体系结构笔记------MIPS流水线的简单实现

体系结构笔记------MIPS流水线的简单实现

- MIPS指令集

- I类指令

- R类指令

- J类指令

- 简单的数据通路

- 时钟周期划分

- 数据存储

- 指令的数据通路分析

- R类指令的举例

- I类指令的举例

- ADDI

- LW与SW

- 控制流指令的单周期数据通路

- 无条件跳转

- 条件分支指令

- 控制逻辑

- 单周期数据通路的局限

- 流水线中的数据通路

MIPS指令集

MIPS指令集是RISC精简指令集,拥有RISC的特点,首先其中的所有的指令位数都是32位的,在这32位中有6为用于编码操作种类,所以我们很容易就了解到,它最多有2的6次方条指令(0 ~ 63)共64条。之后的26位根据划分的不同分为I类,R类和J类。其中所有的寄存器引索都是以5为来编码(0 ~ 31其中0号比较特别,它始终是数字0)。

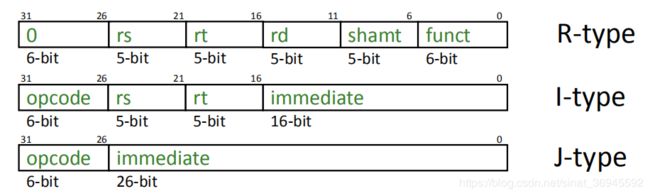

I类指令

指令格式如下:

其中包含了两个寄存器与一个16位的立即数。

常用的使用格式是rs寄存器与立即数操作,结果写到rt寄存器中。

还有一些指令只用到了rs,比如有些分支指令和寄存器跳转指令,rt没有用上。

举个例子,load与store指令是I类的指令,load操作是rs+立即数作为地址将取出的数放到rt中,store操作是rs+立即数作为地址将rt中的数存进去。

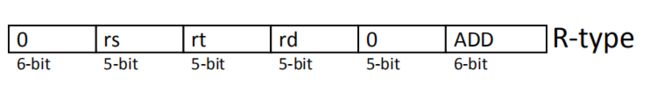

R类指令

这个图有点问题,最左边的是6位的操作码,之后是三个寄存器rs,rt,rd,之后的5位是位移量,最后的六位是具体的操作运算编码。

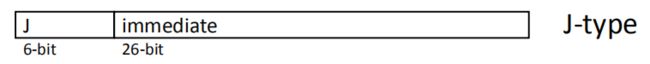

J类指令

这类指令比较简单,就是有操作码和26位的偏移量组成,偏移量和pc相加形成要跳转的地址。

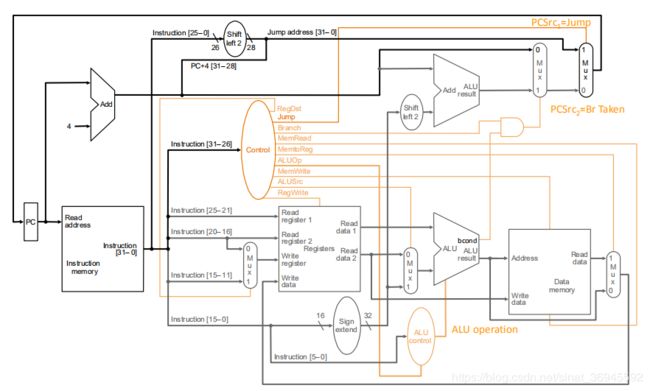

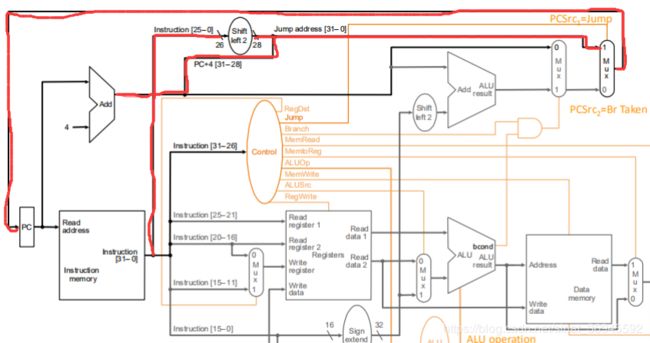

简单的数据通路

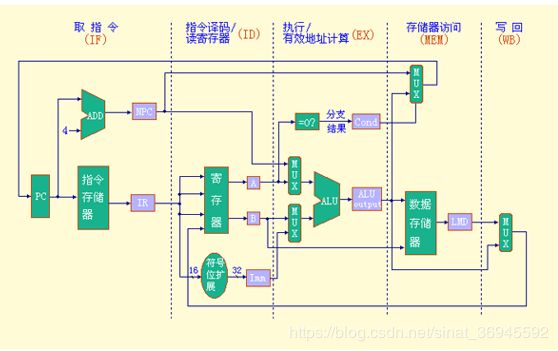

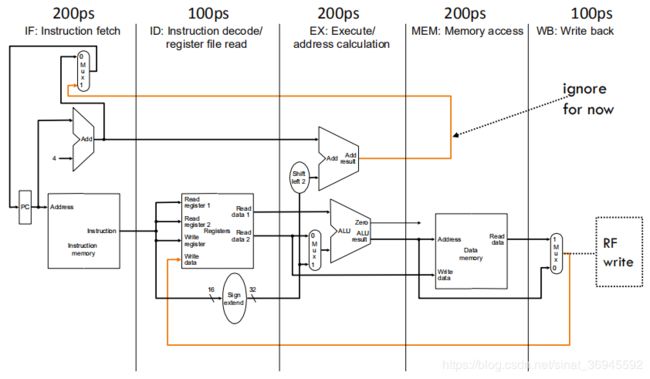

这个数据通路的操作分成5个时钟周期,每个时钟周期有相应的操作:取指令,指令译码/读寄存器,执行/有效地址计算,存储器访问/分支完成,写回。

时钟周期划分

一条MIPS指令最多需要以下5个时钟周期

取指令周期(IF):

IR←Mem[PC](将PC的指令取出放入指令寄存器表示当前运行的指令)

NPC←PC+4(PC指向下一条指令(32位加4))

指令译码/读寄存器周期(ID):

A ← Regs[rs](从源寄存器中读操作数)

B ← Regs[rt](从源寄存器中读操作数)

Imm ← ( ( I R 16 ) 16 # # I R 16..31 ) ((IR_{16})^{16} \#\# IR_{16..31}) ((IR16)16##IR16..31)(根据指令中立即数的位置也就是IR中存放的指令后16位为立即数)

由于在MIPS指令格式中,操作码字段以及rs、rt字段都是在固定的位置。所以在指令译码与读数时操作是并行进行的,称为固定字段译码技术。

根据指令的格式高位的操作码由control来选取,并将选取的结果传到了MUX的选通器中来确定传入的格式是由几个寄存器构成。所以该结构的设计使读数与译码并行执行。

执行/有效地址计算周期(EX):

不同指令所进行的操作不同;

存储器访问指令 :ALU←A + Imm(操作数加上寄存器内容作为访问的目标地址)

寄存器-寄存器:ALU←A func B

寄存器-立即值ALU指令 :ALU←A op Imm

分支指令:ALU←NPC+(Imm<<2); cond←(A = = 0)

将有效地址计算周期和执行周期合并为一个时钟周期,这是因为MIPS指令集采用load/store结构,没有任何指令需要同时进行数据有效地址的计算、转移目标地址的计算和对数据进行运算。

存储器访问/分支完成周期(MEM):所有指令都要在该周期对PC进行更新。除了分支指令,其他指令的PC的值不变。

在该周期内处理的MIPS指令仅仅有load、store和分支三种指令。

存储器访问指令:LMD←Mem[ALU] (将ALU中计算出的地址内容读出)

Mem[ALU]←B(或者写入)

分支指令:if (cond) PC ←ALU else PC←NPC(这个NPC是计算后的PC也就是分支的地址如上图,cond是上面计算的判断条件)

写回周期(WB):不同的指令在写回周期完成的工作也不一样。

寄存器-寄存器ALU指令:Reg[rd]← ALU

寄存器-立即数ALU指令:Reg[rt]← ALU

load指令:Reg[rt]← LMD

数据存储

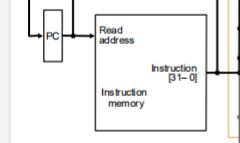

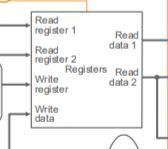

在上面的硬件图中关于数据存储的有三个部分,一个是读指令时的指令存储器。

还有就是在第四阶段数据访存时的数据存储器。

还有就是中间的寄存器组了。

可以看出在这一指令流水中数据与指令分开存放到两个寄存器中,但是其不是哈佛结构仍是冯诺伊曼结构,对于两者的区别是对程序与数据地址空间连续与存放的实际物理位置无关。所以仍旧是冯诺伊曼结构。

这样处理的好处是在流水线运作时,不会产生一个周期里既对指令访存又对数据的访存的访存冲突。

指令的数据通路分析

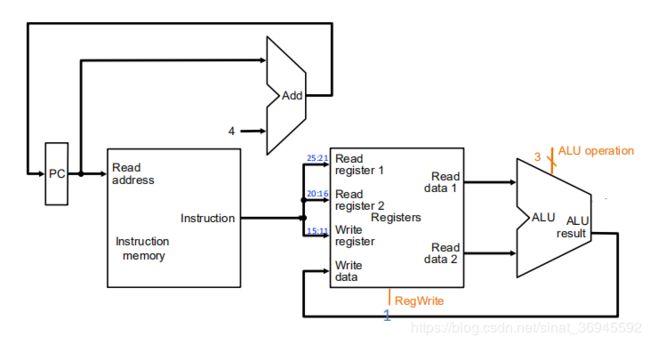

R类指令的举例

add rd rs rt 其中rd是目的寄存器在指令中是[15:11],rt与rs是源寄存器在指令中是[20:16]和[25:21]。

数据通路有:

PC取指后由ALU加一返回,数据运算完后由一条回路返回writeData写入寄存器组中。

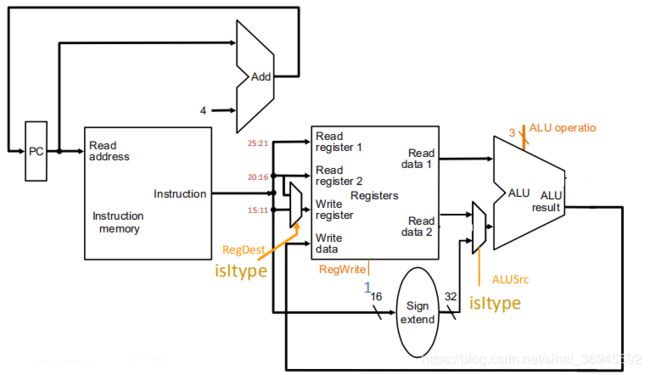

I类指令的举例

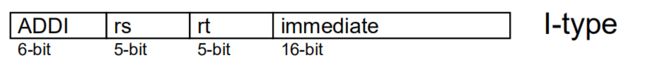

ADDI

addi rt rs imm这里的imm为十六位立即数addi是整数的加法。

其中rt是目的寄存器在指令中是[20:16],rs是源寄存器在指令中是[25:21],立即数在[0:15]位。

这里的istype是指令译码时由上面的control返回下来的,传入的是指令的高六位。

其返回的RegDest作为选通信号,阻断了对[15:11]的传输,将末十六位传到了sign extend位扩展器将16位变成32位(带符号)。ALUSrc传下来选通立即数对ALU的输入,结果完成后返回writeData写回。

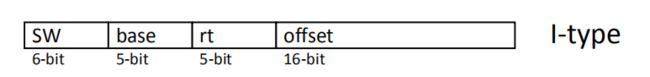

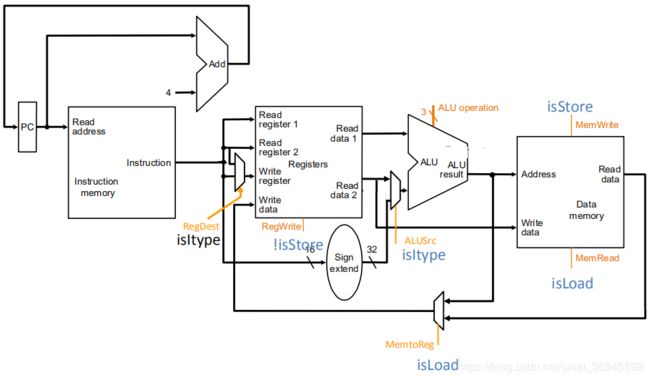

LW与SW

LW rt offset (base)可选

SW rt offset (base)可选

两者的数据通路如下。

对于istype同上面一样,选通信号截断[11:15]的数据,read1是base若没有就默认为0,read2是传入的rt[16:20],经由ALU计算出imm立即数与read1的base的相加结果得到目的地址,输入到Address中,如果是LW就是isLoad=1,isStore=0,将数据读出写回到寄存器组,如果是SW,isLoad=0,isStore=1,就将read2处通到数据内存中的writeData写到相应的内存单元中。

结合上面Addi的数据通路有以下的硬件图(不含控制指令)

控制流指令的单周期数据通路

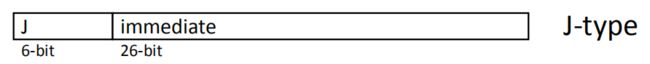

无条件跳转

J imm(这里的立即数是26位的)

如红线标注的部分指令,指令的[0:25]位取出之后左移两位,之后取出PC的高4位合并为32位传回PC(选通信号由control发出)

concat为位连接的部件。

条件分支指令

BEQ RS RT IMM(16位立即数)

目标地址是PC+4后加上32位的imm,并将在rs与rt相等时跳转,否则就继续PC加4运行。

这个数据通路如上图,按执行的顺序来,首先[0:15]位的立即数含符号扩展至32位左移2位,之后与加4之后的PC进行加法运算,同时加4后的PC也准备好了一起进入选通器(红色部分),r传入的两个寄存器进行逻辑运算产生的cond与control的分支信号进行与运算(通过与门)作为选通信号来决定是PC加4作为下一条指令地址还是分支地址(绿色),最终通过一个选通器(用于分别Jmp指令)传回PC(蓝色)。

控制逻辑

除了上面所述的Control之外(control就是用于译码指令高位运算类型来确定指令类型并生产相应的控制信号)

还有一个ALUControl,用于控制ALU的具体运算类型。其中有一个部分取的是指令的[0:5]位是指对R类指令后6位定义的运算类型与control的ALUOp一起决定ALU的运算类型。

单周期数据通路的局限

对于大多数CPU来说,单周期实现效率很低,因为不同的指令所需完成的操作差别相当大,因而所需要的时钟周期时间也大不一样。

单周期实现时,需要重复设置某些功能部件,而在多周期实现方案中,这些部件是可以共享的。

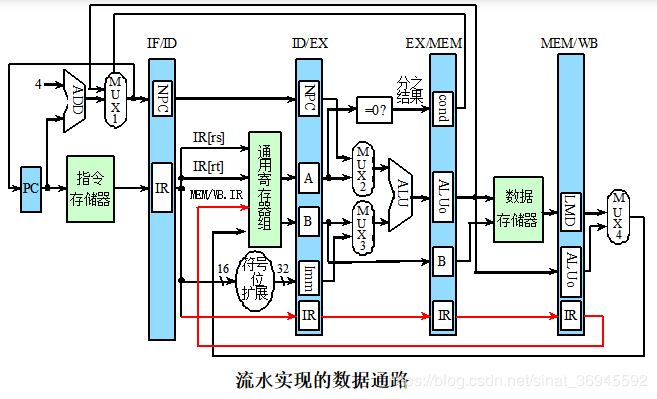

流水线中的数据通路

首先将指令的执行根据阶段划分有:

由于在流水线的操作中多个指令并行执行,我们在每段之间建立寄存器组(流水线寄存器)

流水寄存器的命名:用其相邻的两个段的名称拼合而成。

例如:ID段与EX段之间的流水寄存器用ID/EX表示

每个流水寄存器是由若干个寄存器构成的

流水寄存器的作用:将各段的工作隔开,使得它们不会互相干扰。保存相应段的处理结果。