Xilinx 7 Series FPGA I/O引脚分配设计原则 —— 杂记

前言

一个合理的IO分配方案可保证系统从一开始就获得优良的速度性能、稳定性、热性能和功耗,并缩短整个系统的优化周期。

Xilinx强烈建议用户在设计PCB阶段就开始着手一个更合理的IO分配方案的设计,而不是随机设计。

这个过程包含了IO Planing和Clock Planning两大部分。

PCB布局建议

首先应该通过绘制草图来确定器件的方向。

对于高速接口(如存储器接口),应保证尽可能短的连线,因此选用器件最外围的引脚作为高速信号接口是比较合适的方案。

PCB设计建议

建议使用Vivado提供的工具来验证IO分配方案:

> 运行“同时切换噪声分析(Simultaneous Switching Noise, SSN)”;

> 运行“设计规则检查(DRCs)”;

> 导出IBIS模型。

进行信号完整性分析:

> 对于GT,要用Spice或IBIS-AMI仿真;

> 对于普通设计,需要运行IBIS仿真以检查信号过冲情况。

使用XPE工具对设计进行能耗预测。并将仿真导出的XDC(Xilinx Design Constrain)文件插入到用户设计的项目XDC中,以此作为用户项目的“功耗预算约束”。

分配时钟资源

Xilinx建议,在进行IO引脚分配之前先完成时钟资源的选择。

因为时钟资源的配置(选择)预示了某些IO引脚的分配规则和一些用户逻辑的布局规则。

正确的时钟设计可获得优异的结果。

时钟设计包括:

> 创建约束;

> 时钟资源的手动布局;

> 利用特定器件提供的特殊功能,可能需要预先计划以避免问题并充分利用不同器件的特性。

可参考《7 Series FPGAs Clocking Resources User Guide》。

IO分配方案设计流程

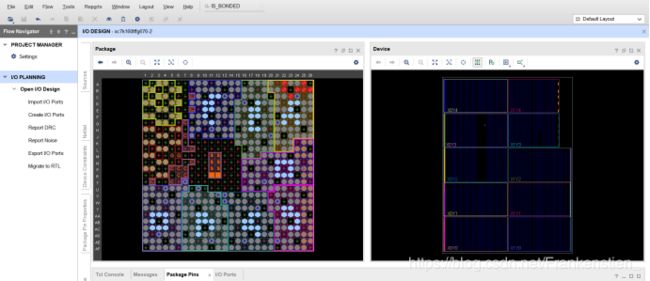

用户可以使用Vivado的IO Planning工具在设计工作流的任何阶段进行IO分配(重分配),该工具使用户得以在可视化的封装和器件核心上完成非常方便快速的IO分配工作(若用户提供了完整的已综合网表,该工具还可以实现用户功能模块IP核模块的交互式可视化布局。

Xilinx非常建议用户先完成RTL设计,甚至是完成综合获得网表,而后再进行IO分配方案的设计。

如此一来可以获得完整的DRC检测,实现最高的开发效率。

但是在实际的项目开发过程中,通常在设计PCB的阶段就需要确定FPGA的IO分配方案。

虽然Vivado软件也提供了相应的Pre-RTL IO Planning功能,但是其中的DRC检查将会变得非常的基础(基本的IO Bank DRC规则),具体包括:

> 阻止将高速收发器GTs的引脚赋值给噪声敏感的引脚;

> 避免I/O标准违反设计规则;

> 确保I/O标准不会用于不支持它们的I/O Bank;

> 确保Bank没有不兼容的Vcc端口赋值;

> 确保需要Vref端口的Bank有可自由使用的Vref引脚;

> 确保全局时钟和局部时钟有合适的赋值;

> 确保差分I/O端口设置在合适的引脚上;

> 确保输出引脚不会布局在仅支持输入的引脚上。

然而,仅使用这些规则进行检查,在后续的设计中,可能会出现问题。

因此,在进行Pre-RTL IO Planning时Xilinx希望用户可以创建一个系统框架级别的“伪RTL设计(dummy RTL)”,该设计应包含应用所需的时钟模块和一些基本逻辑,使得Vivado可以在该阶段进行更多的DRC检查,以避免在设计工作流的后期出现DRC冲突问题;

若条件允许,该“伪RTL设计”最好还包括系统内的各个基本功能模块,及其端口的信号方向(Input/Output),如此一来在进行SSN分析的时候就能获得更准确的结果。

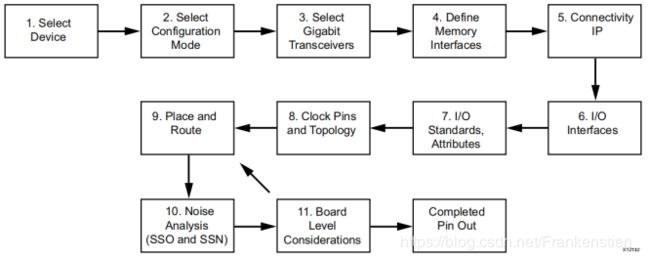

Xilinx推荐的I/O引脚分配工作步骤如图所示:

(1)选择FPGA器件

考虑器件的资源需求,结合PCB上关键路径的位置考虑器件封装的选择。

(2)选择器件的配置模式

不同的配置模式对应了不同的配置引脚,某些配置需要用到一定数量的用户IO,串行配置模式占用少,并行配置模型占用多。而在配置完成后这些用户IO可以被用于其他功能。但是在配置过程中,必须保证这些IO不受用户其他应用的信号的干扰。

(3)选择吉比特收发器(GT)引脚

GTs通常有其专用引脚,并通常与其他GTs或IO时钟域共用时钟输入引脚(CCIO)。

此外,Xilinx列出了在各个FPGA家族中一系列不建议使用的位于GTs附近的IO引脚,不恰当地使用了这些引脚将会对GTs的信号完整性造成影响。

用户可以用Clock Resources视图和Device视图来放置GTs,还需要避免某些些硬核IP会阻碍GT ( ? )。

(4)定义外部存储器接口引脚

取决于对时钟频率和延迟(偏移),高速存储器接口(如DDR2、DDR3等)对IO引脚的选择有着特定的需求。

用户可以通过Memory Interface Generator(MIG)工具来配置相应的IO引脚约束,并将这些约束添加到最终的UCF文件中。

(5)定义IP接口引脚

某些IP核(如Ethernet以及PCIe)有特定的IO引脚需求,使用CORE generator工具可以创建各类IP核并自动分配引脚。

(6)定义普通用户功能IO引脚

可以使用IO Planning视图或项目进行可视化的用户IO引脚配置。

(7)定义IO电平标准和属性

用户可选择自动IO分配功能实现自动IO分配。

需要注意“差分IO对”的存在。

可运行设计规则检查(Design Rule Check, DRC),以检查IO电平标准与IO所在的Bank属性是否冲突。

有些IO电平标准可以在一个Bank中组合使用,有些则不能。

(8)定义时钟引脚与时钟拓扑结构

使用FPGA器件上提供的专用时钟输入引脚可获得最佳的时序性能。

使用比全局时钟资源数量更少的时钟的设计通常更简单。

对于更复杂的时钟拓扑结构,用户需要输入时钟树和足够的时钟负载,以便通过布局和布线来运行早期设计并验证其功能。

复杂的时钟拓扑结构包括高速时钟计数器的设计,需要自动或手动规划资源布局来使用区域时钟资源。

(9)布局和布线设计

至此,大部分主要结构(I/O、IP和时钟)都应该定义好了。

定义的和可用的上述主要结构越多,运行DRC的结果就越精确。

该阶段需要执行以下步骤:

> 锁定所有的IO引脚;

> 在布局和布线以前运行一次DRC;

> 运行布局和布线来验证当前的引脚配置方案;

(注意,当前阶段并不需要定义完整的用户逻辑,而只需要确定和IO有关的主要结构。)

> 对当前设计进行完全布局(Implementation)来验证IO引脚是否合法;

> 检查 ngdbuild report和map report所列出的与IO、时钟相关的消息。

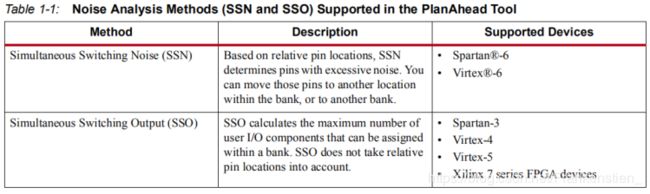

(10)噪声分析(SSN和SSO)

噪声分析的方法有SSN和SSO两种:

SSN(Simultaneously Switching Noise)分析可以估计I/O Bank中管脚在同时转换输出状态时对其它输出端口造成的干扰。这是一个常见的问题,许多总线有大量的位宽,当总线数据有多位同时变化时,很容易在其它I/O上产生噪声。比如数字电路设计中倾向于使用格雷码编码,正是因为两个相邻的数字用格雷码表示时只有1bit的差异,使得同时转换噪声最小。

SSN分析会将I/O Bank的规格电气特性考虑在估算中,以获得更准确的模型封装对SSN的影响。我们知道FPGA中将I/O隔离地分布在多个I/O Bank中,每个I/O Bank都有独立的电源分布和独立的同时转换响应。并且,不同的电源分布网络对噪声有不同的响应,因此设计者需要理解不同I/O标准、设计中用到的I/O数量、FPGA电源系统对转换响应的影响。

Xilinx通过三维提取和仿真刻画了所有Bank的特征,这些信息会用于SSN分析中,预测转换对系统电源网络和I/O Bank中其它输出管脚的影响。SSN分析仅分析输出信号和双向端口的输出状态,计算中会忽略输入信号。SSN分析可以帮助设计者发现设计中潜在的噪声问题。

当出现过大的噪声干扰时,需要优化设计:

> 使用低噪声冲击的IO电平标准;

> 降低驱动强度;

> 使用并行端接DCI标准;

> 降低驱动器的级别(如:Changing the SSTL Class II to an SSTL Class I);

> 重新定义引脚位置,远离噪声源;

> 将下降沿引脚分散到不同的IO Bank内从而降低单个Bank电源的突变噪声;

> 将下降沿组分散到多个同步相位上。

优化设计后:

> 重新进行第9步:布局和布线设计

> 重新进行第10步:噪声分析(SSN和SSO)

(11)板级考虑

需要通过专业仿真软件,利用特定FPGA器件的IBIS(Input/Output Buffer Informational Specification)或HSPICE模型进行信号完整性仿真分析。

可将FPGA器件的引脚布局导入到第三方PCB分析设计软件以设计出更好的引脚分配方案。

优化设计后:

> 重新进行第9步:布局和布线设计

> 重新进行第10步:噪声分析(SSN和SSO)

引脚选择原则 ***

Xilinx建议用户对以下应用进行尤为谨慎的引脚选择!

配置引脚

不同的配置模式对应了不同的配置引脚,某些配置需要用到一定数量的用户IO,串行配置模式占用少,并行配置模型占用多。

在配置完成后这些用户IO可以被用于其他功能。但是在配置过程中,必须保证这些IO不受用户其他应用的信号的干扰。若IO引脚数量充足,最好还是不要复用这些配置用IO引脚。

可在器件的配置模式下设置某些IO bank的电压限制。

为不同的配置引脚选用合理终端类型(使用推荐的引脚上/下拉电阻)。

详情可参考《Vivado Design Suite User Guide: Programming and Debugging》手册。

吉比特收发器引脚

GT有特定的引脚需求,用户使用GT时必须考虑以下情况:

> 共享时钟;

> 共享同Quad内的PLL;

> 其他硬IP核的布置(如PCIe硬核)以及他们与GT的距离;

> 在SSI器件中还需要考虑是否跨越了SLR。

Xilinx建议用户使用GT wizard来创建GT IP核。

为了平衡时钟资源,Vivado的布局器(Placer)将尝试约束由GT输出时钟所驱动的负载的数量(?)。

存储器接口引脚

在分配多个存储器接口引脚组的时候应尽量使其分开。若将多个存储器接口的引脚聚在一起,则会造成整个器件内部的布线瓶颈。并确保存储器接口的布线长度控制在用户手册的建议长度范围内。

用Vivado调用存储器接口IP核后,与其相关的所有IO引脚会被集成为一个“I/O Port Interface”,以便于用户统一配置。Vivado提供了一个“Memory Bank/Byte Planner”来协助用户将存储器接口IO引脚的分配到物理器件的“字节通道(Byte Lane)”上。

详情可参考《The Zynq-7000 SoC and 7 series Devices Memory Interface Solutions》手册。

接口的数据引脚、地址引脚、控制引脚

将同一个接口的数据、地址和控制引脚都集中放置在同一个IO Bank内。若实在无法实现,也要尽量放置在相邻的Bank内。

此外,最好利用IO Planning工具在可视化的器件内核结构图上,按照IOB的排列顺序依次分配总线引脚,这样可在Implementation阶段获得尽可能短的布线路径,并节约布线资源(有待验证)。

接口的控制引脚

将这些引脚放置在它们控制的数据总线的中间位置:时钟引脚、使能引脚、复位引脚、选通引脚等。

扇出非常高、覆盖全设计域的控制信号引脚

将此类引脚放置在整个器件的中间位置。

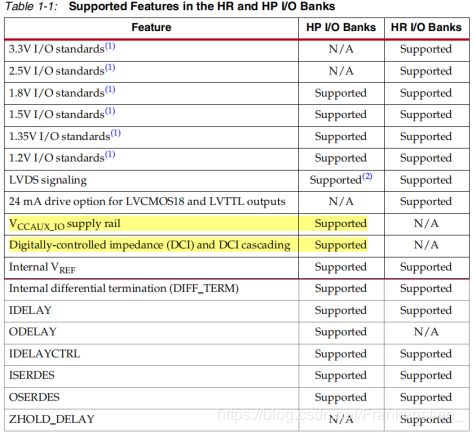

高速IO引脚

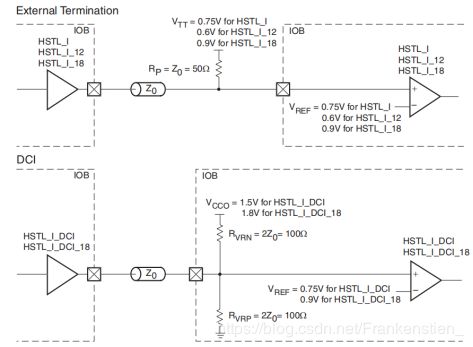

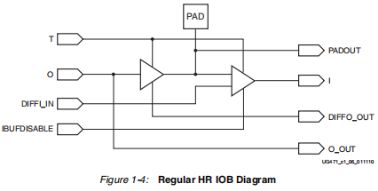

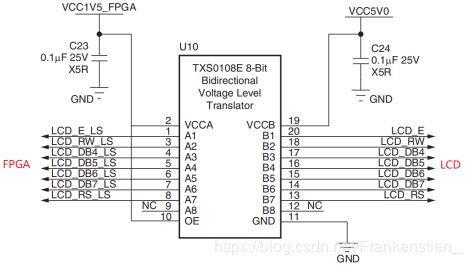

HP_IO Bank与HR_IO Bank的所支持的电压和速度都不同,HP_IO支持的读写速度高达1866Mb/s,而HR_IO支持的最高速度则为1066Mb/s。

HP_IO最特别之处在于集成了DCI功能,使得器件可以自动完成高速信号的阻抗匹配,通常用于高速芯片间的通信。

DCI功能省去了用户在此类应用的PCB设计中布置大量片外阻抗匹配电阻的繁琐工作。

实际上,除去DCI功能相关结构和IO电平范围差异后,HP_IO和HR_IO的IOB结构基本相同。

若用户需要更多的IO引脚来驱动低速信号,则可以将HP_IO连接电平转换芯片来拓展其电平范围,即可将其当作普通HR_IO来使用(参考官方KC705开发板的设计)。

有关DCI的详情可参考《7 Series FPGAs SelectIO Resources User Guide》手册。

接口带宽验证

Xilinx建议用户创建“小型连接设计(Small Connectivity Design)”来验证器件上各个硬件接口的设计。(是否就是前文所述的“伪RTL设计”呢?)

仅需描述特定的硬件接口即可,用这个设计可以完成以下验证:

> 针对IO引脚、时钟和时序的完整DRC检查;

> 在PCB板到货后进行硬件测试;

> 得以利用Vivado提供的工具实现快速Implementation,在最短时间内实现接口调试。

Vivado提供的测试用设计有:

> SerDes(串行并行转换器)的IBERT;

> IP核的测试用设计

虽然这个“小型连接设计”在设计工作流的早期并不是必须的,但是它能够让用户获得更全面的DRC检查以及更早进入软件设计的阶段。

用户可以利用Vivado IP Integrator来快速创建“小型连接设计”。

电源分配系统(Power Distribution System, PDS)设计建议

FPGA的应用场合及其丰富多样,器件的工作频率范围和电压范围很大(相比于普通MCU、MPU、CPU、GPU等集成电路),且可以布局在不同的时钟域之间。

因此,PDS的设计非常的关键,建议细读《PCB Design Guide》手册,详细了解对PDS设计的建议。

器件上的供电路径

器件上各个电源的上电过程存在严格的顺序要求,建议用户采用供电监控器或时序电路来保证。

对于更复杂的系统,则可以借助其MCU芯片来保证FPGA芯片的上电和复位过程。

详细的上电/掉电过程可在器件的Data Sheet中找到。

此外,电源引脚上去耦电容的选择很重要,必要时要进行电源分配网络仿真分析(推荐使用第三方软件:SIMPLIS仿真器),请重点参考《PCB Design Guide》手册。

供电模式

从上电、运行到掉电,一个器件需要经历一下几个供电阶段(Power Phase),在不同阶段存在不同的供电需求。

> 上电阶段

在上电瞬间会迎来一个暂态电流冲击,只要遵循推荐的上电过程,这个冲击就不是什么大问题。

> 启动供电阶段

启动供电指的是器件在初始化和配置的过程中需要满足的供电。通常持续很短时间,不需要为该阶段设计专门的散热措施。而对于低功耗器件,该阶段的电流会明显高于器件正常运行时的电流,在设计其电源电路时必须考虑到这一点。Vivado提供了XPE工具来预测器件的最大电流阶段,并预测其电流大小,可供用户设计电源方案。

> 就绪供电阶段

就绪供电也称为“设计静态功耗”,是在器件配置完成而未被激活状态下的功耗。代表了器件的最低功耗。

> 激活供电阶段

激活供电也称为“设计动态功耗”,是器件在运行用户应用时的功耗,该功耗由“设计静态功耗”和“用户应用运行所导致的脉冲功耗”构成。

配置电路的设计建议

无论如何都最好预留JTAG调试接口。

INIT_B和DONE引脚上的信号在配置调试过程中非常重要,INIT_B指示:

> 器件上电后是否完成了初始化;

> 配置比特流是否发生了CRC(循环冗余校验)错误。

建议将INIT_B和DONE引脚接LED并配置成上拉输出。

参考资料:

《Pin Planning Methodology》

《UltraFast Design Methodology Guide for the Vivado Design Suite_Board and Device Planning》

《7-Series FPGAs SelectIO Resources》

《KC705 Evaluation Board for the Kintex-7 FPGA》

http://xilinx.eetrend.com/content/2018/100014411.html —— 《Vivado使用技巧(16)——SSN转换噪声分析》

https://www.xilinx.com/content/xilinx/en/video/hardware/i-and-o-planning-overview.html