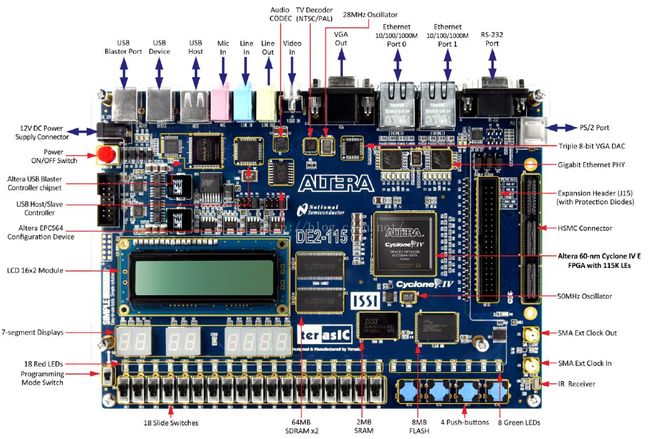

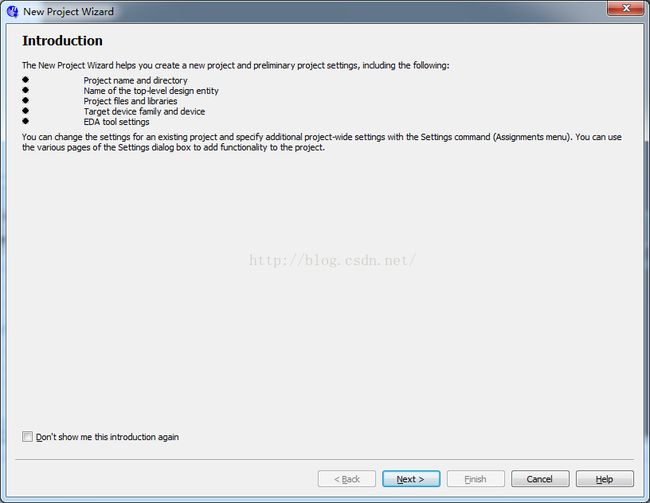

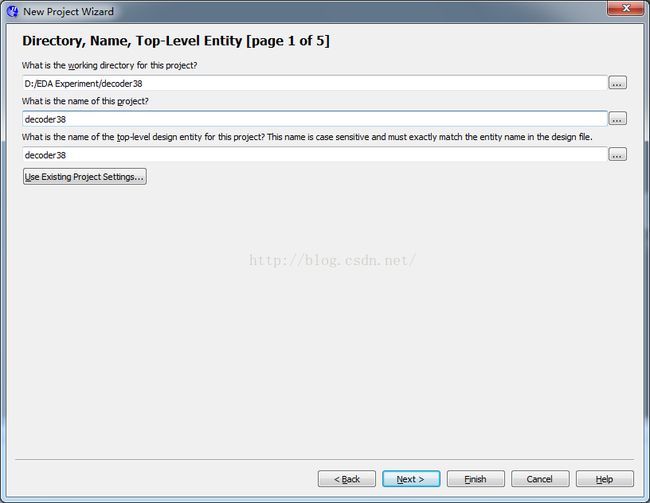

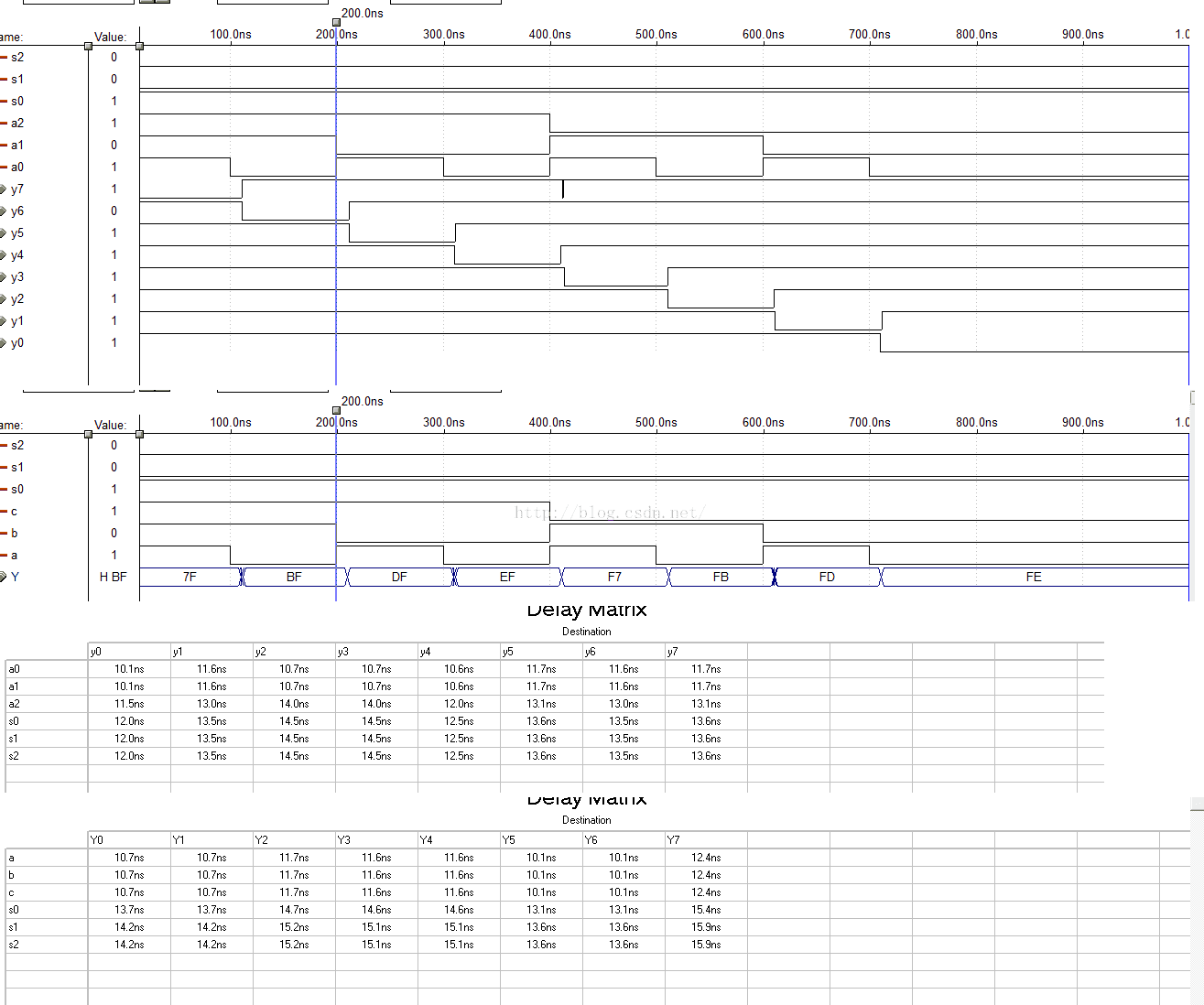

- quartus频率计 时钟设置_FPGA021 基于QuartusⅡ数字频率计的设计与仿真

weixin_39876739

quartus频率计时钟设置

摘要随着科技电子领域的发展,可编程逻辑器件,例如CPLD和FPGA的在设计中得到了广泛的应用和普及,FPGA/CPLD的发展使数字设计更加的灵活。这些芯片可以通过软件编程的方式对内部结构进行重构,使它达到相应的功能。这种设计思想改变了传统的数字系统设计理念,促进了EDA技术的迅速发展。数字频率计是一种基本的测量仪器。它被广泛应用与航天、电子、测控等领域。采用等精度频率测量方法具有测量精度保持恒定,

- 2020-11-12 写单片机内存的脚本 nc openocd 事务自动测试

linuxScripter

这是写单片机内存的脚本:z@z-ThinkPad-T400:~/zworkT400/EDA_heiche/zREPOgit/simple-gcc-stm32-project$catz.wholeRun.oneCase.cmdcattmp6.toWrite|awk'{system("echomwb"$1""$2"|nclocalhost4444");}'catUSER/DEBUG/debug.h|g

- VLSI电路单元的自动布局:全局布局基础介绍

Jaaiko

数学建模算法开源图论matlab

2024年华数杯全国大学生数学建模竞赛B题为:VLSI电路单元的自动布局。本题主要关注的是全局布局问题。学术界针对全局布局的评估模型和优化方法的研究历史悠久。本文借题顺势介绍全局布局的一些重点基础内容和相关工具/资料,以期为对EDA算法设计领域感兴趣、对数学建模感兴趣的人降低研究门槛。VLSI是超大规模集成电路的简称。完成一个VLSI设计的流程十分复杂,包含多种数据格式的转化,其中将逻辑网表转变为

- VLSI 电路单元的自动布局-2024华数杯B题

2401_84314384

算法python数学建模

摘要超大规模集成电路设计通常采用电子设计自动化(EDA)的方式进行,布局是EDA工具的核心的核心。本文通过构建的线长评估模型及网格密度评估模型,并在此基础上对模型进行优化,最后利用模型实现VLSI电路单元的自动布局。问题一:基于结合直线型斯坦纳最小树思想的优化HPWL模型评估与电路单元连线接口坐标相关的线长。本题需要建立与电路单元连线接口坐标相关的线长评估模型,最小化每组估计线长与对应RSMT的差

- 事件驱动的架构及应用

treewinder

EDAsoa分布式应用电子政务processing企业应用jms

事件驱动的架构及应用来源:软件世界作者:李臣亮Gartner在2003年引入了一个新术语事件驱动架构(EventDrivenArchitecture,EDA),主要用于描述一种基于事件的范例。EDA是一种用于进行设计和实现应用和系统的方法—在这些应用和系统里,事件所触发的消息可以在独立的、非耦合的组件和服务之间传递,这些模块彼此并不知晓对方。这些应用程序中的EDA极大地改进了企业或政府响应不同的、

- 探索未来编程新纪元:flow-eda——可视化低代码的创新实践

史锋燃Gardner

探索未来编程新纪元:flow-eda——可视化低代码的创新实践flow-eda采用springboot+vue/react搭建的一个基于事件驱动的流式低代码编程应用程序,您可以在编辑器中采用拖拽的形式来实现业务编程工作,一键运行和停止,让开发工作变得更简单高效。项目地址:https://gitcode.com/gh_mirrors/fl/flow-eda项目介绍在软件开发领域,flow-eda正迅

- 第R3周:天气预测

Jessica2017lj

python

本文为[365天深度学习训练营]中的学习记录博客参考文章:第R3周:LSTM-火灾温度预测(训练营内部可读)作者:[K同学啊]任务说明:该数据集提供了来自澳大利亚许多地点的大约10年的每日天气观测数据。你需要做的是根据这些数据对RainTomorrow进行一个预测,这次任务任务与以往的不同,我增加了探索式数据分析(EDA),希望这部分内容可以帮助到大家。我的环境:●语言环境:Python3.8●编

- 2020-03-24

黑乎乎AI

Datawhale零基础入门数据挖掘-Task2数据分析【代码摘要】赛题:零基础入门数据挖掘-二手车交易价格预测地址:[https://tianchi.aliyun.com/competition/entrance/231784/introduction?spm=5176.12281957.1004.1.38b02448ausjSX]EDA的价值主要在于熟悉数据集,了解数据集,对数据集进行验证来确

- 数据科学生命周期的7个步骤–在业务中应用AI

听忆.

人工智能

数据科学生命周期的7个步骤–在业务中应用AI1.问题定义(BusinessUnderstanding)2.数据收集(DataCollection)3.数据准备(DataPreparation)4.数据探索(ExploratoryDataAnalysis,EDA)5.模型构建(Modeling)6.模型评估(Evaluation)7.模型部署与维护(DeploymentandMaintenance)

- 保持异步同步:SmartBear利用事件驱动架构

慧都小妮子

架构java微服务

开发团队需要保持竞争力,API从业者正在使用各种协议来完成工作。总是有新出现的方法、协议和框架来满足业务需求。我们的软件质量状况|2023年API工具和趋势报告发现,不仅微服务在增加,我们还看到支持事件和消息传递的API也在增加。此外,我们看到各种协议都在使用——例如REST和AsyncAPI等等。为了理解事件和消息传递的兴起,我们必须更深入地了解事件驱动架构(EDA),了解这种架构范式如何与微服

- rf 's book

gtkknd

rf

微波射频工程师必读经典参考书更新于2013-08-0521:14:42文章出处:互联网微波射频工程师参考书EDA仿真设计《ADS应用详解--射频电路设计与仿真》『中』陈艳华、李朝晖、夏玮编著人民邮电出版社图书简介:本书介绍使用ADS进行射频电路设计和仿真的基础知识和方法。网友书评1:这本书50刀,不值得。作者估计不是射频专业人士,纯粹抄袭网上的那个9个经典实例,而且还有删减,加多了一个功分器,VC

- (135)vivado综合选项--->(35)Vivado综合策略三五

FPGA系统设计指南针

数字IC系统设计(提升笔记)单片机嵌入式硬件FPGA综合

1目录(a)IC简介(b)数字IC设计流程(c)Verilog简介(d)Vivado综合策略三五(e)结束1IC简介(a)在IC设计中,设计师使用电路设计工具(如EDA软件)来设计和模拟各种电路,例如逻辑电路、模拟电路、数字信号处理电路等。然后,根据设计电路的规格要求,进行布局设计和布线,确定各个电路元件的位置和连线方式。最后,进行物理设计,考虑电磁兼容性、功耗优化、时序等问题,并生成芯片制造所需

- (134)vivado综合选项--->(34)Vivado综合策略三四

FPGA系统设计指南针

数字IC系统设计(提升笔记)单片机嵌入式硬件FPGA综合

1目录(a)IC简介(b)数字IC设计流程(c)Verilog简介(d)Vivado综合策略三四(e)结束1IC简介(a)在IC设计中,设计师使用电路设计工具(如EDA软件)来设计和模拟各种电路,例如逻辑电路、模拟电路、数字信号处理电路等。然后,根据设计电路的规格要求,进行布局设计和布线,确定各个电路元件的位置和连线方式。最后,进行物理设计,考虑电磁兼容性、功耗优化、时序等问题,并生成芯片制造所需

- 【EDA概述】

Winner1300

EDAfpga开发

文章目录前言一、EAD技术的发展二、FPGA和CPLD有什么区别三、FPGA应用?四、FPGA技术开发与单片机技术开发发展前景五、FPGA技术开发和单片机技术开发各自的薪资水平如何六、如何学习FPGA总结前言提示:这里可以添加本文要记录的大概内容:EDA技术提示:以下是本篇文章正文内容,下面案例可供参考一、EAD技术的发展EDA技术的发展主要经历了以下四个阶段:雏形时期:20世纪60年代中期到70

- 事件驱动架构

可爱的小小小狼

架构架构

事件驱动模型是基于观察者模式或者发布订阅模式实现的。核心概念事件驱动架构(Event-DrivenArchitecture,EDA)是一种基于事件和异步通信的架构模式。其核心概念包括以下几个方面:事件(Event):事件是系统中发生的事情或状态变化的表示。它可以是用户操作、传感器数据、消息等。事件通常包含有关事件发生的上下文信息。事件发布者(EventPublisher)事件订阅者(EventSu

- 零基础入门金融风控-贷款违约预测Task2 数据分析

一缕阳光lyz

数据分析数据挖掘

Task2数据分析此部分为零基础入门金融风控的Task2数据分析部分,带你来了解数据,熟悉数据,为后续的特征工程做准备,欢迎大家后续多多交流。赛题:零基础入门数据挖掘-零基础入门金融风控之贷款违约目的:1.EDA价值主要在于熟悉了解整个数据集的基本情况(缺失值,异常值),对数据集进行验证是否可以进行接下来的机器学习或者深度学习建模.2.了解变量间的相互关系、变量与预测值之间的存在关系。3.为特征工

- 【机器学习笔记】 15 机器学习项目流程

RIKI_1

机器学习机器学习笔记人工智能

机器学习的一般步骤数据清洗数据清洗是指发现并纠正数据文件中可识别的错误的最后一道程序,包括检查数据一致性,处理无效值和缺失值等。与问卷审核不同,录入后的数据清理一般是由计算机而不是人工完成。探索性数据分析(EDA探索性数据分析(EDA)是一个开放式流程,我们制作绘图并计算统计数据,以便探索我们的数据。目的是找到异常,模式,趋势或关系。这些可能是有趣的(例如,找到两个变量之间的相关性),或者它们可用

- 立创EDA专业版快速使用和一些快捷键

-Harvey

电赛EDA嘉立创PCB

立创EDA专业版介绍原理图PCB快捷键原理图PCB介绍器件=符号+封装+3D模型+属性仅支持放置器件在原理图或PCB一个Board(板)只能有一个原理图和PCB,一个原理图可以有多页原理图网络标签是给连接线命名新建图页如果一个图页上画不下,可以在Schematic上新建图页工程库我们如果将一个器件的封装更换,相关信息会保存到工程库中。下次使用该器件时,会优先选用工程库的器件。设置-分配位号可以自动

- 解读 EventBridge Transform,数据转换和处理的灵活能力

阿里云EventBridge提供了强大而灵活的事件总线服务,它可以连接应用程序、阿里云云服务和阿里云Serverless服务来快速构建EDA(Event-drivenArchitectures)事件驱动架构,驱动应用与应用,应用与云的连接。除此之外,它还可以作为流式的数据管道,在不同的数据仓库和数据处理或分析程序之间快速构建ETL系统。本文将从以下几个方面展开对阿里云EventBridgeTran

- 立创EDA学习:PCB布局

写点什么呢

学习记录学习单片机嵌入式硬件硬件工程pcb工艺

目前进度ESP32最小系统板项目,已完成原理图绘制点击“更新/转换原理图到PCB”点击“应用修改”对应器件的封装就可以对应到PCB中布局传递回到原理图,框选每一个模块,“设计-布局传递”会跳转到PCB界面,可以自己选择放置位置依次选中各个模块,进行布局传递最后是四个螺丝孔先规定一个最大尺寸笔者单位是mil,可以更改为mm嘉立创每个月有两次免费打板机会,尺寸是100mmX100mm以内,布局优先考虑

- 数据分析基础之《pandas(8)—综合案例》

csj50

机器学习数据分析

一、需求1、现在我们有一组从2006年到2016年1000部最流行的电影数据数据来源:https://www.kaggle.com/damianpanek/sunday-eda/data2、问题1想知道这些电影数据中评分的平均分,导演的人数等信息,我们应该怎么获取?3、问题2对于这一组电影数据,如果我们想看Rating、Runtime(Minutes)的分布情况,应该如何呈现数据?4、问题3对于这

- 八段码到8421BCD码转换电路

北国无红豆

FPGAmcu嵌入式硬件

目录EDA设计基础练习题:实验要求如下:代码八段码到8421BCD码转换电路8421BCD码到八段码转换电路八段码到8421BCD~运行结果展示8421BCD转八段码~运行结果展示特别注意EDA设计基础练习题:4、八段码到8421BCD码转换电路(以共阳极数码管为例)。5、8421BCD码到八段码转换电路(以共阴极数码管为例)。实验要求如下:1、程序设计:编写完整实验程序;注明端口名称及意义;2、

- 多物理场仿真技术“博客”和“微博”介绍

多物理场仿真技术

多物理场仿真技术的博客最早开始于2013年,6年多以来从未间断。博客中转载了很多有价值的仿真技术,记录了CAD/CAE/EDA/CFD/HPC/优化等软件研发历程,和仿真相关的研发资料以及软件帮助文档。相比公众号信息更加全面。博客地址:http://blog.sina.com.cn/multiphysics-------------------------主要内容介绍:1.研发的CAD/CAE/C

- 【转】微波射频工程师必读经典参考书

AdelaideLiu

电子常识射频

成为一名优秀的微波射频工程师,除实际工作经验的积累外,理论知识也非常重要。最近微波射频网(MWRF.NET)编辑根据微波社区(Club.mwrf.net)网友推荐,以及当当网、京东、亚马逊等主要网上书店的图书评价中,整理出最受微波射频工程师欢迎的参考书。由于推荐的图书比较多,我们按EDA仿真设计、微波电路/工程、天线、通信、物联网、雷达、电磁兼容进行分类整理。微波射频工程师必读经典参考书EDA仿真

- 微波射频工程师必读经典参考书

qq_23371267

图书微波图书通信技术图书

成为一名优秀的微波射频工程师,除实际工作经验的积累外,理论知识也非常重要。最近微波射频网(MWRF.NET)编辑根据微波社区(Club.mwrf.net)网友推荐,以及当当网、京东、亚马逊等主要网上书店的图书评价中,整理出最受微波射频工程师欢迎的参考书。由于推荐的图书比较多,我们按EDA仿真设计、微波电路/工程、天线、通信、物联网、雷达、电磁兼容进行分类整理。微波射频工程师必读经典参考书EDA仿真

- 基于Robei EDA--实现串口通信

悲喜自渡721

fpga开发

一、串口简介串口作为常用的三大低速总线(UART、SPI、IIC)之一,在设计众多通信接口和调试时占有重要地位。但UART和SPI、IIC不同的是,它是异步通信接口,异步通信中的接收方并不知道数据什么时候会到达,所以双方收发端都要有各自的时钟,在数据传输过程中是不需要时钟的,发送方发送的时间间隔可以不均匀,接受方是在数据的起始位和停止位的帮助下实现信息同步的。而SPI、IIC是同步通信接口(后面的

- LLaMA 2 和 QianWen-14B

wangqiaowq

人工智能深度学习

阿里云通义千问14B模型开源!性能超越Llama2等同等尺寸模型-科技新闻-EDA365电子论坛网LLaMA2的硬件要求:LLaMA2系列模型有不同的参数量版本,如7B、13B和70B等。对于不同大小的模型,其硬件需求也有所不同。以下是一些硬件要求摘要:LLaMA270B推理时全精度(FP32)显存占用最低要求为约280GB。对于微调和推理,Llama-13B建议使用至少10GBVRAM(显存)的

- 数据挖掘——特征工程

run_session

Kagglepython机器学习数据分析

文章目录特征工程3.3.1删除异常值3.3.2特征构造批量处理时间数据1.归一化2.标准化3.3.3特征筛选特征工程在EDA中我们更多的操作是针对数据本身与分析而特征工程是针对数据的进一步处理来最终选择出我们模型中需要的特征3.3.1删除异常值#这里我包装了一个异常值处理的代码,可以随便调用。defoutliers_proc(data,col_name,scale=3):"""用于清洗异常值,默认

- Samtec工程师分享ADS Design Guide Developer Studio | Keysight EDA创新论坛上的思维碰撞

SamtecChina2023

信号信号处理安全

【摘要/前言】"Samtec始终为客户提供卓越的信号完整性支持。有时,我们协助客户通过模拟来评估通道。不同的参数设置会导致不同的模拟结果,为了避免这一情况发生,我们利用ADSDesignGuideDeveloperStudio统一了通道配置。"——Samtec信号完整性专家HenryDai【Samtec共襄技术盛宴】在2023年10月17日于上海张江举行的2023KeysightEDA用户创新论坛

- FPGA_组合逻辑_全加器(层次化设计思想)

哈呀_fpga

fpga开发fpga学习图像处理信号处理系统架构

一理论全加器:2个数据位相加,除了加数与被加数加和之外,还要加上上一级传进来的进位信号。层次化设计思想:自底而上:由基本单元构建高层单元,依次而上,直至构建系统。自上而下:将系统划分为不同层次的基本单元,直到可以用EDA元件库的元件实现为止。功能模块1功能模块1功能模块1二电路开发板:使用fpga开发板上key按键与led灯。使用2个按键表示2个输入数据位,1个按键表示进位信号,2个led分别表述

- 强大的销售团队背后 竟然是大数据分析的身影

蓝儿唯美

数据分析

Mark Roberge是HubSpot的首席财务官,在招聘销售职位时使用了大量数据分析。但是科技并没有挤走直觉。

大家都知道数理学家实际上已经渗透到了各行各业。这些热衷数据的人们通过处理数据理解商业流程的各个方面,以重组弱点,增强优势。

Mark Roberge是美国HubSpot公司的首席财务官,HubSpot公司在构架集客营销现象方面出过一份力——因此他也是一位数理学家。他使用数据分析

- Haproxy+Keepalived高可用双机单活

bylijinnan

负载均衡keepalivedhaproxy高可用

我们的应用MyApp不支持集群,但要求双机单活(两台机器:master和slave):

1.正常情况下,只有master启动MyApp并提供服务

2.当master发生故障时,slave自动启动本机的MyApp,同时虚拟IP漂移至slave,保持对外提供服务的IP和端口不变

F5据说也能满足上面的需求,但F5的通常用法都是双机双活,单活的话还没研究过

服务器资源

10.7

- eclipse编辑器中文乱码问题解决

0624chenhong

eclipse乱码

使用Eclipse编辑文件经常出现中文乱码或者文件中有中文不能保存的问题,Eclipse提供了灵活的设置文件编码格式的选项,我们可以通过设置编码 格式解决乱码问题。在Eclipse可以从几个层面设置编码格式:Workspace、Project、Content Type、File

本文以Eclipse 3.3(英文)为例加以说明:

1. 设置Workspace的编码格式:

Windows-&g

- 基础篇--resources资源

不懂事的小屁孩

android

最近一直在做java开发,偶尔敲点android代码,突然发现有些基础给忘记了,今天用半天时间温顾一下resources的资源。

String.xml 字符串资源 涉及国际化问题

http://www.2cto.com/kf/201302/190394.html

string-array

- 接上篇补上window平台自动上传证书文件的批处理问卷

酷的飞上天空

window

@echo off

: host=服务器证书域名或ip,需要和部署时服务器的域名或ip一致 ou=公司名称, o=公司名称

set host=localhost

set ou=localhost

set o=localhost

set password=123456

set validity=3650

set salias=s

- 企业物联网大潮涌动:如何做好准备?

蓝儿唯美

企业

物联网的可能性也许是无限的。要找出架构师可以做好准备的领域然后利用日益连接的世界。

尽管物联网(IoT)还很新,企业架构师现在也应该为一个连接更加紧密的未来做好计划,而不是跟上闸门被打开后的集成挑战。“问题不在于物联网正在进入哪些领域,而是哪些地方物联网没有在企业推进,” Gartner研究总监Mike Walker说。

Gartner预测到2020年物联网设备安装量将达260亿,这些设备在全

- spring学习——数据库(mybatis持久化框架配置)

a-john

mybatis

Spring提供了一组数据访问框架,集成了多种数据访问技术。无论是JDBC,iBATIS(mybatis)还是Hibernate,Spring都能够帮助消除持久化代码中单调枯燥的数据访问逻辑。可以依赖Spring来处理底层的数据访问。

mybatis是一种Spring持久化框架,要使用mybatis,就要做好相应的配置:

1,配置数据源。有很多数据源可以选择,如:DBCP,JDBC,aliba

- Java静态代理、动态代理实例

aijuans

Java静态代理

采用Java代理模式,代理类通过调用委托类对象的方法,来提供特定的服务。委托类需要实现一个业务接口,代理类返回委托类的实例接口对象。

按照代理类的创建时期,可以分为:静态代理和动态代理。

所谓静态代理: 指程序员创建好代理类,编译时直接生成代理类的字节码文件。

所谓动态代理: 在程序运行时,通过反射机制动态生成代理类。

一、静态代理类实例:

1、Serivce.ja

- Struts1与Struts2的12点区别

asia007

Struts1与Struts2

1) 在Action实现类方面的对比:Struts 1要求Action类继承一个抽象基类;Struts 1的一个具体问题是使用抽象类编程而不是接口。Struts 2 Action类可以实现一个Action接口,也可以实现其他接口,使可选和定制的服务成为可能。Struts 2提供一个ActionSupport基类去实现常用的接口。即使Action接口不是必须实现的,只有一个包含execute方法的P

- 初学者要多看看帮助文档 不要用js来写Jquery的代码

百合不是茶

jqueryjs

解析json数据的时候需要将解析的数据写到文本框中, 出现了用js来写Jquery代码的问题;

1, JQuery的赋值 有问题

代码如下: data.username 表示的是: 网易

$("#use

- 经理怎么和员工搞好关系和信任

bijian1013

团队项目管理管理

产品经理应该有坚实的专业基础,这里的基础包括产品方向和产品策略的把握,包括设计,也包括对技术的理解和见识,对运营和市场的敏感,以及良好的沟通和协作能力。换言之,既然是产品经理,整个产品的方方面面都应该能摸得出门道。这也不懂那也不懂,如何让人信服?如何让自己懂?就是不断学习,不仅仅从书本中,更从平时和各种角色的沟通

- 如何为rich:tree不同类型节点设置右键菜单

sunjing

contextMenutreeRichfaces

组合使用target和targetSelector就可以啦,如下: <rich:tree id="ruleTree" value="#{treeAction.ruleTree}" var="node" nodeType="#{node.type}"

selectionChangeListener=&qu

- 【Redis二】Redis2.8.17搭建主从复制环境

bit1129

redis

开始使用Redis2.8.17

Redis第一篇在Redis2.4.5上搭建主从复制环境,对它的主从复制的工作机制,真正的惊呆了。不知道Redis2.8.17的主从复制机制是怎样的,Redis到了2.4.5这个版本,主从复制还做成那样,Impossible is nothing! 本篇把主从复制环境再搭一遍看看效果,这次在Unbuntu上用官方支持的版本。 Ubuntu上安装Red

- JSONObject转换JSON--将Date转换为指定格式

白糖_

JSONObject

项目中,经常会用JSONObject插件将JavaBean或List<JavaBean>转换为JSON格式的字符串,而JavaBean的属性有时候会有java.util.Date这个类型的时间对象,这时JSONObject默认会将Date属性转换成这样的格式:

{"nanos":0,"time":-27076233600000,

- JavaScript语言精粹读书笔记

braveCS

JavaScript

【经典用法】:

//①定义新方法

Function .prototype.method=function(name, func){

this.prototype[name]=func;

return this;

}

//②给Object增加一个create方法,这个方法创建一个使用原对

- 编程之美-找符合条件的整数 用字符串来表示大整数避免溢出

bylijinnan

编程之美

import java.util.LinkedList;

public class FindInteger {

/**

* 编程之美 找符合条件的整数 用字符串来表示大整数避免溢出

* 题目:任意给定一个正整数N,求一个最小的正整数M(M>1),使得N*M的十进制表示形式里只含有1和0

*

* 假设当前正在搜索由0,1组成的K位十进制数

- 读书笔记

chengxuyuancsdn

读书笔记

1、Struts访问资源

2、把静态参数传递给一个动作

3、<result>type属性

4、s:iterator、s:if c:forEach

5、StringBuilder和StringBuffer

6、spring配置拦截器

1、访问资源

(1)通过ServletActionContext对象和实现ServletContextAware,ServletReque

- [通讯与电力]光网城市建设的一些问题

comsci

问题

信号防护的问题,前面已经说过了,这里要说光网交换机与市电保障的关系

我们过去用的ADSL线路,因为是电话线,在小区和街道电力中断的情况下,只要在家里用笔记本电脑+蓄电池,连接ADSL,同样可以上网........

- oracle 空间RESUMABLE

daizj

oracle空间不足RESUMABLE错误挂起

空间RESUMABLE操作 转

Oracle从9i开始引入这个功能,当出现空间不足等相关的错误时,Oracle可以不是马上返回错误信息,并回滚当前的操作,而是将操作挂起,直到挂起时间超过RESUMABLE TIMEOUT,或者空间不足的错误被解决。

这一篇简单介绍空间RESUMABLE的例子。

第一次碰到这个特性是在一次安装9i数据库的过程中,在利用D

- 重构第一次写的线程池

dieslrae

线程池 python

最近没有什么学习欲望,修改之前的线程池的计划一直搁置,这几天比较闲,还是做了一次重构,由之前的2个类拆分为现在的4个类.

1、首先是工作线程类:TaskThread,此类为一个工作线程,用于完成一个工作任务,提供等待(wait),继续(proceed),绑定任务(bindTask)等方法

#!/usr/bin/env python

# -*- coding:utf8 -*-

- C语言学习六指针

dcj3sjt126com

c

初识指针,简单示例程序:

/*

指针就是地址,地址就是指针

地址就是内存单元的编号

指针变量是存放地址的变量

指针和指针变量是两个不同的概念

但是要注意: 通常我们叙述时会把指针变量简称为指针,实际它们含义并不一样

*/

# include <stdio.h>

int main(void)

{

int * p; // p是变量的名字, int *

- yii2 beforeSave afterSave beforeDelete

dcj3sjt126com

delete

public function afterSave($insert, $changedAttributes)

{

parent::afterSave($insert, $changedAttributes);

if($insert) {

//这里是新增数据

} else {

//这里是更新数据

}

}

- timertask

shuizhaosi888

timertask

java.util.Timer timer = new java.util.Timer(true);

// true 说明这个timer以daemon方式运行(优先级低,

// 程序结束timer也自动结束),注意,javax.swing

// 包中也有一个Timer类,如果import中用到swing包,

// 要注意名字的冲突。

TimerTask task = new

- Spring Security(13)——session管理

234390216

sessionSpring Security攻击保护超时

session管理

目录

1.1 检测session超时

1.2 concurrency-control

1.3 session 固定攻击保护

- 公司项目NODEJS实践0.3[ mongo / session ...]

逐行分析JS源代码

mongodbsessionnodejs

http://www.upopen.cn

一、前言

书接上回,我们搭建了WEB服务端路由、模板等功能,完成了register 通过ajax与后端的通信,今天主要完成数据与mongodb的存取,实现注册 / 登录 /

- pojo.vo.po.domain区别

LiaoJuncai

javaVOPOJOjavabeandomain

POJO = "Plain Old Java Object",是MartinFowler等发明的一个术语,用来表示普通的Java对象,不是JavaBean, EntityBean 或者 SessionBean。POJO不但当任何特殊的角色,也不实现任何特殊的Java框架的接口如,EJB, JDBC等等。

即POJO是一个简单的普通的Java对象,它包含业务逻辑

- Windows Error Code

OhMyCC

windows

0 操作成功完成.

1 功能错误.

2 系统找不到指定的文件.

3 系统找不到指定的路径.

4 系统无法打开文件.

5 拒绝访问.

6 句柄无效.

7 存储控制块被损坏.

8 存储空间不足, 无法处理此命令.

9 存储控制块地址无效.

10 环境错误.

11 试图加载格式错误的程序.

12 访问码无效.

13 数据无效.

14 存储器不足, 无法完成此操作.

15 系

- 在storm集群环境下发布Topology

roadrunners

集群stormtopologyspoutbolt

storm的topology设计和开发就略过了。本章主要来说说如何在storm的集群环境中,通过storm的管理命令来发布和管理集群中的topology。

1、打包

打包插件是使用maven提供的maven-shade-plugin,详细见maven-shade-plugin。

<plugin>

<groupId>org.apache.maven.

- 为什么不允许代码里出现“魔数”

tomcat_oracle

java

在一个新项目中,我最先做的事情之一,就是建立使用诸如Checkstyle和Findbugs之类工具的准则。目的是制定一些代码规范,以及避免通过静态代码分析就能够检测到的bug。 迟早会有人给出案例说这样太离谱了。其中的一个案例是Checkstyle的魔数检查。它会对任何没有定义常量就使用的数字字面量给出警告,除了-1、0、1和2。 很多开发者在这个检查方面都有问题,这可以从结果

- zoj 3511 Cake Robbery(线段树)

阿尔萨斯

线段树

题目链接:zoj 3511 Cake Robbery

题目大意:就是有一个N边形的蛋糕,切M刀,从中挑选一块边数最多的,保证没有两条边重叠。

解题思路:有多少个顶点即为有多少条边,所以直接按照切刀切掉点的个数排序,然后用线段树维护剩下的还有哪些点。

#include <cstdio>

#include <cstring>

#include <vector&