FPGA之FIFO IP核详细教程

FPGA之fifo的相关知识(附完整设计代码,仿真代码)

本文回答以下几个问题:

1:fifo是什么,有什么作用;

2:在使用fifo的两种模式;

3:使用异步fifo IP核的详细步骤说明;

4:RTL设计和仿真;

5:功能仿真;

下面一 一解释上面的几个问题

1: Fifo是什么 :fifo是英文first in first out 的缩写,即先进先出(队列),fifo在FPGA内部是RAM加上已编写好的读写控制模块(RTL级)然后“封装”在一起的一个module

fifo使用场景

1.1 信号的跨时钟域处理

fifo很多时候用在数据或者是信号跨时钟域的处理上,如多位宽信号S在A的时钟域是10MHz,现在要把信号S传到B时钟域20MHz,这种不同时钟域之间的信号切换常常会建立时间保持时间不满足进而导致亚稳态的产生。而亚稳态在时序电路设计中是灾难性的。采用fifo几乎可以避免亚稳态的产生。

1.2 解决输入输出数据位宽不一致的问题

例如输入信号是16位宽,而输出每次只需要8位宽,不考虑跨时钟域的情况下,可以在时序触发下先截取低8位,再截取高8位,这样做在数据较少还是比较实用,但是当数据量很多时,会占用较多的存储器资源,而且处理起来远不如fifo方便。

2: 在使用fifo IP核时在配置页面有同步fifo和异步fifo。同步fifo是读写时钟相同,异步fifo读写时钟不同。

3.这里以Quartus为例

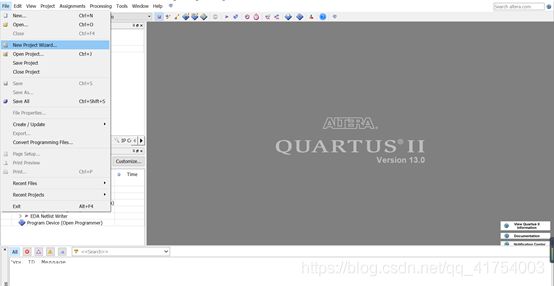

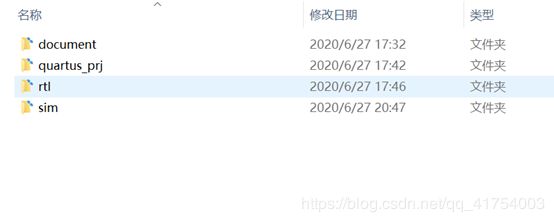

①建立一个工程

接下来就是填写工程名和工程存储路径

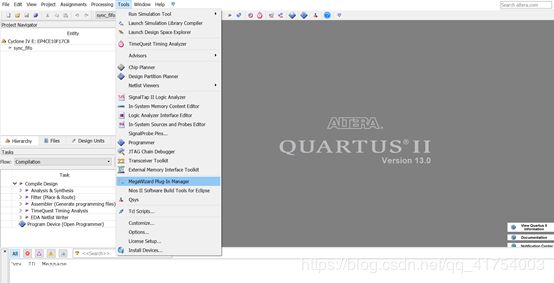

②在Tools下找到MegaWizard Plug-In Manager点击进入

选择第一个Create a new custom megafunction variation点击next

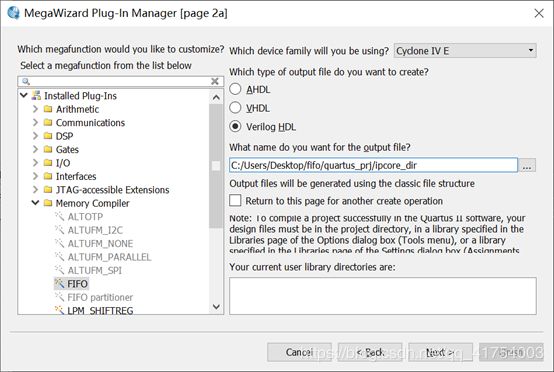

上图中在Memory Complier中找到FIFO IP核,如图右上默认的芯片是Cyclone IV E,和开头建项目时是同步的。在这下面默认的是硬件描述语言是Verilog HDL 本次用到的是Verilog。再下面是IP核的存放位置。为了便于项目移植和文件的整洁性,建议在quaetus_prj文件夹下建议一个ipcoer_dir的文件夹当做IP核的生成路径

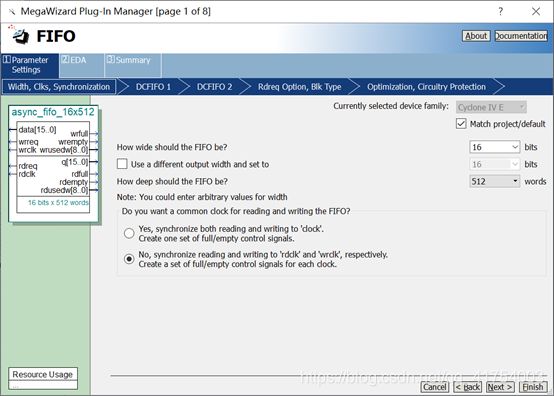

③接下来到了IP核的配置页面

第一个选项让用户选择是否输入输出是不同位宽,按照自己的项目需求选择,这里不勾上,代表输入输出位宽一致,选择16位数据位宽,右上角第一个16bit是输入数据位宽,第二个灰色的16是输出位宽,刚刚选择的是输入输出位宽相等,所以对于输出位宽无法更改。下面512是数据深度,根据需求选择。

下面的同步异步的选择,这里选择异步fifo。当我们选择好后可以看到左边fifo框图已经显示出了fifo的一些I/O口。左下角是用的芯片内部资源,可以看到用了22个LUT,一个M9K和128个寄存器。点击next进入下一个配置页面

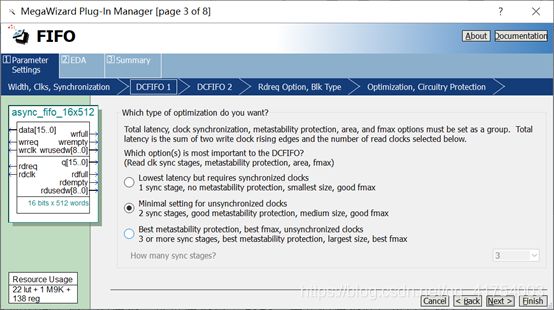

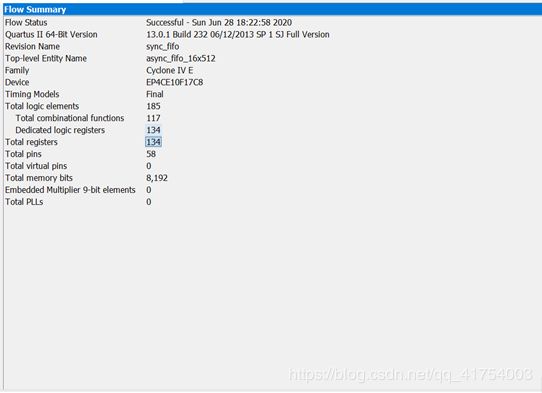

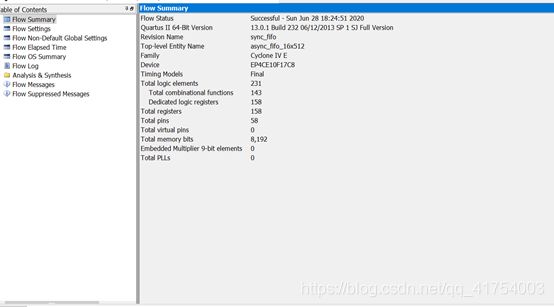

这里选择对少个latency,latency字面意思是潜伏,这里是rd_req读请求有效后等到多少个时钟周期后数据才输出,越多越能减少亚文态发生的概率,但是多了以后相应的资源会变多,下面依次是2个latency和3个latency。可以看到3个latency所用的寄存器和逻辑门都要多于2个latency的。

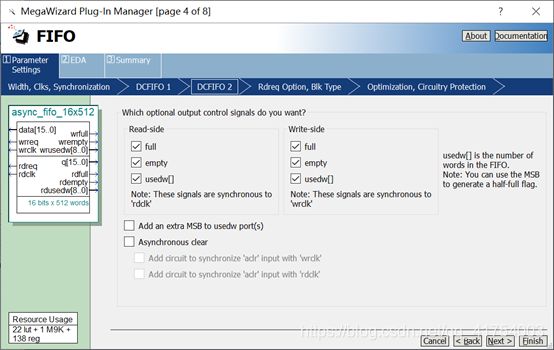

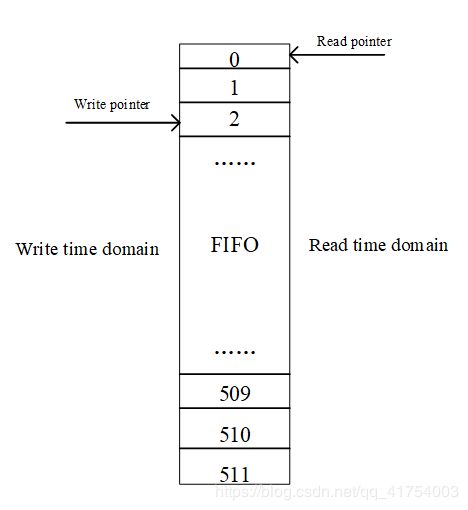

下图左侧是读时钟域下的写满,读空和已使用的总字数,右侧对应于写时钟域下的信号。如图,所谓写满是指写指针追上了读指针,这时读的太慢,则会出现读指针追上写指针指针对应的地址数据还没读完就被重新写入了,造成数据的丢失。而读空是指,读指针追上了写指针,这时会造成读指针追上和超过写指针地址所对应读出的数据是无效的。下面两个是增加usedw的端口和复位暂时不用管,点击next

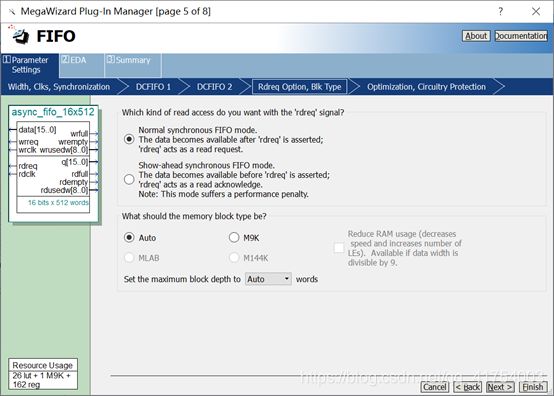

下图,这里有normal模式和show-ahead模式。Normal模式是给定地址后在下一个时钟周期把数据读取出来。Show-ahead模式相当于预读取,地址给定数据就读出来。可以看到show-ahead模式下面的Note,这种模式可能会带来时序上的违例。这里选择normal模式。点击next

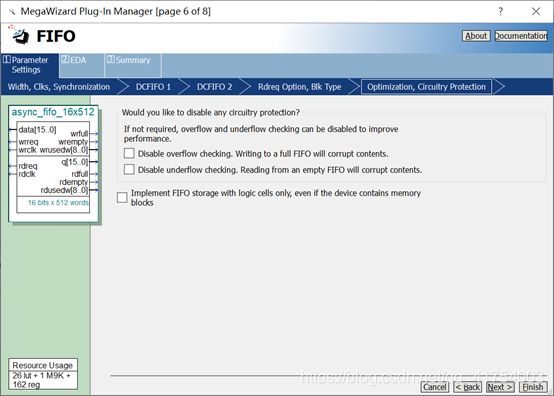

这里两个是写溢出和读空保护,点击是取消保护,这里不去勾选。点击next

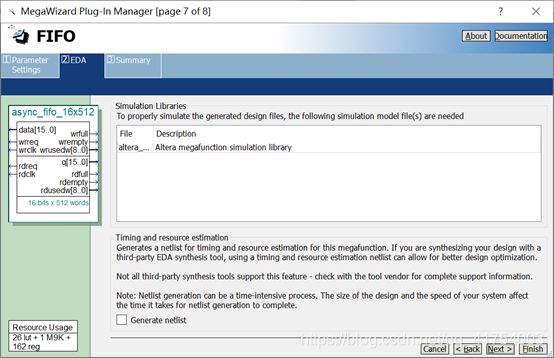

先不去生成网标信息,继续点击next

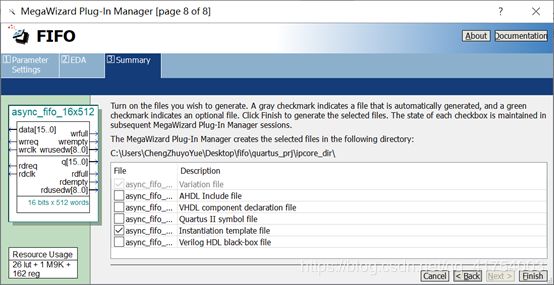

这里为了方便把 Instantiation template file选上,生成例化文件在./quartus_prj/ipcore_dir 目录先找到“_inst.v”结尾的文件,将其复制到工程中去。

4.1 RTL设计

module async_fifo(

input wire wr_clk,

input wire wrdata_v,

input wire rd_clk,

input wire rd_req,

input wire [15:0] data_in,

output wire [15:0] data_o

);

parameter DW_FLAG = 512 - 2;

wire rdfull,rdempty,wrempty,wrfull;

wire wr_req;

wire [8:0] rdusedw;

wire [8:0] wrusedw;

wire wrusedw_flag;

assign wrusedw_flag = (wrusedw > DW_FLAG) ? 1'b1:1'b0;

assign wr_req = (~wrusedw_flag) & wrdata_v;

async_fifo_16x512 async_fifo_16x512_inst (

.data ( data_in ),//写入的数据

.rdclk ( rd_clk ),//读时钟

.rdreq ( rd_req ),//读请求

.wrclk ( wr_clk ),//写时钟

.wrreq ( wr_req ),//写请求

.q ( data_o ),//读数据输出

.rdempty ( rdempty ),//读空标志

.rdfull ( rdfull ),//读时钟域的写满信号

.rdusedw ( rdusedw ),//读剩余的地址数量

.wrempty ( wrempty ),//写满标志

.wrfull ( wrfull ),//写时钟域的读空标志

.wrusedw ( wrusedw )//已经写得可用地址数

);

endmodule

4.2仿真文件

`timescale 1ns/1ns

module tb_async_fifo();

reg rd_clk;

reg wr_clk;

reg [15:0] wr_data;

reg wr_v;

reg rd_req;

initial begin

wr_clk = 0;

rd_clk = 0;

wr_clk = 0;

wr_data = 0;

wr_v = 0;

rd_req = 0;

#50

write_data();

end

initial begin

#50

read_data();

end

always #10 wr_clk = ~wr_clk;

always #5 rd_clk = ~rd_clk;

async_fifo async_fifo_inst(

.wr_clk (wr_clk),

.wrdata_v (wr_v),

.rd_clk (rd_clk),

.rd_req (rd_req),

.data_in (wr_data),

.data_o ()

);

task write_data();

integer i;

begin

for(i=0;i<512;i=i+1)

begin

@(posedge wr_clk)

wr_v = 1;

wr_data = i;

end

@(posedge wr_clk)

wr_v = 0;

wr_data = 0;

end

endtask

task read_data();

integer j;

begin

for(j=0;j<1100;j=j+1)

@(posedge rd_clk)

begin

if(j>520)

rd_req = 1;

else

rd_req = 0;

end

end

endtask

endmodule

5.1仿真分析

这里用Modelsim进行仿真,可以直接从quartus中直接调用modelsim软件并自动生成仿真文件,但是每次都要修改仿真文件,在sim目录下建一个仿真文件自己编写了,内容在4.2。

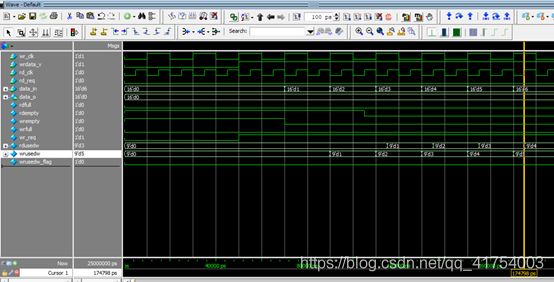

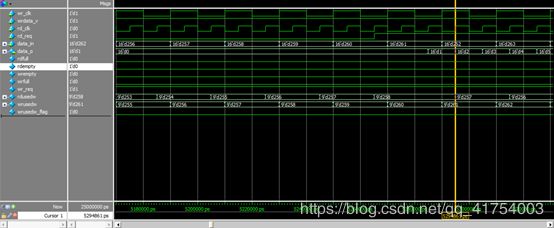

如图在wr_req有效时数据就立即写入fifo里了,第一个数据是8’d0,在两个wr_clk后wrusedw数量是1个

然后再看rd_req有效时,在读请求有效后过了两个时钟周期rdusedw才变化,这里对应之前配置页面选择的两个latency。

3个latency可以看到在rd_req有效三个时钟周期后rdusedw才变化

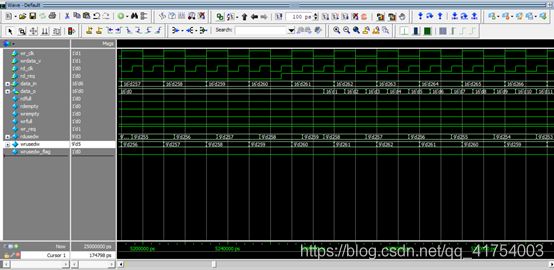

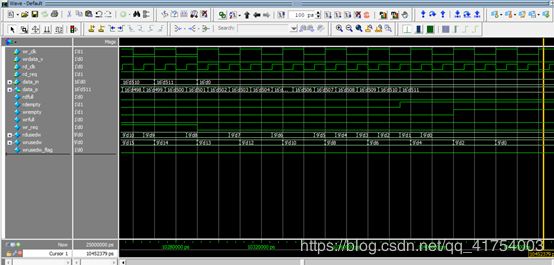

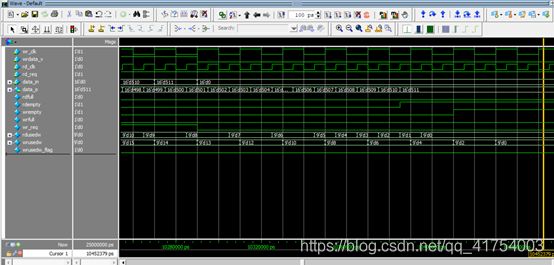

下图所示数据写完并读完时的信号变化,在4.2仿真文件中让读时钟是写时钟的2倍,然后在读时钟的第520(对应于写时钟的第260个周期)个时钟周期让读请求有效,所以保证读指针在第511数据及其以前不追上写指针。读时钟域下读空信号rdempty先于rdusedw等于0两个时钟周期给出有效信号。告诉你,不要再读了,已经读完了,要不再等等写指针再动一动,咱再读(滑稽)

如下图可以看到在写时钟域下当第512个数据511写入ram中时wrfull并未拉高,因为已经读的数据那些地址等写指针写完一个数据周期(512个数据)回到0地址还可以继续写,(这里指针和地址没有区分,一样的概念),因为读指针已经把要的数据拿走了不需要了。两个时钟域下usedw很有用,由它可以产生一些标志信号能给出一些预留时间防止出现写满或者读空的情况。

如果你认真读到这里,不妨打开工具自己动手做一下。文中如果有错误或者瑕疵欢迎指正,虚心接受。