1. SRAM存储器(静态读写存储器)

-

- 存取速度快,容量小,价格昂贵。

- 基本的静态存储元阵列包含:1. 存储位元 2. 三组信号线(地址线、数据线、控制线)。

- 通常做成Cache,Cache主要是为了平缓各器件之间的差异。

- 掉电就丢失。

- 注意:读写操作不会同时发生。(读与写功能的互锁逻辑)

2. DRAM存储器(动态读写存储器)

-

- 存储容量大,速度慢,价格低廉。

- 存储位元的记忆原理:DRAM存储器的存储位元是由一个MOS晶体管和电容器组成的记忆电路。——MOS管被当作开关使用,信息1或0则是有电容器上的电荷量来体现的。——充满电时为1,没有电荷时为0。

- 通常做成主存

- SRAM与DRAM的比较

| SRAM | DRAM | |

| 存储信息 | 触发器 | 电容 |

| 面积 | 大 | 小 |

| 容量 | 少 | 多 |

| 存储成本 | 高 | 低 |

| 破坏性读出 | 非 | 是 |

| 需要刷新 | 不要 | 要 |

| 存取速度 | 快 | 慢 |

| 功率损耗 | 少 | 多 |

| 集成度 | 低 | 高 |

3. SRAM和DRAM容易扩充,扩充原则:先横后竖

- 字长位数扩展(位扩展)

- 需要用多片给定芯片扩展字长位数。

- 所需芯片:D=设计要求的存储器容量/选择芯片存储器容量

- 字存储容量扩展(字扩展)

- 给定的芯片存储容量较小(字数少),此时需要用多片给定芯片来扩展字数。

- 所需芯片:D=设计要求的存储器容量/选择存储器容量

- 字扩展:

- 所需芯片数量=CPU能访问的存储器总容量/每个芯片所能提供的容量。

- 依据芯片的地址线把CPU的地址线分为内地址(一般用低位地址线)。

- 片内地址线直接与芯片地址线相连。

- 片外地址线经过译码与芯片的片选端相连。

- 字位同时扩展

- 先横后竖

4. 只读存储器和闪速存储器(只要求记忆)

- 只读存储器ROM

- 掩模ROM:实际上是一个存储内容固定的ROM,由生产厂家提供产品。

- 可编程ROM:用户后写入内容,有些可以多次写入

- 一次性编程的PROM

- 多次编程的EPROM和EEPROM

- EPROM:光擦出可编程可读存储器

- EEPROM:电擦除可编程可读存储器

- 高密度:意味着其具有比特数目巨大的存储容量

- 非易失性:存储的数据在没有电源的情况下可以长期保存。

5. 并行存储器(为了提高CPU与主存之间的数据传输率,因而可以采用并行技术的存储器)

- 双端口存储器(有两个相对独立的读写控制电路而得名)

- 双端口存储器的逻辑结构(高速的)

双端口存储器由于同一个存储器具有两组相互独立的读写控制电路而得名。由于进行并行的独立操作,因而是一种高速工作的存储器,在科研和工程中非常有用。

-

- 无冲突读写控制

当两个端口的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突。当任一端口被选中驱动时,就可对整个存储器进行存取,每一个端口都有自己的片选控制(CE)和输出驱动控制(OE)。读操作时,端口的OE(低电平有效)打开输出驱动器,由存储矩阵读出的数据就出现在I/O线上

-

- 有冲突读写控制(BUSY标志)

当两个端口同时存取存储器同一存储单元时,便发生读写冲突。为解决此问题,特设置了BUSY标志。在这种情况下,片上的判断逻辑可以决定对哪个端口优先进行读写操作,而对另一个被延迟的端口置BUSY标志(BUSY变为低电平),即暂时关闭此端口

-

- 有冲突读写控制判断方法

- 如果地址匹配且在CE之前有效,片上的控制逻辑在CEL和CER之间进行判断来选择端口(CE(输出驱动控制)判断)

- 如果CE(输出驱动控制)在地址匹配之前变低,片上的控制逻辑在左、右地址间进行判断来选择端口(地址有效判断)

- 无论采用哪种判断方式,延迟端口的BUSY标志都将置位而关闭此端口,而当允许存取的端口完成操作时,延迟端口BUSY标志才进行复位而打开此端口

- 多模块交叉存储器(并行技术)

- 多体:多个存储器模块。

- 交叉:多模块交叉寻址。

-

- 字长*模块数=信息总量

- 顺序存储器存储时间:模块数*每个模块的存储周期

- 交叉存储器存储时间:单个模块存储周期+(模块数-1)*总线传输周期

- 顺序存储器带宽:信息总量/顺序存储器的存储时间

- 交叉存储器带宽:信息总量/交叉存储器的存储时间

6. Cache存储器(地址映射)

- Cache的功能:

-

- 平缓速度不匹配的现象。

- 一般采用高速的SRAM构成

- CPU与主存之间的速度差异特别大,采用两级或多级Cache系统

- 全由硬件调度,对用户透明。

- Cache的基本原理:

-

- 主存与Cache之间的数据是以“块”为单位传输的。

- CPU读主存时,把地址同时给Cache和主存,Cache控制逻辑依据地址判断此字是否在Cache中,若在,此字立即传送到CPU,否则,用主存读周期把此字从主存送到CPU中,与此同时,把含有这个字的整个数据块从主存猝发式读入Cache中执行。

- Cache的命中率:

-

- CPU的命中率接近于1

- 命中率与程序的行为、Cache的容量、组织方式、块的大小有关。

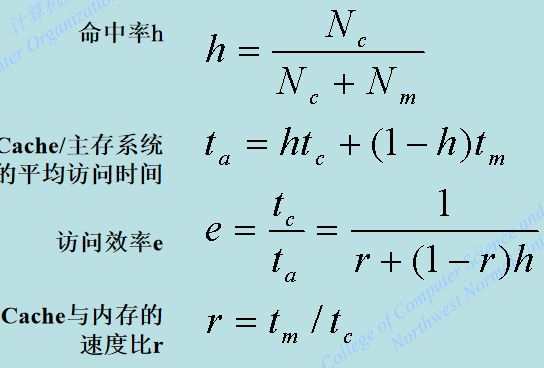

- 公式:

-

- 在一个程序执行期间,设Nc表示cache完成存取的总次数,Nm表示主存完成存取的总次数,h定义为命中率,则有h=Nc/(Nc+Nm)

- 若tc表示命中时的cache访问时间,tm表示未命中时的主存访问时间,1-h表示未命中率,则cache/主存系统的平均访问时间ta为ta=h*tc+(1-h)tm

- 地址映射方法:把主存某单元如何定位到Cache某单元

- 无论选择哪种映射方式,都要把主存和Cache划分为同样大小的“块”(行)

- 数据交换单位:块(行),块大小相同,块数不同。

- 全相联的映射方式(块冲突率低,地址映射缓慢,使用命中时间长)

- 映射方式(多对多)

主存地址可以拷贝到任一行

-

- 地址变换

标记实际上构成了一个目录表(用一个相联存储器实现)

-

- 将地址分成两部分(块号和字号)。在内存块中写入Cache时,同时写入块号标记

- CPU给出访问地址时,也将地址分为块号和字,对块号与Cache中的标记进行比较从而比较电路。相同表示命中,访问相应单元;如果没有命中,CPU直接访问内存,并将被访问内存的相应块写入Cache某行中。

- 特点:

- 优点:冲突概率小,Cache利用率高

- 缺点:比较器难以实现,需要一个访问速度很快代价高的相联存储器

- 适用场合:

- 小容量的Cache

- 直接映射方式(主存某块只能被交换到Cache的特定某行中)(特点:地址映射速度快,适用命中率高、块冲突率高,相对命中率低)

- 映射方式(一对多)如:

- i= j mod m

- 主存第j块内容只能拷贝到cache的第i行中

- m为cache中的总行数

- [例]cache容量为16行,主存容量256块,则地址2,18,34…..242等都存放在cache的地址为2的行内,如果第一次18号块在cache的第2 行中,下次访问34号块的内容,则不管cache其他位置的内容访问情况,都会引起2号行内容的替换

- 基本原理:

- 利用行号选择相应行

- 把行标记与CPU访问地址进行比较,相同表示命中,访问Cache

- 如果没有命中,访问内存,并将相应块雪茹Cache

- 特点:

- 优点:比较电路少,硬件实现简单;Cache地址为主存地址的第位,无需变换

- 缺点:冲突率高(抖动)

- 应用场合:

- 适合大容量Cache

- 映射方式(一对多)如:

- 组相联映射方式

- 前两种的组合

- Cache分组,组间采用直接映射方式,组内采用全相联的映射方式

- Cache分U组,组内容量V行

- 映射方式(一对多)

- q= j mod u //主存第j块内容拷贝到Cache第q组中的某行

- 地址变换

- 设主存地址x,看是不是在cache中,先y= x mod u,则在y组的V行中依次查找

- 分析:比全相联容易实现,冲突低

- V=1,则为直接相联映射方式

- U=1,则为全相联映射方式

- V的值一般比较小,一般是2的幂,称之为V路组相联Cache

- 前两种的组合

- 三种方法比较:

| 直接映射 | 全相联映射 | 组相联映射 | |

| 优点 | 节省硬件,目录表小,成本低 | (1)块冲突最低 (2)Cache空间利用率最高 |

集中全相联和直接映射的优点弥补他们的缺点 |

| 缺点 | (1)块冲突率很大 (2)Cache空间利用率很低 |

(1)映射表太长 (2)查表速度慢 |

块冲突仍大于全相联 利用率低于全相联 目录表大于直接方式 |