DSP学习笔记----EMIF(外部存储器接口)

一. EMIF介绍

CE空间:

dsp的存储空间分为片内和片外两种,片外空间分成四个部分,分别用于映射不同的片外设备,即ce空间 。

The remainder of the memory map is external space that is divided into four spaces. Each space has a chip

enable decode signal (called CE) that indicates an access to the selected space.内存映射的其余部分是被划分为四个空间的外部空间。每个空间都有一个可芯片解码信号(称为CE),表示对所选空间的访问。

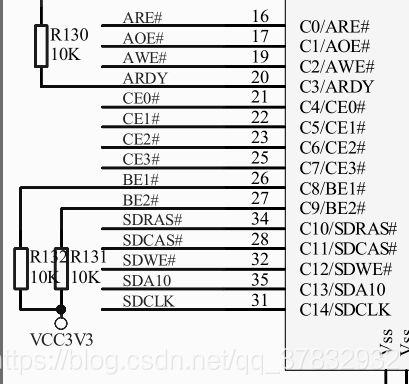

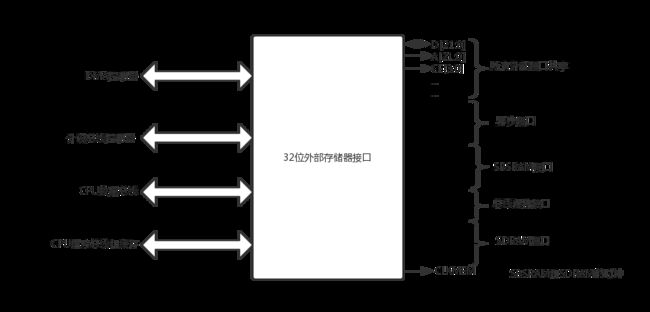

EMIF就是外部存储器接口,知识DSP上的引脚,用于外接存储器设备。CPU与外部存储器的连接口。在芯片上的位置如下图。

它的结构框图如下:

接口位的作用及配置参考: https://blog.csdn.net/app_12062011/article/details/7869589

EMIF支持的存储器:

1 异步存储器,包括ROM,FLASH,异步SRAM

2 同步突发静态存储器(SBSRAM)

3 同步动态存储器(SDRAM)

二. EMIF设计

EMIF的设计要针对不同的存储器,C55x设置了4个片选信号CE0~CE3,直接作为外部存储器的选通信号。

三. EMIF编程实验

最重要的是配置寄存器

对于与SDRAM连接的配置过程:

配置开始->全局控制寄存器配置EMIF时钟->CE空间寄存器配置SDRAM空间->SDCTL配置SDRAM工作模式->SDTIM配置刷新模式->配置扩展功能->配置结束

(就是通过EMIF的寄存器去控制SDRAM的接口?)

总的程序

/******************************************************************************/

/******************************************************************************/

/*----------------------------------------------------------------------------*/

/* MODULE NAME... EMIF */

/* FILENAME...... emif.c */

/* DATE CREATED.. Wed 2/4/2004 */

/* PROJECT....... write and read data between the CPU and SDRAM */

/* COMPONENT..... */

/* PREREQUISITS.. */

/*----------------------------------------------------------------------------*/

/*----------------------------------------------------------------------------*/

/* DESCRIPTION: */

/* */

/* This is an example for EMIF of C5509 */

/*----------------------------------------------------------------------------*/

#include

#include

#include

#include

#include

Uint16 x;

Uint32 y;

CSLBool b;

unsigned int datacount = 0;

int databuffer[1000] ={0};

int *souraddr,*deminaddr;

/*锁相环的设置*/

PLL_Config myConfig = {

0, //IAI: the PLL locks using the same process that was underway

//before the idle mode was entered

1, //IOB: If the PLL indicates a break in the phase lock,

//it switches to its bypass mode and restarts the PLL phase-locking

//sequence

20, //PLL multiply value; multiply 24 times

1 //Divide by 2 PLL divide value; it can be either PLL divide value

//(when PLL is enabled), or Bypass-mode divide value

//(PLL in bypass mode, if PLL multiply value is set to 1)

};

/*SDRAM的EMIF设置*/

EMIF_Config emiffig = {

0x221, //EGCR : the MEMFREQ = 00,the clock for the memory is equal to cpu frequence

// the WPE = 0 ,forbiden the writing posting when we debug the EMIF

// the MEMCEN = 1,the memory clock is reflected on the CLKMEM pin

// the NOHOLD = 1,HOLD requests are not recognized by the EMIF

0xFFFF, //EMI_RST: any write to this register resets the EMIF state machine

0x3FFF, //CE0_1: CE0 space control register 1

// MTYPE = 011,Synchronous DRAM(SDRAM),16-bit data bus width

0xFFFF, //CE0_2: CE0 space control register 2

0x00FF, //CE0_3: CE0 space control register 3

// TIMEOUT = 0xFF;

0x7FFF, //CE1_1: CE0 space control register 1

0xFFFF, //CE1_2: CE0 space control register 2

0x00FF, //CE1_3: CE0 space control register 3

0x7FFF, //CE2_1: CE0 space control register 1

0xFFFF, //CE2_2: CE0 space control register 2

0x00FF, //CE2_3: CE0 space control register 3

0x7FFF, //CE3_1: CE0 space control register 1

0xFFFF, //CE3_2: CE0 space control register 2

0x00FF, //CE3_3: CE0 space control register 3

0x2911, //SDC1: SDRAM control register 1

// TRC = 8

// SDSIZE = 0;SDWID = 0

// RFEN = 1

// TRCD = 2

// TRP = 2

0x0410, //SDPER : SDRAM period register

// 7ns *4096

0x07FF, //SDINIT: SDRAM initialization register

// any write to this register to init the all CE spaces,

// do it after hardware reset or power up the C55x device

0x0131 //SDC2: SDRAM control register 2

// SDACC = 0;

// TMRD = 01;

// TRAS = 0101;

// TACTV2ACTV = 0001;

};

main()

{

unsigned int error=0;

/*初始化CSL库*/

CSL_init();

/*EMIF为全EMIF接口*/

CHIP_RSET(XBSR,0x0a01);

/*设置系统的运行速度为120MHz*/

PLL_config(&myConfig);

/*初始化DSP的外部SDRAM*/

EMIF_config(&emiffig);

/*向SDRAM中写入数据*/

souraddr = (int *)0x40000;

deminaddr = (int *)0x41000;

while(souraddr 四.参考博客

https://blog.csdn.net/app_12062011/article/details/7869589