FPGA时序分析理论篇

1、前言

毕业后开始接触FPGA,虽然在学校就学习过verilog,但是只是学学开发板的代码,对于时序这块还是接触很少,毕业后第一个项目大量需要时序约束的知识,但是最后也没用上,因为需要时序约束的IP核是老外写的,自己写的IP核不加也能用。我这里写的文章大多是参考黑金的文档资料以及自己买的时序约束视频,具体哪家自己淘宝。不过官方文档,最为权威。

1.1 寄存器特性参数

对于如图1所示的寄存器,时序分析时一定会遇到的三个时间参数是Tco、Tsu、Th。其中Tco是输出延迟,指的是有效时钟沿到来后,输出引脚上获得有效输出的最大延迟时间。Tsu是建立时间,指的是寄存器想要正确寄存数据,数据需要在有效沿到来之前最小保持时间。Th指的是寄存器想要正确寄存时间,数据需要在有效沿到来之后,最小的稳定时间。三者的关系如图2所示。

图1 一般寄存器的图形表示

图2 Tco、Tsu、Th

图2中,CLK的第一个上升沿后隔了Tco之后,寄存器的Q端开始有数据输出。此时寄存器把数据发往下一个寄存器,下一个寄存器在第二个始终上升沿寄存数据,所以数据必须满足在上升沿到来之前维持自身稳定Tsu的时长,且上升沿到来之后维持自身稳定Th时长。从图形上看,以第一个时间上升沿为0刻度点的话,数据前端在时间必须早于Tclk-Tsu,后端时间大于Tclk+Th。

1.2 时序约束的目的

时序约束的目的,就是控制FPGA的综合、布局和布线,使得寄存器可以正确的寄存数据。也就是说使得数据满足建立时间大于Tsu,保持时间大于Th。一般说来,由于组合逻辑和线延时的存在,会使得数据建立时间不够Tsu,但是Th是满足的。

2、时序分析理论

2.1 时序分析的一般理论模型

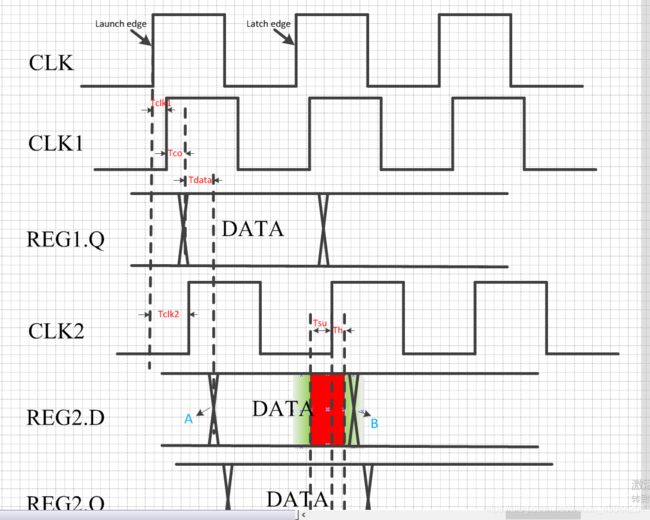

时序分析的理论模型如图2所示。REG1为源寄存器,REG2为目的寄存器。Tclk1是时钟从全局时钟资源到达REG1时钟端的延迟,Tclk2是时钟从全局时钟资源到达REG2时钟端的延迟,Tdata是数据从REG1到REG2中所有的延迟的总值,包括线延迟和组合逻辑延迟等。

图3 时序分析的一般理论模型

2.2 建立关系和保持关系

对于同步时钟设计,建立关系(set up relationship)一般为时钟周期Tclk,保持关系(hold relationship)一般为0。

2.3 时序图及其计算

对于图3的一般时序模型,它的的时序图如图4所示,我们假定CLK的第一个上升沿为launch edge即发射沿,第二个上升沿为latch edge即锁存沿。通过前段分析可知,数据想要正确被下一级寄存器寄存,必须满足建立时间大于Tsu和保持时间大于Th,即满足建立时间余量(set up slack)和保持时间余量(hold slack)。

图4 图3的 时序图

2.3.1 建立时间余量(set up slack)

对于建立时间余量(set up slack)有:

data arrival time = launch edge + Tclk1 + Tco + Tdata

注:对应到图形中就是REG2.D的DATA的A端,数据到达时间指的是数据“头”到达REG2.D端的时间

data required time = latch edge + Tclk2 -Tsu

注:对应到图形中就是REG2.D中红色区域的左边,数据要求时间就是如果数据要被REG2正确寄存,他的到达时间要早于这个时刻。so 建立时间余量(set up slack)大于0则表示数据到达时间早于数据要求时间,否则晚于。

set up slack = data required time - data arrival time

= (latch edge + Tclk2 -Tsu) - (launch edge + Tclk1 + Tco + Tdata)

=(latch edge - launch edge) + (Tclk2 - Tclk1 ) - Tsu - Tco -Tdata

= T +Tskew - Tsu - Tco -Tdata

注:其中T为时钟周期,Tskew时钟偏斜(可以认为为0)。

2.3.2 保持时间余量(hold slack)

对于保持时间余量(hold slack)有:

data hold time = launch edge + Tclk1 + Tco + Tdata + Td

注:1、其中Td还数据周期,大小一般是时钟周期。

2、对应到图形中就是REG2.D的DATA的B端,数据到达时间指的是数据“尾”到达REG2.D端的时间

data required time = latch edge + Tclk2 + Th

注:对应到图形中就是REG2.D中红色区域的右边,数据要求时间就是如果数据要被REG2正确寄存,他的持续时间要晚于这个时刻。so 保持时间余量(hold slack)大于0则表示数据保持时间“晚”于数据要求时间,否则“早”于。

hold slack = data hold time - data required time

= (launch edge + Tclk1 + Tco + Tdata + Td) - (latch edge + Tclk2 + Th)

= (launch edge - latch edge)+ (Tclk1 - Tclk2 )+Tco + Tdata + Td - Th

= Tco + Tdata - Th - Tskew

3、总结

建立时间余量 set up slack = T +Tskew - Tsu - Tco -Tdata

保持时间余量 hold slack = Tco + Tdata - Th - Tskew

注:其中T为时钟周期,Tskew时钟偏斜。

在1.2中我们提到时序约束就是为了使得建立时间余量和保持时间余量大于0,但是前文可知,Tskew、Tsu、Tco和Th无法控制,为寄存器的特性参数,Tskew一般可以认为是0。就只剩下T和Tdata。前文提到过保持时间余量一般(不是绝对的)没有问题,主要是建立时间余量。所以时序约束的目的就是控制布局和布线尽量减少Tdata,同时还需修改设计即HDL代码减少组合逻辑延迟即综合。如果代码无法继续优化而布局布线也无法继续优化,减少Tdata,那么只有增大T才能使得建立时间余量满足要求,即降低设计的运行时钟。