#计算机组成原理# chapter 4存储器 -4.2主存储器 part 2.1随机存取存储器

文章目录

- chapter 4 存储器

- 4.2 主存储器

- 4.2.3 随机存取存储器

chapter 4 存储器

4.2 主存储器

4.2.3 随机存取存储器

随机存取存儲器按其存储信息的原理不同,可分为静态RAM和动态RAM两大类。

1.静态RAM( Static RAM,SRAM)

(1)静态RAM基本单元电路

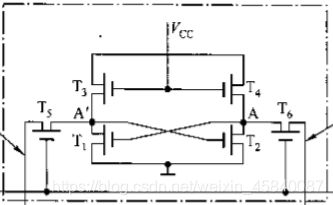

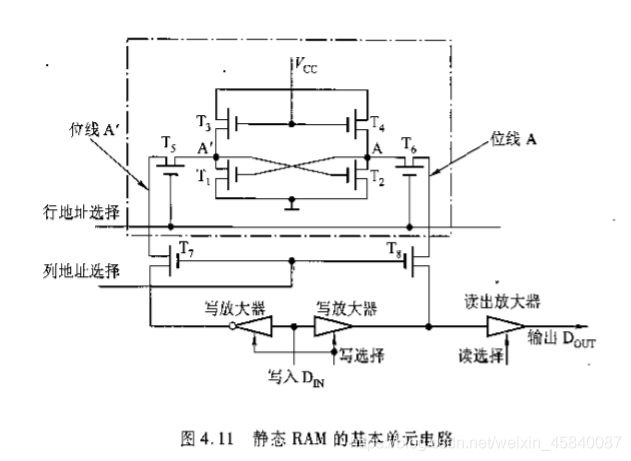

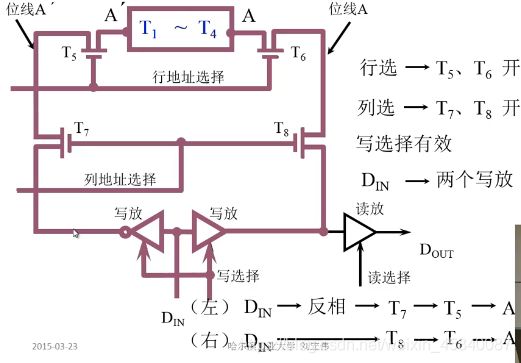

存储器中用于寄存“0”和“1”代码的电路称为存储器的基本单元电路,图4.1是一个由6个MOS管组成的基本单元电路。图中T1-T4是一个由MOS管组成的触发器基本电路,解决了用什么样的电路存放0,1。T5-T6犹如一个开关,受行地址选择信号控制,起到译码驱动作用。由T1~T6这6个MOS管共同构成一个基本单元电路。

T7,T8受列地址选择控制,分别与位线A’和A相连,它们并不包含在基本单元电路内,而是芯片内同一列的各个基本单元电路所共有的。就像下图一样。

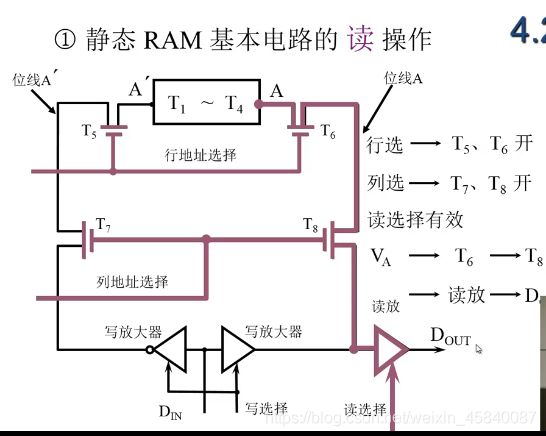

静态RAM基本电路的读操作

假设触发器已存有“1"信号,即A点为高电平。当需读出时,只要使行、列地址选择信号均有效,则T5,T6,T7,T8均导通,A点高电平通过T6后,再由位线A通过T8,作为读出放大器的输人信号,在读选择有效时,将“1”信号读出。

由于静态RAM是用触发器工作原理存储信息,因此即使信息读出后,它仍保持其原状态,不需要再生。但电源掉电时,原存信息丢失,故它属易失性半导体存储器。

静态RAM基本电路的写操作 写入时不论触发器原状态如何,只要将写人代码送至图的D(IN)端,在写选择有效时,经俩个写放大器,使两端输出为相反电平。当行、例地址选择有效时,使T5、T6、T7、T8导通,并将A与A’点置成完全相反的电平。这样,就把欲写入的信息写入到该基本单元电路中。如欲写入1,即D(IN)=1,经两个写放大器使位线A为高电平,位线A’为低电平,结果使A点为高,A’点为低,即写入了“1”信息。

写入时不论触发器原状态如何,只要将写人代码送至图的D(IN)端,在写选择有效时,经俩个写放大器,使两端输出为相反电平。当行、例地址选择有效时,使T5、T6、T7、T8导通,并将A与A’点置成完全相反的电平。这样,就把欲写入的信息写入到该基本单元电路中。如欲写入1,即D(IN)=1,经两个写放大器使位线A为高电平,位线A’为低电平,结果使A点为高,A’点为低,即写入了“1”信息。

(2) 静态RAM芯片举例

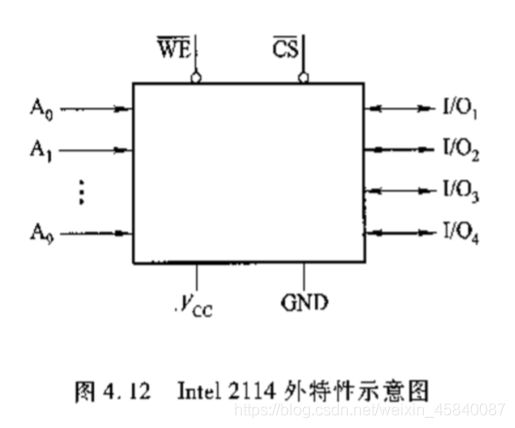

Intel2114芯片的基本单元电路由6个MOS管组成,图4.12是一个容量为1Kx4位的2114外特性示意图。

Intel2114芯片的基本单元电路由6个MOS管组成,图4.12是一个容量为1Kx4位的2114外特性示意图。

图中,A9到A0为地址输入端;I/O1~I/O4,为数据输入/输出端;CS为片选信号(低电平有效);WE为写允许信号(低电平为写,高电平为读);Vcc为电源端;GND为接地端。

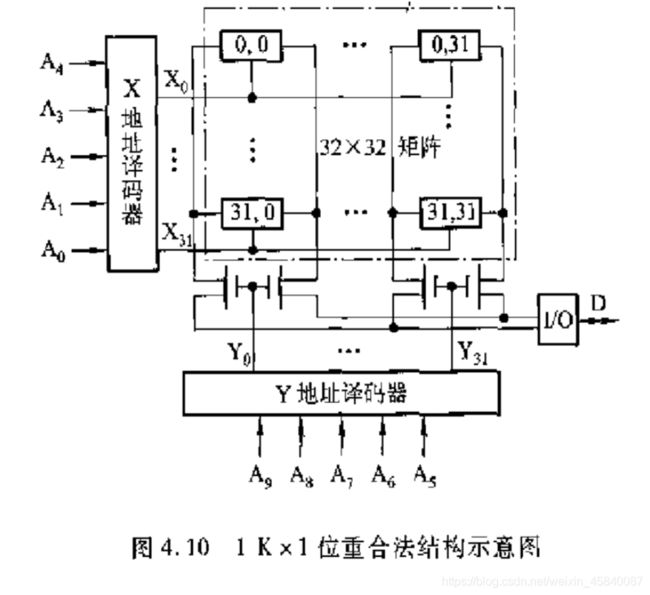

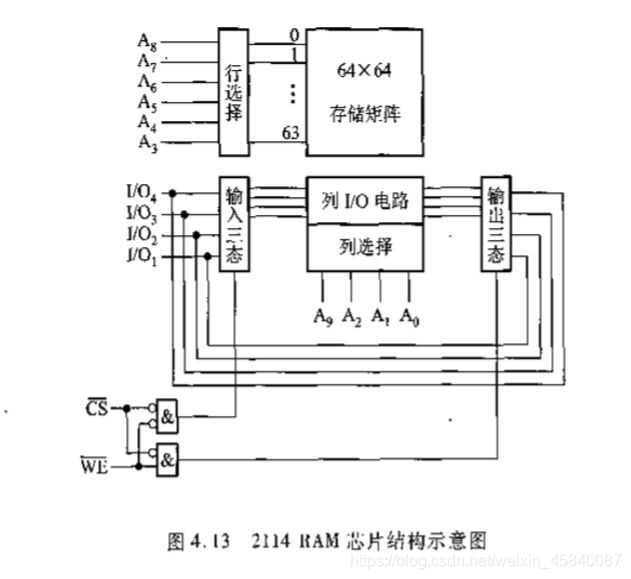

2114RAM芯片的结构示意图如图4.13所示。

图中存储矩阵由 64x64 个基本单元电路组成,列I/O电路即读/写电路。10根地址线分为行地址A8~A3和列地址A9、A2、A1、A0 ,4根数据线为I/O4-I/O1,它们是受输入/输出三态门控制的双向总线。当CS和WE均为低电平时,输人三态门打开,I/O4-I/O1上的数据即写入到指定地址单元中。当CS为低电平、WE为高电平时,输出三态门打开,列I/O电路的输出经片内总线输出至数据线I/O4-I/O1上。

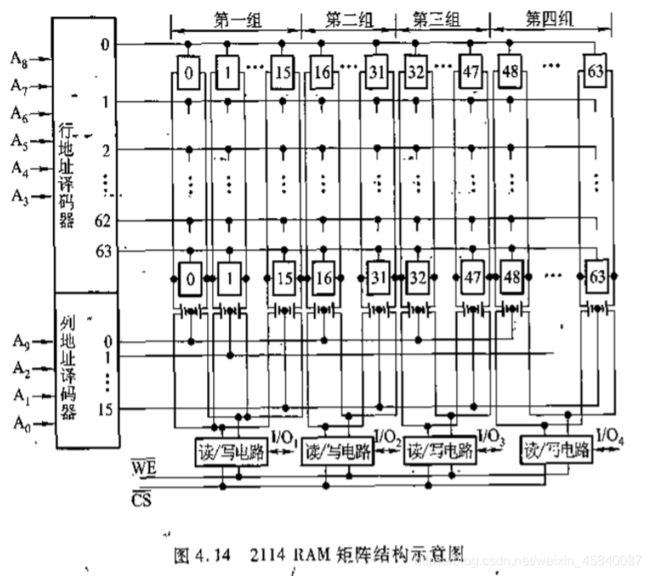

2114RAM芯片内的在储矩阵结构如图4.14所示。其中每一个小方块均为一个由6个MOS管组成的基本单元电路,排列成64x64矩阵,64列对应64对T7 T8管。又将64列分成4组,每包含16列,并与一个读/写电路相连,读/写电路受WE和CS控制,4个读/写电路对应4根数据线I/O1-I/O4。由图中可见,行地址经译码后可选中某一行;列地址经译码后可选中4组中的对应列,共4列。

当对某个基本单元电路进行读/写操作时,必须被行、列地址共同选中。例如,当A9–A0为全0时,对应行地址A8-A3为000000列地址A9、A2、A1、A0也为0000,第0行的第0,16,32,48这4个基本单元电路被选中。此刻,若做读操作,则CS为低电平,WE为高电平,在读写电

路的输出端I/O1-I/O4,便输出第0行的第0、16、32、48这4个基本单元电路所存的信息。若做写操作,将写入信息送至I/O1-I/O4端口,并使CS为低电平、WE为低电平,同样这4个输入信号将分别写入到第0行的第0、16,32、48这4个单元之中。

3)静态RAM读写时序

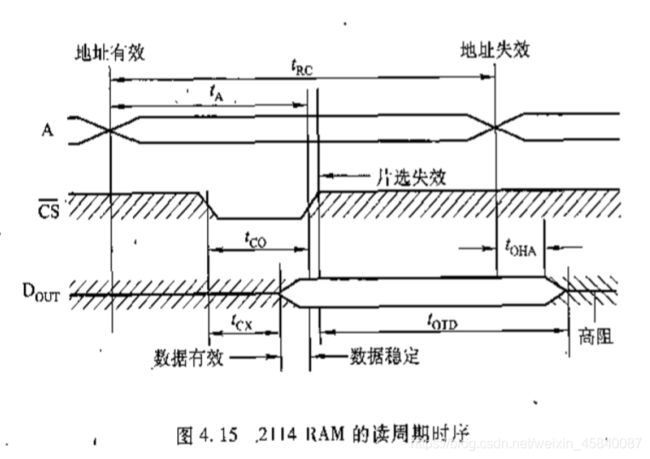

a.读周期时序

图4.15是2114RAM芯片读周期时序,在整个读周期中WE始终为高电平(故图中省略)。读周期tRC是指对芯片进行两次连续读操作的最小间隔时间。读时间tA表示从地址有效到数据稳定所需的时间,显然读时间小于读周期。图中tco是从片选有效到输出稳定的时间。可见只有当地址有效经tA后,且当片选有效经tco后,数据才能稳定输出,这两者必须同时只备。根据tA和tco的值,使可知当地址有效后,经tA-tco时间必须给出片选有效信号,否则信号不能出现在数据线上。

需注意一点,从片选失效到输出高阻需一段时间tOTD,故地址失效后,数据线上的有效数据有一段维持时间tOHA,以保证所读的数据可靠。

b.写周期时序

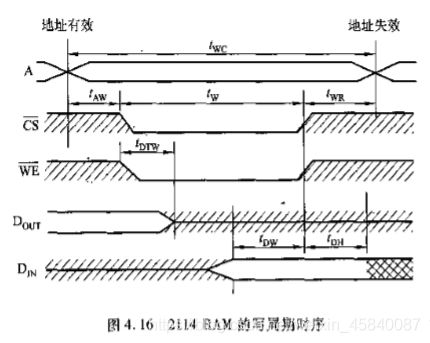

图4.16是2114RAM写周期时序。

写周期twc是对芯片进行连续两次写操作的最小间隔时间。写周期包括滞后时间tAW、写

入时间tW和写恢复时间tWR。在有效数据出现前,RAM的数据线上存在着前一时刻的数据

Dout(如图4.15所示的维持时间),故在地址线发生变化后,CS、WE均需滞后tAW再有效,以避免将无效数据写入到RAM的错误。但写允许WE失效后,地址必须保持一段时间,称为写恢复时间。此外,RAM数据线上的有效数据(即CPU送至RAM的写入数据Din)必须在CS、WE失效前的tDW时刻出现,并延续一段时间tDH(此刻地址线仍有效,tWR>tDH),以保数据可靠写入。

已制成的RAM芯片读写时序关系已被确定,因此,将它与CPU连接时,必须注意它们相互间的时序匹配关系,否则RAM将无法正常工作。其体RAM芯片的读/写周期时序可查看相关资料。

值得注意的是,不论是对存储器进行读操作还是写操作,在读周期和写周期内,地址线上的地址始终不变。