Advanced Microcontroller Bus Architecture, 即AMBA,是ARM公司提出的总线规范,被很多SoC设计所采用,常用的实现有AHB(Advanced High-Performance Bus)和APB(Advanced Peripheral Bus)。AHB用于高性能系统,APB用于低速外设。以下代码实例使用的是SystemVerilog描述。

(一)AHB总线信号接口:

包括AHB主设备,AHB从设备,AHB仲裁器等。

1 interface ahb_msr_intf #( 2 parameter AW = 32, 3 DW = 32 4 ) ( 5 input logic HCLK, 6 input logic HRESETn 7 ); 8 logic HGRANT; 9 logic HREADY; 10 HRESP_e HRESP; 11 logic [DW-1:0] HRDATA; 12 13 logic HBUSREQ; 14 logic HLOCK; 15 HTRANS_e HTRANS; 16 logic [AW-1:0] HADDR; 17 logic HWRITE; 18 HSIZE_e HSIZE; 19 HBURST_e HBURST; 20 HPROT_e HPROT; 21 logic [DW-1:0] HWDATA; 22 23 24 modport m ( 25 input HGRANT, HREADY, HRESP, HRDATA, 26 output HBUSREQ, HLOCK, HTRANS, HADDR, HWRITE, HSIZE, HBURST, HPROT, HWDATA 27 ); 28 29 modport s ( 30 input HBUSREQ, HLOCK, HTRANS, HADDR, HWRITE, HSIZE, HBURST, HPROT, HWDATA, 31 output HGRANT, HREADY, HRESP, HRDATA 32 ); 33 34 endinterface: ahb_msr_intf

以上为AHB主设备接口。

1 interface ahb_slv_intf #( 2 parameter AW = 32, 3 DW = 32 4 ) ( 5 input logic HCLK, 6 input logic HRESETn 7 ); 8 logic HSEL; 9 logic [AW-1:0] HADDR; 10 HTRANS_e HTRANS; 11 HSIZE_e HSIZE; 12 HBURST_e HBURST; 13 logic HWRITE; 14 HPROT_e HPROT; 15 logic [DW-1:0] HWDATA; 16 17 logic HREADY; 18 HRESP_e HRESP; 19 logic [DW-1:0] HRDATA; 20 21 22 modport m ( 23 input HREADY, HRESP, HRDATA, 24 output HSEL, HADDR, HTRANS, HSIZE, HBURST, HWRITE, HPROT, HWDATA 25 ); 26 27 modport s ( 28 input HSEL, HADDR, HTRANS, HSIZE, HBURST, HWRITE, HPROT, HWDATA, 29 output HREADY, HRESP, HRDATA 30 ); 31 32 endinterface: ahb_slv_intf

以上为AHB从设备接口。下面对信号进行一一说明。

HCLK 总线时钟

HRESETn 总线复位信号,低电平有效。

HADDR 地址总线,字节为单位。

HTRANS[1:0] 传输类型,具体如下:

1 typedef enum logic [1:0] { 2 HTRANS_IDLE = 2'b00, 3 HTRANS_BUSY = 2'b01, 4 HTRANS_NONSEQ = 2'b10, 5 HTRANS_SEQ = 2'b11 6 } HTRANS_e;

HWRITE 为高表示写传输,为低表示读传输。

HSIZE 传输大小,可能的取值定义如下:

1 typedef enum logic [2:0] { 2 HSIZE_BYTE = 3'b000, // 8bit 3 HSIZE_HALFWORD = 3'b001, // 16bit 4 HSIZE_WORD = 3'b010, // 32bit 5 HSIZE_DWORD = 3'b011, // 64bit 6 HSIZE_QWORD = 3'b100, // 128bit 7 HSIZE_OWORD = 3'b101, // 256bit 8 HSIZE_HWORD = 3'b110, // 512bit 9 HSIZE_TWORD = 3'b111 // 1024bit 10 } HSIZE_e;

HBURST 突发传输类型,突发传输模式可以为增量传输或者回环传输。

1 typedef enum logic [2:0] { 2 HBURST_SINGLE = 3'b000, 3 HBURST_INCR = 3'b001, 4 HBURST_WRAP4 = 3'b010, 5 HBURST_INCR4 = 3'b011, 6 HBURST_WRAP8 = 3'b100, 7 HBURST_INCR8 = 3'b101, 8 HBURST_WRAP16 = 3'b110, 9 HBURST_INCR16 = 3'b111 10 } HBURST_e;

HPROT 提供总线访问的附加信息并且主要是打算给那些希望执行某种保护级别的模块

使用的。这个信号指示当前传输是否为预取指或者数据传输,同时也表示传输是保护模式访问还是用户模式访问。对带存储器管理单元的总线主机而言这些信号也用来指示当前传输是高速缓存的(cache)还是缓冲的(buffer)。定义如下:

1 // cacheable | bufferable | privileged | data 2 // not-cacheable | not-bufferable | user | opcode 3 typedef enum logic [3:0] { 4 HPROT_NNUO = 4'b0000, 5 HPROT_NNUD = 4'b0001, 6 HPROT_NNPO = 4'b0010, 7 HPROT_NNPD = 4'b0011, 8 HPROT_NBUO = 4'b0100, 9 HPROT_NBUD = 4'b0101, 10 HPROT_NBPO = 4'b0110, 11 HPROT_NBPD = 4'b0111, 12 HPROT_CNUO = 4'b1000, 13 HPROT_CNUD = 4'b1001, 14 HPROT_CNPO = 4'b1010, 15 HPROT_CNPD = 4'b1011, 16 HPROT_CBUO = 4'b1100, 17 HPROT_CBUD = 4'b1101, 18 HPROT_CBPO = 4'b1110, 19 HPROT_CBPD = 4'b1111 20 } HPROT_e;

HWDATA 写数据。

HSELx 从机选择。

HRDATA 读数据。

HREADY 为高时表示总线传输完成。

HRESP 传输相应信号,表征传输状态,定义如下:

1 typedef enum logic [1:0] { 2 HRESP_OKAY = 2'b00, 3 HRESP_ERROR = 2'b01, 4 HRESP_RETRY = 2'b10, 5 HRESP_SPLIT = 2'b11 6 } HRESP_e;

HSPLITx 16位信号,指示仲裁器总线主设备应该被允许重试一个分块传输,每一位对应一个总线主机。

以下信号与仲裁器相关:

HBUSREQx 总线主设备x请求申请总线控制权。最多16个主设备。

HLOCKx 总线锁定请求,其他主设备无法或者仲裁器授权。

HGRANTx 表示当前主设备为优先级最高的主设备。

HMASTER 仲裁器信号表示正在执行传输或支持分块传输的从设备进行传输的主设备号。

HMASTLOCK 主设备正在执行一个锁定顺序的传输。

AHB 互联矩阵:

1 module ahb_matrix # ( 2 parameter WIDTH = 32, 3 NMSR = 4, 4 NSLV = 16 5 ) ( 6 input logic HCLK, 7 input logic HRESETn, 8 ahb_msr_intf.s ahbmv[NMSR], 9 ahb_slv_intf.m ahbsv[NSLV] 10 ); 11 12 localparam NMSRV = $clog2(NMSR), 13 NSLVV = $clog2(NSLV); 14 15 logic HBUSREQx[NMSR]; 16 logic HGRANTx[NMSR]; 17 logic HREADY; 18 HRESP_e HRESP; 19 logic [WIDTH-1:0] HRDATA; 20 21 logic HSEL[NSLV]; 22 logic [31:0] HADDR; 23 logic HWRITE; 24 HTRANS_e HTRANS; 25 HSIZE_e HSIZE; 26 HBURST_e HBURST; 27 HPROT_e HPROT; 28 logic [WIDTH-1:0] HWDATA; 29 30 logic [NMSRV-1:0] HMASTER, HMASTERd; 31 logic [NSLVV-1:0] HSLAVE, HSLAVEd; 32 logic errslv; 33 34 genvar i; 35 36 37 struct { 38 logic [WIDTH-1:0] HADDR [NMSR]; 39 logic HWRITE [NMSR]; 40 HTRANS_e HTRANS [NMSR]; 41 HSIZE_e HSIZE [NMSR]; 42 HBURST_e HBURST [NMSR]; 43 HPROT_e HPROT [NMSR]; 44 logic [WIDTH-1:0] HWDATA [NMSR]; 45 } ahbmd; 46 47 struct { 48 logic [WIDTH-1:0] HRDATA [NSLV]; 49 logic HREADY [NSLV]; 50 HRESP_e HRESP [NSLV]; 51 } ahbsd; 52 53 54 generate 55 for (i = 0; i < NSLV; i++) begin: ahbsv_loop 56 assign ahbsv[i].HSEL = HSEL[i]; 57 assign ahbsv[i].HADDR = HADDR; 58 assign ahbsv[i].HWRITE = HWRITE; 59 assign ahbsv[i].HTRANS = HTRANS; 60 assign ahbsv[i].HSIZE = HSIZE; 61 assign ahbsv[i].HBURST = HBURST; 62 assign ahbsv[i].HPROT = HPROT; 63 assign ahbsv[i].HWDATA = HWDATA; 64 end 65 endgenerate 66 67 generate 68 for (i = 0; i < NMSR; i++) begin: ahbmv_loop 69 assign HBUSREQx[i] = ahbmv[i].HBUSREQ; 70 assign ahbmv[i].HGRANT = HGRANTx[i]; 71 assign ahbmv[i].HREADY = HREADY; 72 assign ahbmv[i].HRESP = HRESP; 73 assign ahbmv[i].HRDATA = HRDATA; 74 end 75 endgenerate 76 77 generate 78 for (i = 0; i < NMSR; i++) begin: ahbmd_loop 79 assign ahbmd.HADDR[i] = ahbmv[i].HADDR; 80 assign ahbmd.HWRITE[i] = ahbmv[i].HWRITE; 81 assign ahbmd.HTRANS[i] = ahbmv[i].HTRANS; 82 assign ahbmd.HSIZE[i] = ahbmv[i].HSIZE; 83 assign ahbmd.HBURST[i] = ahbmv[i].HBURST; 84 assign ahbmd.HPROT[i] = ahbmv[i].HPROT; 85 assign ahbmd.HWDATA[i] = ahbmv[i].HWDATA; 86 end 87 endgenerate 88 89 assign HADDR = ahbmd.HADDR[HMASTER]; 90 assign HWRITE = ahbmd.HWRITE[HMASTER]; 91 assign HTRANS = ahbmd.HTRANS[HMASTER]; 92 assign HSIZE = ahbmd.HSIZE[HMASTER]; 93 assign HBURST = ahbmd.HBURST[HMASTER]; 94 assign HPROT = ahbmd.HPROT[HMASTER]; 95 assign HWDATA = ahbmd.HWDATA[HMASTERd]; 96 97 generate 98 for (i = 0; i < NSLV; i++) begin: ahbsd_loop 99 assign ahbsd.HRDATA[i] = ahbsv[i].HRDATA; 100 assign ahbsd.HREADY[i] = ahbsv[i].HREADY; 101 assign ahbsd.HRESP[i] = ahbsv[i].HRESP; 102 end 103 endgenerate 104 105 assign HRDATA = ahbsd.HRDATA[HSLAVEd]; 106 assign HREADY = errslv ? 1'b1 : ahbsd.HREADY[HSLAVEd]; 107 assign HRESP = errslv ? HRESP_OKAY : ahbsd.HRESP[HSLAVEd]; 108 109 110 always_ff @(posedge HCLK or negedge HRESETn) begin 111 if (!HRESETn) 112 HSLAVEd <= '0; 113 else if (HREADY) 114 HSLAVEd <= HSLAVE; 115 end 116 117 ahb_arbiter #( 118 .NMSR (NMSR) 119 ) ahb_arbiter ( 120 .HCLK (HCLK), 121 .HRESETn (HRESETn), 122 .HBUSREQx (HBUSREQx), 123 .HTRANS (HTRANS), 124 .HBURST (HBURST), 125 .HRESP (HRESP), 126 .HREADY (HREADY), 127 .HMASTER (HMASTER), 128 .HMASTERd (HMASTERd), 129 .HGRANTx (HGRANTx) 130 ); 131 132 ahb_decoder #( 133 .NSLV (NSLV) 134 ) ahb_decoder ( 135 .HADDR (HADDR), 136 .HSEL (HSEL), 137 .HSLAVE (HSLAVE), 138 .errslv (errslv) 139 ); 140 141 endmodule: ahb_matrix

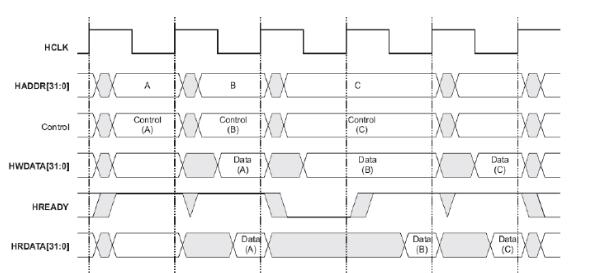

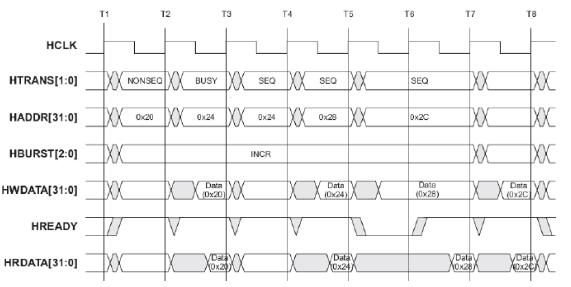

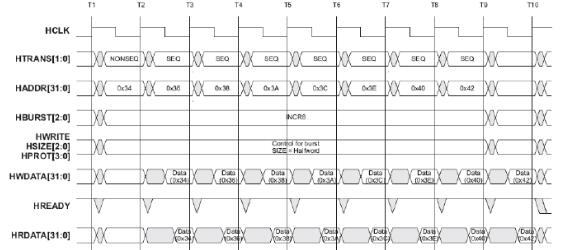

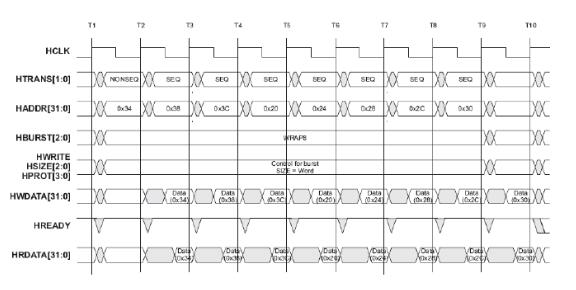

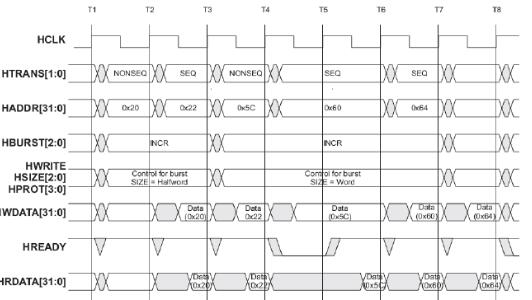

(二)AHB总线工作时序:

无须多言,看图。

基本传输模式

多重传输

使用传输类型

回环突发传输

未定义长度的增量突发传输