芯片边界效应

随着深亚微米工艺的发展,CMOS制造工艺对设计的影响也越来越大。在0.18um以前都可以忽略的工艺影响,在工艺一步一步发展的情形下,制造工艺所带来的影响变成了芯片设计中不可忽视的因素。本文诠释了制造工艺的两个重要效应:STI、WPE。通过对两种效应的分析,提出了在芯片设计阶段考虑它们的必要性。特别是针对IP模块级别的设计,本文给出了在电路设计阶段和版图设计阶段时,如何减小或者避免这两种效应的方法,并且分析和讨论这些方法的优缺点。

STI的概念

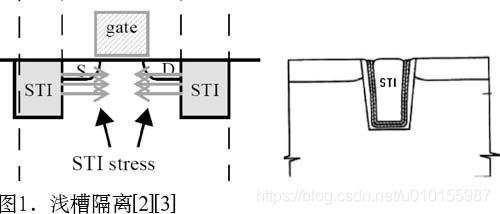

STI是Shallow Trench Isolation的缩写,STI压力效应就是浅槽隔离压力效应。在版图中通常为LOD(length of diffusion)

为了完成有源器件的隔离,在它周围必须形成绝缘侧壁,在较为先进的CMOS工艺制成中,通常用STI的方法来做隔离。浅槽隔离利用高度各向异性反应离子刻蚀在表面切出了一个几乎垂直的凹槽。该凹槽的侧壁被氧化,然后淀积多晶硅填满凹槽的剩余部分。

WPE的概念

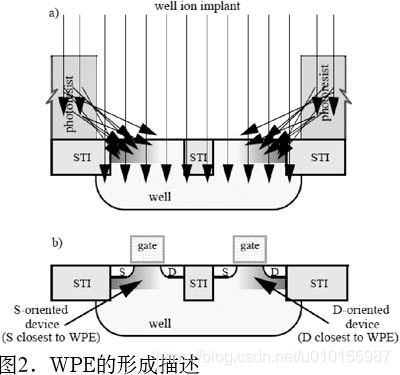

在离子注入制造工艺时,原子从掩模板的边沿开始扩散,在阱边附近的地方硅片表面变得密集,如图2所示。结果就是,阱表面浓度会随着距离掩模板的边沿的远近而有所不同,因此整个阱的掺杂浓度是不均匀的,如图2中的a)所示。这种不均匀造成MOS管阈值电压的不同,还有其它的电性能也有所不同,它会随着距离阱边距离的不同而不同,如图2中的b)所示。这种现象就是我们常说的阱邻近效应(WPE:Well Proximity Effect)。

设计中减小、避免STI、WPE效应的重要性

STI效应

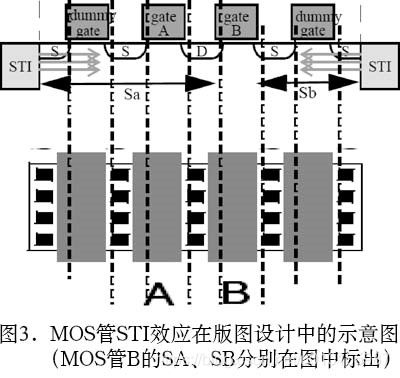

STI带来的压力对器件性能有重要影响,特别是电流Idsat和阈值电压Vth。而这些效应是非常重要的,在仿真器件性能的时候必须包含在内,而MOS管的特性与版图的设计又是息息相关的(图3)。

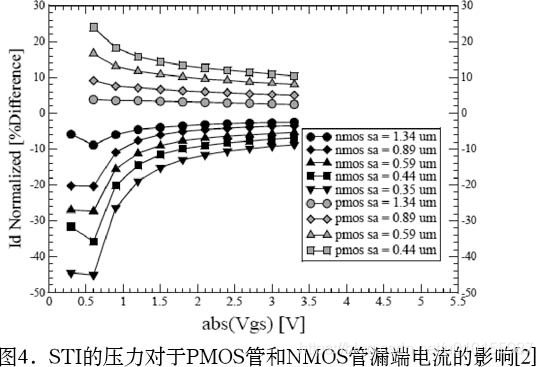

下面通过一组实验数据看看STI的压力对于MOS管漏端电流Ids的影响。横轴是不同的Vgs值(图4)。测试STI的压力对于PMOS管和NMOS管的漏端电流的影响。工艺是0.13um,PMOS管和NMOS管为3.3V,length=0.6um, width=24um,此处设置sa=sb。

我们可以看出,这种压力对于PMOS管和NMOS管的影响正好相反。PMOS管:电流随SA(SB)的增大而变小;NMOS管:电流随SA(SB)的增大而增大。

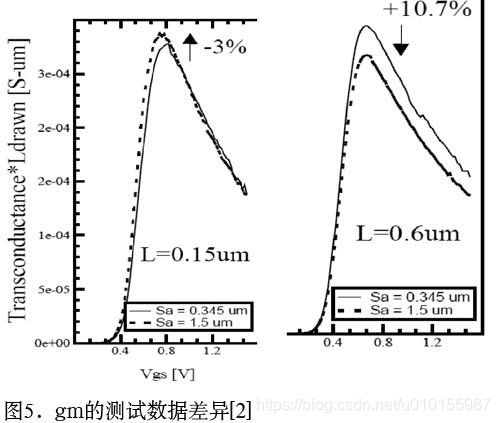

测试STI的压力对于gm的影响,横轴是不同的Vgs值(图5)。在Sa=Sb=0.345um,Sa=Sb=1.5um,两种条件下,对于一个length=0.15um的PMOS,相差约有3%,对于一个length=0.6um的PMOS,相差约有10%。而这些差异,仅仅是一个MOS的差异,对于数十个、数百个甚至与数千个MOS的组合会使电路偏差很大,有可能导致不工作。

WPE效应

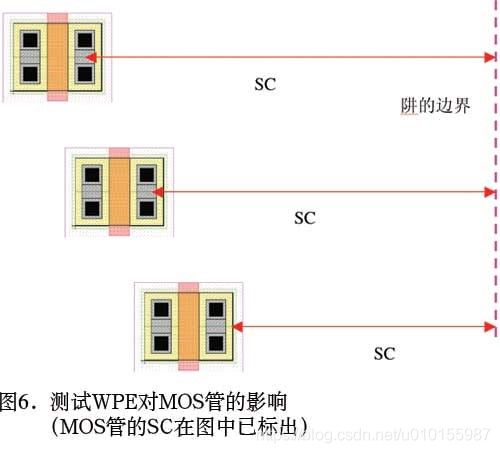

下面我们再来看看WPE的影响。对于同一个器件,固定的长宽,固定的源漏区(SA、SB)大小,根据将它放置在离阱边界距离不同的地方。

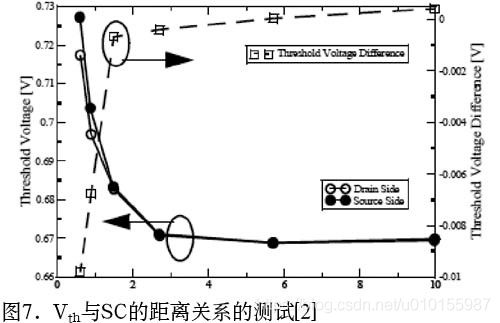

我们看到了下面的测试结果(图7):0.13um工艺下,测试3.3V NMOS管的Vth随SC的距离的变化:

我们可以看出,当NMOS管距离阱边比较近的时候,Vth会增大约50mV。Vth也会随着源漏端的方向而有所不同,达到约有10 mV的偏差。当NMOS管距离阱边比较远的时候,如SC的距离大于3um,Vth基本上就没有多少的偏差了。

通过一系列实验数据,我们可以看出,STI、WPE对器件性能有重要影响,在深亚微米IP模块设计中必须考虑的制造工艺的影响。那么,对IP模块级别的设计,如何减小或者避免这两种效应呢?

电路设计中如何减小STI、WPE的影响

在电路设计阶段,在版图设计没有进行或还没有完成时,我们并不能准确预测到完成后的版图会对电路带来怎样的影响。在这个阶段,我们如何尽量避免这些效应呢?在此,对于IP模块设计者给出几种方法可供参考。

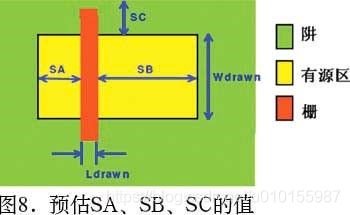

方法一:预先估计MOS管的SA、SB和SC的值,再进行仿真调试,进而达到理想的设计值。

根据制造工艺的设计规则要求,电路设计者可以预估常规MOS管的SA、SB和SC的值,从而较快的进行较为准确的电路设计。对于具有大驱动能力的MOS管,这种方法也很适用。但是由于预估的SA、SB和SC的值不会100%准确,所以会有少量的误差。

比如原始语句是:

******************************

.SUBCKT TOP Z A

M1 Z A IN VSS w= 2.000000 l=0.130000 m=2

……

.ENDS TOP

******************************

在前期仿真阶段,更具所选用的工艺制程所必须的设计规则,加入预估的SA、SB、SC的值(图8),语句如下:

******************************

.SUBCKT TOP Z A

M1 Z A IN VSS w= 2.000000 l=0.130000 m=2 sa=0.250000 sb=0.63000 sc=1.6000000….

……..

.ENDS TOP

******************************

方法二:预先放大或缩小MOS管。PMOS管的电流随SA/SB的增大而变小,所以可以预先放大PMOS管;NMOS管的电流随SA/SB的增大而增大,所以可以预先缩小NMOS管。这种作用类似于方法一,都是将WPE和STI效应在电路设计阶段就考虑进来,而不是等到版图完成之后才能调整。但这种方法对于比较有经验的设计者或者有实验数据的设计者来说才比较适用。

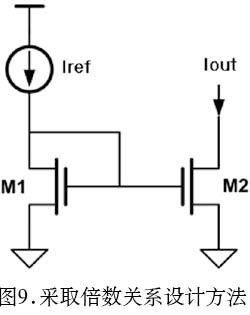

方法三:对于对称性要求比较高的电路(如电流镜、差分放大等),设计者应该尽量采取整数倍的设计方法,采用同样长度的管子,管子宽度的设计也尽量用倍数的关系。这种方法有助于提高管子制造出来之后的对称性。

举例,对于电流镜, 我们知道:

Iout = Iref * [(W/L) M2 / (W/L) M1]

如下图:

理论上,这种电路可以精确的复制电流而不受工艺和温度的影响,Iout与Iref的比值有器件尺寸的比率决定,但是实际上,管子之间的比率与WPE和STI效应息息相关。所以如选择M1管子为子单元,M2管子应为子单元的整数倍为好,在电路前期仿真阶段可以看到这种方法的优越性。

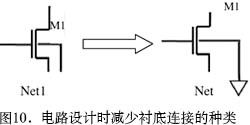

方法四:在不影响电路设计性能的情况下,尽量将PMOS管衬底连接电源,NMOS管衬底连接地,而不要到中间电平,可以减少阱的个数。

如图10所示,从电路设计阶段就减少衬底连接种类,有利于在版图设计时减少阱的个数,进而直接降低WPE以及STI对MOS管影响。

在上图中,在设计规格满足的情况下,我们应该尽量采用将M1管的衬底连接到VSS,而不是连接到NET1的方法来进行设计,这样有助于在版图的布局优化。

方法五:在电路设计后期,即版图设计完成之后,进行版图寄生参数的提取,然后再进行电路仿真,即我们常说的后仿。

用HSPICE做电路仿真时,传统的BSIM3 SPICE Model并没有把WPE/STI效应估算进去,而BSIM4 Spice Model开始支持这些效应了,所以要仿真使用BSIM4的模型。目前,晶圆厂的先进制成都已经提供了这种模型给用户使用了。这种方法可以进行最为准确的设计,但是如果后仿之后才考虑所有版图因素的话,这样会造成设计循环次数较多。

前四种办法在版图设计没有完成时采用,可以有效地缩短设计周期,减少设计的循环次数。第五种方法,对于考虑WPE/STI效应更有效,但会需要较长的设计周期。随着工艺的越来越先进,后期仿真又是必不可少的,特别是对于精确的设计。

版图设计中如何减小STI、WPE的影响

版图设计是创建工程制图的精确的物理描述的过程,而这一物理描述遵守有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束[6]。版图设计之后得到的GDSII格式的数据将交给掩模厂进行掩模的制作,以至最终送到晶圆厂(代工厂)生产线上去做芯片的生产制造。所以可以说版图的设计与生产制造出来的芯片的有更为直接的关系,因而在版图设计阶段考虑制造工艺的影响至关重要。那么,版图设计中如何减小STI、WPE的影响呢?下面针对STI、WPE的影响提出了几个IP模块版图设计的要点:

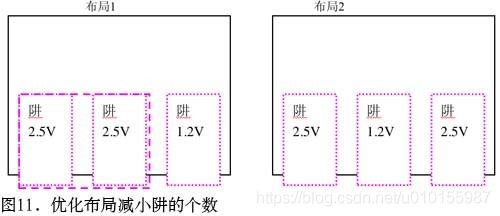

在版图布局规划阶段,优化阱的布局以减小阱的个数,比如将同一电位的器件放在一个阱里面,这样可以减小或避免WPE效应(图11)。

可以看出布局1比布局2有优势,因为相同的2.5V的阱可以进行合并,进而形成一个大的阱,受阱边界影响的MOS管的个数就会减少,WPE效应降低了,甚至几乎没有什么影响了。

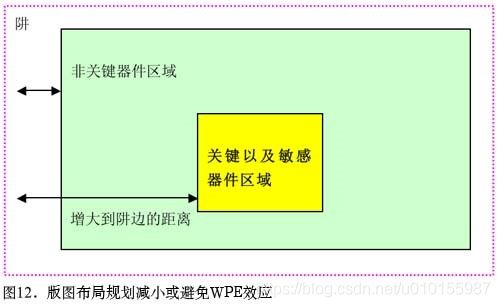

注意关键器件的布局,尽量将关键器件放置在离阱的边界比较远的地方,这样可以减小或避免WPE效应(图12)。

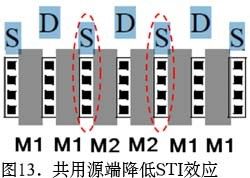

提高MOS管源、漏两端的可共用性,这样可以降低STI效应。如图13所示,将MOS管M1和M2实现源端的共用。

在有限的空间下,多加一些虚拟器件(Dummy device),这样就可以使关键器件远离阱的边缘,减小WPE;又可以增大MOS管源、漏两端的面积,从而降低STI效应(图14)。

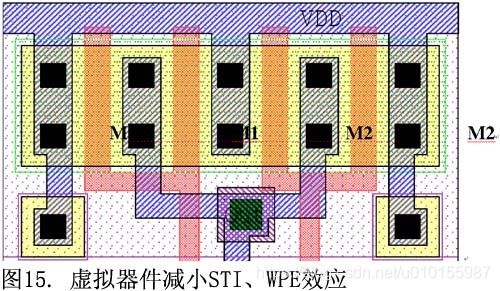

对于对称性要求比较高的电路(如电流镜、差分放大等),设计者应该尽量采取单元模块调用的设计方法。先作一个单元模块具有一定长度和宽度的管子,其它的管子都以这单元模块为单元进行重复调用,组成新的管子。这样,这些管子之间就会具有类似的特性,如SA、SB(STI效应)或者SC(WPE效应)的值。进行调用构建新的管子M1、M2,可以看出M1和M2具有类似的SA、SB、SC值(图15)。

STI、WPE是在深亚微米制造工艺时必须考虑的因素,特别是纳米级的制造工艺对器件有越来越重要的影响。如果不加以考虑,芯片会面临性能无法提高的影响,以至于会导致芯片无法工作。而在电路设计和版图设计中就融入这些因素,可以有效地缩短产品周期,降低生产成本。然而越来越多的工艺制作因素影响着IP模块的设计,这对于IP模块设计来说,更多的了解工艺变得非常重要。

以上效应中,WPE通过器件远离阱边缘来缓解,STI通过增加DUMMY器件来缓解。