【至简设计案例系列】基于FPGA的密码锁设计(altera版)

本文为明德扬原创及录用文章,转载请注明出处!

作者:秦红锴

一、项目背景概述

随着生活质量的不断提高,加强家庭防盗安全变得非常重要,但传统机械锁的构造过于简单,很容易被打开,从而降低了安全性。数字密码锁因为它的保密性很高,安全系数也非常高,再加上其不需要携带避免了丢失的可能,省去了因钥匙丢失而需要换锁的麻烦,受到了越来越多的人的欢迎。随看人们对高科技产品也越来越推崇,在当今社会科技的高度集中和创新,人们对日常生活中保护自身及财产安全的物品非常追捧,对其安全性的要求也非常的高。

为了达到人们对锁具安全性的高要求,加强锁具的安全保密性,用密码锁来取代传统机械锁的锁具是必然趋势。数字密码锁比传统机械锁具更加的安全 。

在本案例的设计过程中,应用了至简设计法、状态机模板应用等,在经过逐步改进、调试等一系列工作之后,最终达到了设计目标。

基于明德扬至简设计法和明德扬设计规范,设计一个基于FPGA的密码锁、并将数值显示在数码管上,然后根据输入的键值判断密码是否正确。

二、项目设计要求

1、通过矩阵键盘采样输入密码;

2、数码管显示输入的密码

3、密码正确,指示灯给出指示,不正确蜂鸣器给出报警

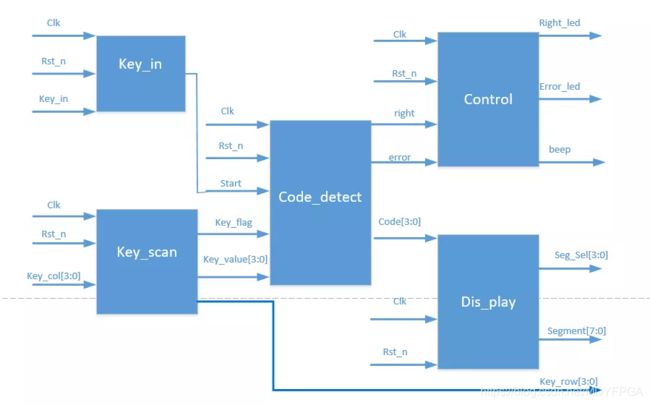

三、顶层接收设计

根据所有的功能要求,我们先对其进行结构划分如下:

Key_in:开始模块

Key_scan :按键扫描模块

Code_detect:密码比较模块

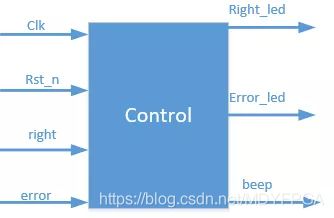

Control:控制信号模块

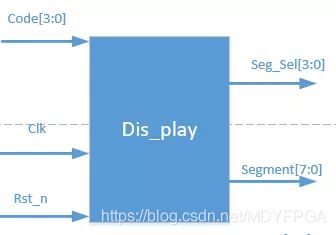

Dis_play:数码管显示模块

| Key_in | 比较按键输入 |

| Key_scan | 按键扫描,密码检测 |

| Code_detect | 负责密码的比较 |

| Dis_play | 数码管显示 |

| control | 负责输出LED,BEEP控制 |

矩阵按键模块

如果按键不多的话,我们可以直接按键与FPGA相连接,但是如果按键比较多的时候,如何还继续使用直接按键与FPGA相连接的话,所会大量增加FPGA端口的消耗,为了减少FPGA端口的消耗,我们可以把按键设计成矩阵的形式,就如下图所示:

| 信号名称 | I/O | 功能描述 |

|---|---|---|

| clk | I | 模块时钟 |

| rst_n | I | 模块复位 |

| key_col[3:0] | I | 列信号 |

| key_row[3:0] | O | 行信号 |

| Key_num | O | 键值 |

| Key_vld | O | 按键有效 |

由上图可以知道,矩阵键盘的行row(行)与col(列)的交点,都是通过一个按键来相连接。传统的一个按键一个端口的方法,若要实现16个按键,则需要16个端口,而现在这个矩阵键盘的设计,16个按键,仅仅需要8个端口,如果使用16个端口来做矩阵键盘的话,可以识别64个按键,端口的利用率远远比传统的设计好的多,所以如果需要的按键少的话,可以选择传统的按键设计,如果需要的按键比较多的话,可以采用这种矩阵键盘的设计。

而我们现在就以扫描法为例来介绍矩阵键盘的工作原理。

在进行键盘扫描时,应内部对信号进行按键消抖处理。

详细内容可以参考明德扬另一篇文章:矩阵键盘的检测。

| 信号名称 | I/O | 功能描述 |

|---|---|---|

| clk | I | 模块时钟 |

| rst_n | I | 模块复位 |

| key_falg | I | 按键按下标志信号 |

| key_value[3:0] | I | 按键值 |

| start | I | 开始比较 |

| error | O | 密码错误 |

| right | O | 密码正确 |

| code[3:0] | O | 输入密码 |

每次输入4位数的密码,所以每次按下一次,就将这词的键值先存到寄存器中。

| 信号名称 | I/O | 功能描述 |

|---|---|---|

| clk | I | 模块时钟 |

| rst_n | I | 模块复位 |

| error | I | 错误信号 |

| right | I | 正确信号 |

| beep | o | 蜂鸣器 |

| Error_led | o | 错误指示灯 |

| Right_led | o | 正确指示灯 |

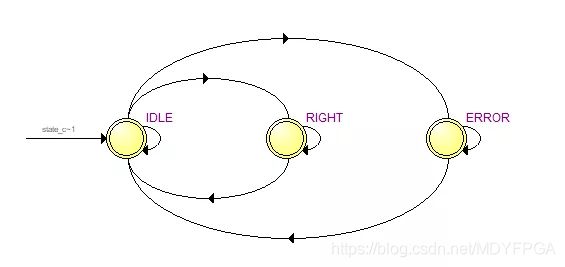

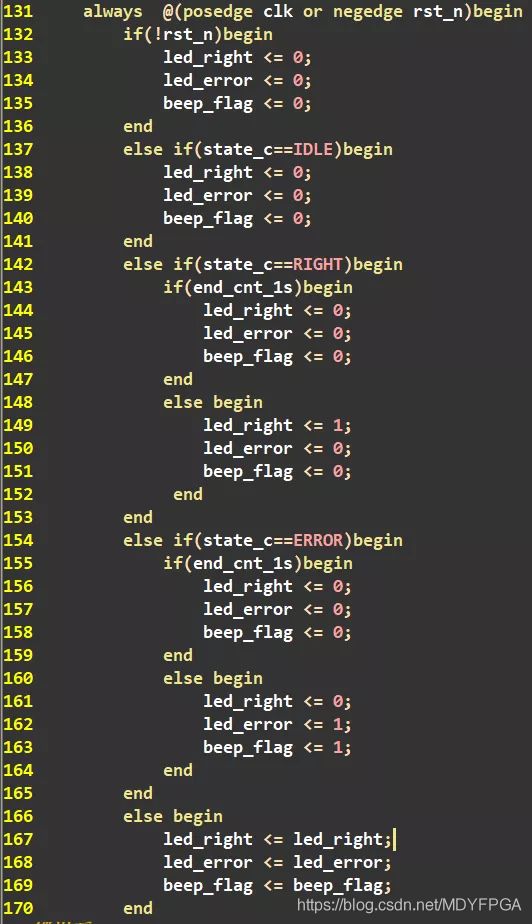

这个模块要操作的信号较多,并且每种情况下,各个指示灯的情况也不一样,为了设计的简单,我们在这采用一个状态机设计,每个状态下规定不同的操作就行了。

状态机的设计主要要有3个状态,主要是有空闲状态,正确状态,错误状态,状态转移图如下所示:

空闲状态:等待检测

正确状态:right_led亮

错误状态:error_led亮,并且BEEP叫1s;

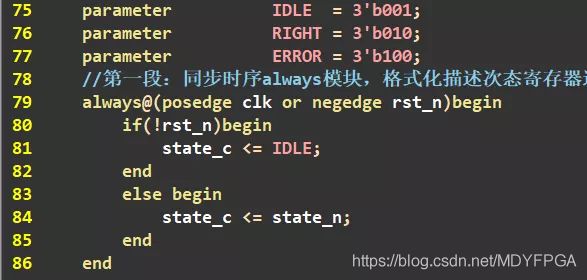

根据MDY的模板设计出4段状态机:

根据模板我们只需要修改很少的部分就可以,

1根据自己的状态图,修改所需要的状态转移条件

2修改状态发生变化的条件

3修改最后的输出信号

本次需要注意的是89行中的时钟条件被修改了,原因是,这几个状态中的灯亮或者蜂鸣器发出响声会持续一段时间,状态改变要等到每次小的状态结束,或者接收到新的上有信号。

| 信号名称 | I/O | 功能描述 |

|---|---|---|

| clk | I | 模块时钟 |

| rst_n | I | 模块复位 |

| Code[3:0] | I | 密码 |

| Seg_Sel[3:0] | O | 位选信号 |

| Segment[7:0] | O | 段选信号 |

数码管动态显示接口是应用最为广泛的一种显示方式之一,动态驱动是将所有数码管的 8 个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极 COM 增加位选通控制电路,位选通由各自独立的 I/O 线控制,当要输出字形码时,所有数码管都接收相同的字形码,但究竟是哪个数码管会显示出字形,取决于单片机对位选通 COM 端电路的控制,所以我们只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。

通过分时轮流控制各个数码管的的 COM 端,就使各个数码管轮流受控显示,这就是动态驱动。在轮流显示过程中,每位数码管的点亮时间为 1~2ms,由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感,动态显示的效果和静态显示是一样的,能够节省大量的 I/O 端口,而且功耗更低。

动态扫描是利用人眼视觉滞留的特点,点亮某一位后,在人眼反应之前,进行下一位的显示,故而出现重影现象。而人的视觉暂留时间大约在1/24秒左右,所以应该保持24帧以上才会保持连续而不会出现闪烁,通俗来讲,应该在一秒内至少扫描多次。也就是每次扫描时间至少小于40ms 。

相关代码可参考之前设计:“数字秒表”一文中。

四、实验总结:

事先在程序中设置内置密码为1111,当下载完成后输入4591,按下确认键之后,发现正确的灯不变化,蜂鸣器会响持续1s,重新输入1111后,正确的灯会先灭然后恢复,蜂鸣器也不发声,说明设计正确。