【FPGA】賽灵思FIFO内核的配置

想的是尽量每天更新一篇,前期先把常用内核配置简单总结一下。内核之后想再总结一下时许约束这部分。可能计划赶不上变化,今天先把FIFO说一下吧。关于FIFO常用的内核有几个细节,

1.关于DRAM和BRAM的区别在上篇转的文章里说过了,

2.还有一个就是关于异步FIFO需满和需空的问题:

参考http://xilinx.eetop.cn/viewthread-613258里提到的问题,感觉下面回答很值得参考,原问题是:

异步FIFO读时钟是写时钟的100倍,或者写是读的100倍会出现什么问题?

快慢时钟相差倍数并不是这个的问题根源。至于你说的快时钟到慢时钟,指针会漏掉,这是很正常的现象,但是漏掉指针如果导致FIFO功能出错,那就是你FIFO设计出错了。 异步FIFO需要保证空满信号及时报出,满了不要去写,空了不要去读。异步FIFO的空满由于异步传递延时的问题,只会出现提前报出虚空虚满的问题,而不会出现漏掉空满的问题。 满信号的产生是写时钟域下,当前周期写指针与两个写时钟周期前的读指针比较,如果判断满了,当下不会再写,但是读时钟域有可能在这两个周期有读动作,只会造成FIFO实际上被读出成非满状态,而此时即使报出满状态是没有关系的,这个时候就是虚满的状态。空状态与之类似,自己分析一下。 异步FIFO读写频率能不能相差百倍以上,自己写一个FIFO验证一下就完了,不要想当然觉得漏掉指针就一定有问题。

上面回答总结一下就是异步FIFO的读和写的时钟不同,若读时钟较快,则会导致FULL信号有效之后在下一个写时钟到来前,会读走一些数据,而此时FIFO为非满状态,但是写时钟还没到来,也就没有对读指针和写指针进行对比从而更改FLL信号状态,从而出现FULL信号有效而实际FIFO并没有满的情况,这种情况就是虚满。如果FIFO深度较浅而读时钟速度太快,感觉可能会导致FULL有效的同时EMPTY也有效,但是这种情况只会停留到写时钟到来前(最后这个情况纯属揣测,并没验证,对FIFO的认识不足,有待查看FIFO具体原理进行确认)。

虚空:虚空状态就是在写时钟比读时钟快的情况下产生的,例如EMPTY信号有效之后,表示此时FIFO为空,但是写时钟会在下一个读时钟到来前迅速的写FIFO进去一些数据,导致EMPTY有效而FIFO实际并不为空。这种情况就是虚空。

3.这个问题是我前几天遇到的,问题描述如下:

外部ADC采样数据和内部时钟不同步,采用异步FIFO解决该问题,这两个时钟的时钟树是同源的,而且都是200 M(如果两个时钟时钟树不同源,FIFO不适合长时间大量数据读取,因为时钟可能会有几Hz的偏差,导致FIFO空或者满),为了防止相位偏移产生亚稳态情况,用一个异步FIFO解决该问题。我设置的是只要FULL信号不有效就往里写,EMPTY信号不有效就读,结果就发现都出来的数据有随机性很强的噪点,最后发现是异步FIFO出现了亚稳态情况,也就是非空就读非满就写的情况导致我只写一个数据然后我就又只取一个数据,频繁的读写一位数据,导致了读出的数据有噪点,最后是加了一个可编程空解决的,判断可编程空实现的数据跨时钟域转换的。

------------------------------------下面说FIFO内核的配置----------------------------

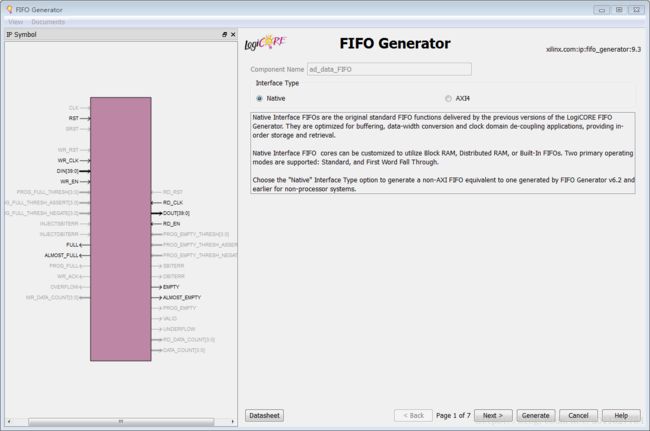

第一个界面

只有两个选项,native和AXI4,前者是纯粹的FIFO,后者是在FIFO上添加的一个AXI4的通信接口,其本质也是一个FIFO只不过穿了一个时髦的外套。据说用AXI4是一个趋势,emmmm我还是比较low还是先搞native吧

我就是看这个地方的DRAM BRAM SRegister之后找到了上篇博文并转了过来。read、write clock 这部分选项分两块,第一块就是上半部分的common clock这是单端同步FIFO,顾名思义就是只有一个参考时钟,读和写都是这个参考时钟,然后memory type 就是这四个选项的区别,也就是在实际综合的时候这个FIFO是要用那种资源去实现。(强烈推荐参考上篇博文)。下半部分就是异步FIFO了,异步FIFO不能用SRegister实现,所以这块就只有三个选项。另外再说一下为什么SRegister不能实现异步FIFO,因为SRegister是循环移位寄存器,也就是说本身这个寄存器只能接受一个同步时钟实现读和写,因此不能实现异步FIFO。

根据资源利用情况选择用哪种方式实现FIFO,然后就是pag3:

read mode两个选项,第一个就是普通的FIFO,当读使能有效时会在读时钟的上升沿进行读取DOUT上的数据,当读使能失效的时候,DOUT无数据。与FWFT模式的区别就在于后者的DOUT一直显示下一个数据的值,根据读使能和读时钟实现读指针的移位。

中间部分当使用build inFIFO时需要自己根据实际需要设定读时钟和写时钟的频率,而DRAM和BRAM则不需要预设,emmm数据手册还有一个小技巧说的是:

If the desired frequency is not within the allowable range, scale the read and write clock frequencies so that they fit within the valid range, while maintaining their ratio relationship.

也就是说如果要超频使用build in FIFO,预设的读写时钟要按比例预设。

下面就是write width 和write depth 、read width 和read depth。这个就不用多说了吧。

最下面的enable ECC(Error Correction Checking)就是使能自校准功能,反正我没用过,哈哈哈哈,据说会启动内部的编解码模块。

最后那个选项用不到就先不说了,用到的时候再看吧。

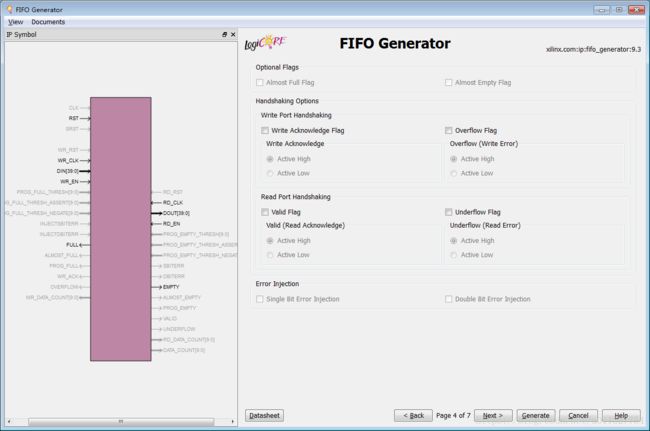

这一页最想面两个optional flags 应该直接翻译就知道了将满标志和将空标志。

中间的两个选项就是写有成功标志和溢出标志,下面两个选项就是可选的高有效还是地有效。

再往下就是都有效标志位和underflow标志位(读失败)也是可选的高有效还是低有效

这两个选项可以用来保证数据读写的准确性,哈哈哈哈这个我也没用到

再往下就是ECC的校验标志位的选择了。但是看数据手册也不太明白,说是在输入端插入一位或者两位信号,可能是有错误的时候用来在输出数据中表示错误的。不是很清楚,用到的时候再细看。

这一也前两个选项 一个是安装reset端口,另一个是使能同步reset。一般都选上就行了。

full flags rest value 就是重启之后full端口的值(一般full是高电平有效)

programmable flags 设置自设置的满和空 下面还有非满和非空,都是用户可以自己设定到多少时候认为满或者非满 这个感觉经常会用到,打个小星号**************

ok 这就差不多了dou这吧