- 浅谈C#之485通讯

CN.LG

C#网络

一、基本介绍C#中实现485通讯,通常指的是使用RS-485串行通信接口。RS-485是一种半双工通信标准,常用于工业环境中的设备之间的通信。二、简单示例打开串口:首先,你需要创建一个SerialPort对象,并设置其参数,如端口名、波特率、数据位、停止位和奇偶校验位。然后打开串口。SerialPortsp=newSerialPort();sp.PortName="COM1";//串口名称sp.B

- 嵌入式系统中的中断的使用和处理机制

TENET-

嵌入式嵌入式中断

文章目录1.概述2.中断请求3.中断响应4.保护现场5.中断服务6.恢复现场7.中断返回1.概述在嵌入式系统中,中断处理机制是确保系统实时响应外部事件的关键技术之一。嵌入式系统通常运行在资源受限的环境中,这意味着需要高效、快速地响应外部输入,如传感器数据、用户按键、通信接口信号等。中断处理使得处理器能够在执行主要任务的同时,及时响应这些外部事件,从而提高系统的实时性和可靠性。中断处理的基本原理是,

- 浅谈C#之232通讯

CN.LG

C#c#开发语言

一、基本介绍C#中实现232通讯,通常指的是通过串行通信接口(如RS232或RS485)与串行设备进行数据交换。以下是一个使用System.IO.Ports命名空间中的SerialPort类创建的基本示例。二、简单示例创建SerialPort实例:首先,你需要创建一个SerialPort对象,并设置其参数,如端口名、波特率、数据位、停止位和奇偶校验位。SerialPortserialPort=ne

- stm32通信方式-USART

打地基的小白

stm32嵌入式硬件单片机

一、通信目的数据传输:将数据从一个设备传送到另一个设备。这可以是在STM32微控制器之间或者STM32与另一类型的设备之间进行。系统扩展:通过通信接口连接更多的硬件模块,如传感器、执行器或其他微控制器,从而扩展系统的功能。远程控制:允许用户通过网络或无线通信远程控制设备。实时监控:通过通信接口收集来自传感器的数据,并将其传输到中央处理单元或其他监控设备进行分析。软件更新:通过通信接口进行固件或软件

- mpu6050

xiaoxiaoguoer6

stm32学习嵌入式硬件

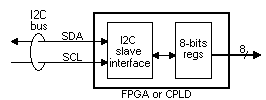

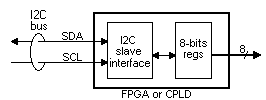

最小模块上有xcl和xda,那么这两个接口用来当作我们主机的i2c的通信接口,外接入的气压计或者磁力计,直接访问外拓的芯片的数据。AD0就是从机地址最低位INT就是中断信号输出

- 还在使用 RESTful API ? 试一试 GraphQL

zoe_ya

restfulgraphql后端

前言GraphQL和RESTfulAPI是两种不同的网络通信接口设计理念,它们都可以用于客户端和服务器之间的数据交换,但是有着不同的工作方式和特点。各自的特点以及优缺点GraphQL:特点:查询语言:GraphQL是一个查询语言,允许客户端精确地指定需要的数据结构。单一端点:与REST不同,GraphQL通常只使用一个端点来处理所有的数据请求。强类型系统:GraphQL服务定义了一套强类型的API

- 基于CUBEMX的HAL库串口通信实操代码

Zhaorming.

STM32单片机嵌入式硬件stm32

1、摘要芯片采用为RoboMaster开发板C型,型号STM32F407IGHx。使用了串口+DMA+中断,CUBEMX中展示通信配置以及部分注释内容都是互通的,代码大体框架可以用于其他芯片上,弄清框架即可列举例子:获取遥控器数据;获取处理视觉传输数据2、概念理论2.1串口串口(SerialPort)是一种通过串行传输数据的通信接口。常用于在计算机系统和外部设备之间进行数据传输,例如连接计算机与打

- ALINX黑金AXU3EGB 开发板用户手册RS485通信接口图示DI RO信号方向标识错误说明

电子阿板

fpga开发单片机智能硬件嵌入式硬件stm32

MAX3485这类RS485芯片,DI是TTL信号输入,RO是TTL信号输出如下图是MAX3485手册规格书。因此ALINX黑金AXU3EGB用户手册Page43页图3-11-1PL端485通信的连接示意图,MAX3485芯片的DIRO信号输入输出标识方向是错误的,应为蓝色箭头方向。(备注里面是对的)下图为AXU3EGB开发板用户手册相关内容至于为什么要提出来,因为很多人看原理图设计时大概率会先看

- ETCD 七 gRPC 通信接口以及客户端

wanghaichao1234

etcdetcddocker数据库

client/v3client定义//Clientprovidesandmanagesanetcdv3clientsession.typeClientstruct{Cluster//向集群里增加etcd服务端节点之类,属于管理员操作。KV//我们主要使用的功能,即操作K-V。Lease//租约相关操作,比如申请一个TTL=10秒的租约。Watcher//观察订阅,从而监听最新的数据变化。Auth/

- 【PCIE709-F】基于复旦微JFM7VX690T80 FPGA的全国产化8通道光纤双FMC接口数据处理平台

北京青翼科技

fpga开发

板卡概述PCIE709-F是一款基于上海复旦微电子的28nm7系列FPGAJFM7VX690T80的全国产化8通道光纤双FMC接口数据预处理平台,该板卡采用复旦微的高性能7系列FPGA作为实时处理器,实现4路10GSFP+光纤以及1路QSFP+通信接口、实现1路X8PCIE数据传输的功能。板载2组独立的64位DDR3SDRAM大容量缓存。板卡具有2个FMC+扩展接口,可以插不同的子板以实现不同的接

- SPI IIC UART接口的区别和各自收发数据的方法

Cuit小唐

嵌入式面试刷题单片机相关单片机嵌入式硬件

SPI、I2C和UART是三种不同的串行通信接口,它们在数据传输方式、速度、拓扑结构等方面存在差异。SPI(SerialPeripheralInterface,串行外设接口):全双⼯,四根线优点:⾼速缺点:没有指定流控制器,没有应答机制确认是否收到数据MISO:主设备数据输入,从设备数据输出MOSI:主设备数据输出,从设备数据出入SCLK:时钟信号,由主设备产⽣CS:从设备使能信号,由主设备控制I

- 智能门锁代码实现之连接硬件的步骤

selenia8860

物联网嵌入式硬件stm32

准备硬件和开发环境:确保你拥有所需的硬件(如微控制器、门锁控制电路、通信接口等),并设置好C语言的开发环境。对于Arduino等开源硬件平台,你可能需要安装特定的IDE(集成开发环境)和驱动程序。编写代码:使用C语言编写智能门锁的逻辑代码。在这个阶段,你需要根据硬件平台的接口文档来编写与硬件通信的代码。在上面的示例中,我们使用了简单的串口通信来模拟数据的读取和写入。实际应用中,你可能需要使用特定的

- 【51单片机】DS18B20(江科大)

2302_80796399

51单片机嵌入式硬件c语言

一、DS18B20温度传感器1.DS18B20介绍·DS18B20是一种常见的数字温度传感器,其控制命令和数据都是以数字信号的方式输入输出,相比较于模拟温度传感器,具有功能强大、硬件简单、易扩展、抗干扰性强等特点·测温范围:-55℃到+125℃·通信接口:1-Wire(单总线)·其它特征:可形成总线结构、内置温度报警功能、可寄生供电2.引脚及应用电路本开发板原理图如图:本开发板的IO口已经外接了一

- 【嵌入式开发】49

少年郎123456

单片机stm32嵌入式硬件

【嵌入式开发】分频的基本概念**分频(FrequencyDivision)**指的是将一个较高的频率信号通过某种方式转变为一个或多个较低频率信号的过程。在嵌入式系统中,分频通常用于产生各种所需的时钟信号,这些信号用于驱动不同的硬件模块,如CPU、外设、通信接口等。分频的作用时钟管理:嵌入式系统中的各种组件和设备通常需要不同频率的时钟信号。通过分频,可以从一个主时钟源生成多个不同频率的时钟,以满足各

- ros2学习笔记-通信接口

守护安静星空

linux软件工程学习c++系统架构1024程序员节

目录1.ros2接口描述2.ros2接口定义3.ROS2接口常用的命令行指令4.测试自定义接口1.ros2接口描述ros2节点之间通讯一般使用std_msgs/下的标准数据类型,当我们要定义自己的消息类型的时候,需要定义通讯接口(数据类型)文件。自定义的通讯数据类型可以用已有的通讯数据类型进行组装,也可以使用ros2规定的原始数据类型组装。已有的通讯接口定义可以使用ros2的命令查看:ros2in

- 基于Robei EDA--实现串口通信

悲喜自渡721

fpga开发

一、串口简介串口作为常用的三大低速总线(UART、SPI、IIC)之一,在设计众多通信接口和调试时占有重要地位。但UART和SPI、IIC不同的是,它是异步通信接口,异步通信中的接收方并不知道数据什么时候会到达,所以双方收发端都要有各自的时钟,在数据传输过程中是不需要时钟的,发送方发送的时间间隔可以不均匀,接受方是在数据的起始位和停止位的帮助下实现信息同步的。而SPI、IIC是同步通信接口(后面的

- 嵌入式Linux开发---RS485通信驱动硬件编程

牛马大师兄

嵌入式Linux经验教程linux嵌入式硬件arm开发驱动开发mcu物联网

提醒:RS485的使用与UART串口的使用基本相同,差别在于使用485时需要手动切换485芯片的收发引脚模式。Linux驱动RS485通信的程序源码Demo见文末。1、RS485基础铺垫智能仪表随着80年代初单片机技术的成熟而发展起来,世界仪表市场基本被智能仪表所垄断,这归结于企业信息化的需要,而企业在仪表选型时其中的一个必要条件就是要具有联网通信接口。最初是数据模拟信号输出简单过程量,后来仪表接

- 【STM32+HAL库+CubeMX】UART轮询收发、中断收发、DMA收发方法及空闲中断详解

Amonter

RTOSstm32嵌入式硬件单片机

(转载)原文链接:https://blog.csdn.net/qq_39344192/article/details/1314707351.什么是UART?UART是一种异步串行通信接口,常用于通过串口与外部设备进行通信。它通过发送和接收数据帧来实现数据传输,使用起来相对简单。UART通常包含发送器(Transmitter)和接收器(Receiver),通过两根信号线(传输线)进行双向通信。2.U

- 串口通信原理详解

wespten

C语言汇编通用操作系统与嵌入式系统开发硬件驱动开发硬件工程

串行接口简称串口,也称串行通信接口(通常指COM接口),是采用串行通信方式的扩展接口。串行通讯的特点是:数据是按位(bit)逐位依次传输的,只需一根传输线即可完成单向传输通信;如果有一对传输线就可以实现双向全双工通信(可以直接利用电话线作为传输线),从而大大降低了成本,特别适用于远距离通信,但传送速度较慢;1、串口划分标准串行接口按时钟同步方式不同,可以分为同步串行接口与异步串行接口。同步串行通信

- 串行通信原理

AB_Est

stm32单片机arm

串行通信原理通信接口背景知识并行通信串行通信三种传输方式通信方式STM32串口通信基础UART:通用异步收发器UART异步通信的特点UART异步通信方式引脚通信接口背景知识并行通信传输原理:数据各个位同时传输;优点:速度快;缺点:占用引脚资源多;串行通信传输原理:数据按位顺序传输;优点:占用引脚资源少;缺点:速度慢;三种传输方式1、单工2、半双工3、全双工通信方式1、同步通信:带时钟同步信号传输。

- 单片机学习笔记---串口通信(1)

Vera一笔画人生~

51单片机学习笔记单片机嵌入式硬件笔记学习c++开发语言

目录通信的基本概念通信的方式1.按照数据传送的方式,可分为串行通信和并行通信。1.1串行通信1.2并行通信2.按照通信的数据同步方式,又可以分为异步通信和同步通信。2.1异步通信2.2同步通信3.按照数据的传输方向,又可以分为单工通信,半双工通信,还有全双工通信。3.1单工通信3.2半双工通信3.3全双工通信4.总线通信速率串口通信简介串口通信串口接口标准和接口种类接口标准接口种类常见通信接口接口

- IEC 61850 学习笔记

金士顿

iec61850

一.GOOSE:面向通用对象的变电站事件;二.IEC61850:建立统一的,面向对象的层次化信息模型,实现设备的自我描述,以适应自动化功能的扩展,满足应用开放互操作需求,使得不同的厂商,不同类型的IED设备能够实现互操作;三.三层通信接口模型:变电站层、间隔层、过程层;四.IEC61850标准提供三类通信服务来满足三层结构的新型变电站需求,既Client-Server类的通信服务完成监控层与间隔层

- chatgpt赋能python:Python控制COM口的方法

turensu

ChatGptchatgptpython开发语言计算机

Python控制COM口的方法什么是COM口?COM口是串行通信接口的一种,是计算机硬件上针对串口使用的接口,常用于数据传输。在过去的几十年里,串口一直是计算机通信的重要手段之一。Python控制COM口的意义在实际应用中,我们需要经常控制硬件设备,比如说打印机、机械手臂等,这些设备通常需要通过COM口进行控制。Python提供了一种简单易用的方法,允许我们通过COM口控制这些设备。Python的

- 【嵌入式】基于STC89C52RC的51单片机学习(六)——串口

qq_51392613

51单片机学习嵌入式硬件

一、串口的基本认识串口是串型通信接口的简称,也叫串行通信接口或者串行通讯接口,是设备间接线通信的一种方式。特点:(1)串行接口是指数据一位位地顺序传送,其特点是线路简单,只要一对传输线就可以实现双向通信(可以直接利用电话线作为传输线),从而大大降低了成本,特别适用于远距离通信,但传输速度较慢。(2)双向通信,全双工。二、关于电器标准和协议串行接口按电气标准及协议来分包括RS-232-C、RS-42

- 【Iot】什么是串口?什么是串口通信?串口通信(串口通讯)原理,常见的串口通信方式有哪些?

卸载引擎

iot物联网单片机前端

串口通信原理1.串口2.串口通信4.波特率与比特率5.帧格式3.串口通讯的通讯协议3.1.RS2323.2.RS485总结1.串口串行接口简称串口,也称串行通信接口或串行通讯接口(通常指COM接口),是采用串行通信方式的扩展接口。串口可以将接收来自CPU的并行数据字符转换为连续的串行数据流发送出去,同时可将接收的串行数据流转换为并行的数据字符供给CPU的器件。一般完成这种功能的电路,我们称为串行接

- STM32微控制器 | 复习六 | USART原理及应用

阿牛哥dd

一、通信协议的定义通信是指通信双方的一种约定,包括对数据格式、同步方式、传送速度、传送步骤、检纠错方式等问题作出统一规定。也称通信控制规程。二、串行通信和并行通信的优缺点并行通信:传输原理:数据各个位同时传输。优点:速度快缺点:占用引脚资源多串行通信:传输原理:数据按位顺序传输。优点:占用引脚资源少缺点:速度相对较慢三、串行通信的通信方式同步通信:带时钟同步信号传输。(SPI、IIC通信接口)异步

- 电机驱控芯片:TMC5160介绍与使用

卓联微-李

驱动开发硬件工程嵌入式硬件自动化

介绍:TMC5160是带串行通信接口的高功率步进电机控制驱动芯片,将实现自动目标定位的灵活斜坡发生器和业界最先进的步进电机驱动器结合在一起。配合外置的功率晶体管,实现高动态、高扭矩电机驱动。TRINAMICs先进的SpreadCycle和StealthChop斩波器,驱动器可绝对无噪音的运行,并实现最大效率和最佳电机扭矩控制。高集成度、高能效和小外形尺寸使系统小型化和性能扩展可行,从而实现经济高效

- 3.2 嵌入式多媒体卡 eMMC Embedded MultiMedia Card

文可明志

第3章高速总线基本知识硬件架构

3.2嵌入式多媒体卡eMMCEmbeddedMultiMediaCard1eMMC/SD是什么?2SD卡有哪些种类?2.1按照大小尺寸分类2.2按照容量大小分类2.3按照通信接口分类2.4按照支持电压不同分类3关于存储卡UHS-I、UHS-II、UHS-III总线标准4UHS-I卡的工作模式/类型/上电时序命令5Layout注意事项5.1eMMCLayout注意事项5.2SD卡连接器Layout注

- STM32入门教程---USART串口协议

石原里美老公

STM32新手学习stm32嵌入式硬件单片机

文章目录通信接口串口通信简介硬件电路电平标准串口参数及时序串口时序USART外设简介USART框图引脚定义表USART基本结构数据帧字长设置配置停止位起始位侦测数据采样波特率发生器数据模式代码串口发送接线图代码思路库函数代码串口发送+接收接线图代码总结通信接口通信的目的:将一个设备的数据传送到另一个设备,扩展硬件系统;通信协议:制定通信的规则,通信双方按照协议规则进行数据收发;TX是数据发送脚,R

- PLC网关的重要性

蓝蜂物联网

物联网

PLC网关的重要性可编程逻辑控制器(PLC)作为现代工业自动化领域的核心设备,广泛应用于各种自动化控制系统。随着工业物联网(IIoT)技术的发展,PLC网关成为了连接传统PLC系统和现代工业物联网的关键组件。一、PLC网关简介PLC网关是一种能够连接PLC设备和物联网系统的硬件设备。它一方面提供与PLC设备的通信接口,另一方面具备联网功能,能够将PLC设备的数据上传到物联网云平台,实现设备的远程监

- 继之前的线程循环加到窗口中运行

3213213333332132

javathreadJFrameJPanel

之前写了有关java线程的循环执行和结束,因为想制作成exe文件,想把执行的效果加到窗口上,所以就结合了JFrame和JPanel写了这个程序,这里直接贴出代码,在窗口上运行的效果下面有附图。

package thread;

import java.awt.Graphics;

import java.text.SimpleDateFormat;

import java.util

- linux 常用命令

BlueSkator

linux命令

1.grep

相信这个命令可以说是大家最常用的命令之一了。尤其是查询生产环境的日志,这个命令绝对是必不可少的。

但之前总是习惯于使用 (grep -n 关键字 文件名 )查出关键字以及该关键字所在的行数,然后再用 (sed -n '100,200p' 文件名),去查出该关键字之后的日志内容。

但其实还有更简便的办法,就是用(grep -B n、-A n、-C n 关键

- php heredoc原文档和nowdoc语法

dcj3sjt126com

PHPheredocnowdoc

<!doctype html>

<html lang="en">

<head>

<meta charset="utf-8">

<title>Current To-Do List</title>

</head>

<body>

<?

- overflow的属性

周华华

JavaScript

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/1999/xhtml&q

- 《我所了解的Java》——总体目录

g21121

java

准备用一年左右时间写一个系列的文章《我所了解的Java》,目录及内容会不断完善及调整。

在编写相关内容时难免出现笔误、代码无法执行、名词理解错误等,请大家及时指出,我会第一时间更正。

&n

- [简单]docx4j常用方法小结

53873039oycg

docx

本代码基于docx4j-3.2.0,在office word 2007上测试通过。代码如下:

import java.io.File;

import java.io.FileInputStream;

import ja

- Spring配置学习

云端月影

spring配置

首先来看一个标准的Spring配置文件 applicationContext.xml

<?xml version="1.0" encoding="UTF-8"?>

<beans xmlns="http://www.springframework.org/schema/beans"

xmlns:xsi=&q

- Java新手入门的30个基本概念三

aijuans

java新手java 入门

17.Java中的每一个类都是从Object类扩展而来的。 18.object类中的equal和toString方法。 equal用于测试一个对象是否同另一个对象相等。 toString返回一个代表该对象的字符串,几乎每一个类都会重载该方法,以便返回当前状态的正确表示.(toString 方法是一个很重要的方法) 19.通用编程:任何类类型的所有值都可以同object类性的变量来代替。

- 《2008 IBM Rational 软件开发高峰论坛会议》小记

antonyup_2006

软件测试敏捷开发项目管理IBM活动

我一直想写些总结,用于交流和备忘,然都没提笔,今以一篇参加活动的感受小记开个头,呵呵!

其实参加《2008 IBM Rational 软件开发高峰论坛会议》是9月4号,那天刚好调休.但接着项目颇为忙,所以今天在中秋佳节的假期里整理了下.

参加这次活动是一个朋友给的一个邀请书,才知道有这样的一个活动,虽然现在项目暂时没用到IBM的解决方案,但觉的参与这样一个活动可以拓宽下视野和相关知识.

- PL/SQL的过程编程,异常,声明变量,PL/SQL块

百合不是茶

PL/SQL的过程编程异常PL/SQL块声明变量

PL/SQL;

过程;

符号;

变量;

PL/SQL块;

输出;

异常;

PL/SQL 是过程语言(Procedural Language)与结构化查询语言(SQL)结合而成的编程语言PL/SQL 是对 SQL 的扩展,sql的执行时每次都要写操作

- Mockito(三)--完整功能介绍

bijian1013

持续集成mockito单元测试

mockito官网:http://code.google.com/p/mockito/,打开documentation可以看到官方最新的文档资料。

一.使用mockito验证行为

//首先要import Mockito

import static org.mockito.Mockito.*;

//mo

- 精通Oracle10编程SQL(8)使用复合数据类型

bijian1013

oracle数据库plsql

/*

*使用复合数据类型

*/

--PL/SQL记录

--定义PL/SQL记录

--自定义PL/SQL记录

DECLARE

TYPE emp_record_type IS RECORD(

name emp.ename%TYPE,

salary emp.sal%TYPE,

dno emp.deptno%TYPE

);

emp_

- 【Linux常用命令一】grep命令

bit1129

Linux常用命令

grep命令格式

grep [option] pattern [file-list]

grep命令用于在指定的文件(一个或者多个,file-list)中查找包含模式串(pattern)的行,[option]用于控制grep命令的查找方式。

pattern可以是普通字符串,也可以是正则表达式,当查找的字符串包含正则表达式字符或者特

- mybatis3入门学习笔记

白糖_

sqlibatisqqjdbc配置管理

MyBatis 的前身就是iBatis,是一个数据持久层(ORM)框架。 MyBatis 是支持普通 SQL 查询,存储过程和高级映射的优秀持久层框架。MyBatis对JDBC进行了一次很浅的封装。

以前也学过iBatis,因为MyBatis是iBatis的升级版本,最初以为改动应该不大,实际结果是MyBatis对配置文件进行了一些大的改动,使整个框架更加方便人性化。

- Linux 命令神器:lsof 入门

ronin47

lsof

lsof是系统管理/安全的尤伯工具。我大多数时候用它来从系统获得与网络连接相关的信息,但那只是这个强大而又鲜为人知的应用的第一步。将这个工具称之为lsof真实名副其实,因为它是指“列出打开文件(lists openfiles)”。而有一点要切记,在Unix中一切(包括网络套接口)都是文件。

有趣的是,lsof也是有着最多

- java实现两个大数相加,可能存在溢出。

bylijinnan

java实现

import java.math.BigInteger;

import java.util.regex.Matcher;

import java.util.regex.Pattern;

public class BigIntegerAddition {

/**

* 题目:java实现两个大数相加,可能存在溢出。

* 如123456789 + 987654321

- Kettle学习资料分享,附大神用Kettle的一套流程完成对整个数据库迁移方法

Kai_Ge

Kettle

Kettle学习资料分享

Kettle 3.2 使用说明书

目录

概述..........................................................................................................................................7

1.Kettle 资源库管

- [货币与金融]钢之炼金术士

comsci

金融

自古以来,都有一些人在从事炼金术的工作.........但是很少有成功的

那么随着人类在理论物理和工程物理上面取得的一些突破性进展......

炼金术这个古老

- Toast原来也可以多样化

dai_lm

androidtoast

Style 1: 默认

Toast def = Toast.makeText(this, "default", Toast.LENGTH_SHORT);

def.show();

Style 2: 顶部显示

Toast top = Toast.makeText(this, "top", Toast.LENGTH_SHORT);

t

- java数据计算的几种解决方法3

datamachine

javahadoopibatisr-languer

4、iBatis

简单敏捷因此强大的数据计算层。和Hibernate不同,它鼓励写SQL,所以学习成本最低。同时它用最小的代价实现了计算脚本和JAVA代码的解耦,只用20%的代价就实现了hibernate 80%的功能,没实现的20%是计算脚本和数据库的解耦。

复杂计算环境是它的弱项,比如:分布式计算、复杂计算、非数据

- 向网页中插入透明Flash的方法和技巧

dcj3sjt126com

htmlWebFlash

将

Flash 作品插入网页的时候,我们有时候会需要将它设为透明,有时候我们需要在Flash的背面插入一些漂亮的图片,搭配出漂亮的效果……下面我们介绍一些将Flash插入网页中的一些透明的设置技巧。

一、Swf透明、无坐标控制 首先教大家最简单的插入Flash的代码,透明,无坐标控制: 注意wmode="transparent"是控制Flash是否透明

- ios UICollectionView的使用

dcj3sjt126com

UICollectionView的使用有两种方法,一种是继承UICollectionViewController,这个Controller会自带一个UICollectionView;另外一种是作为一个视图放在普通的UIViewController里面。

个人更喜欢第二种。下面采用第二种方式简单介绍一下UICollectionView的使用。

1.UIViewController实现委托,代码如

- Eos平台java公共逻辑

蕃薯耀

Eos平台java公共逻辑Eos平台java公共逻辑

Eos平台java公共逻辑

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

蕃薯耀 2015年6月1日 17:20:4

- SpringMVC4零配置--Web上下文配置【MvcConfig】

hanqunfeng

springmvc4

与SpringSecurity的配置类似,spring同样为我们提供了一个实现类WebMvcConfigurationSupport和一个注解@EnableWebMvc以帮助我们减少bean的声明。

applicationContext-MvcConfig.xml

<!-- 启用注解,并定义组件查找规则 ,mvc层只负责扫描@Controller -->

<

- 解决ie和其他浏览器poi下载excel文件名乱码

jackyrong

Excel

使用poi,做传统的excel导出,然后想在浏览器中,让用户选择另存为,保存用户下载的xls文件,这个时候,可能的是在ie下出现乱码(ie,9,10,11),但在firefox,chrome下没乱码,

因此必须综合判断,编写一个工具类:

/**

*

* @Title: pro

- 挥洒泪水的青春

lampcy

编程生活程序员

2015年2月28日,我辞职了,离开了相处一年的触控,转过身--挥洒掉泪水,毅然来到了兄弟连,背负着许多的不解、质疑——”你一个零基础、脑子又不聪明的人,还敢跨行业,选择Unity3D?“,”真是不自量力••••••“,”真是初生牛犊不怕虎•••••“,••••••我只是淡淡一笑,拎着行李----坐上了通向挥洒泪水的青春之地——兄弟连!

这就是我青春的分割线,不后悔,只会去用泪水浇灌——已经来到

- 稳增长之中国股市两点意见-----严控做空,建立涨跌停版停牌重组机制

nannan408

对于股市,我们国家的监管还是有点拼的,但始终拼不过飞流直下的恐慌,为什么呢?

笔者首先支持股市的监管。对于股市越管越荡的现象,笔者认为首先是做空力量超过了股市自身的升力,并且对于跌停停牌重组的快速反应还没建立好,上市公司对于股价下跌没有很好的利好支撑。

我们来看美国和香港是怎么应对股灾的。美国是靠禁止重要股票做空,在

- 动态设置iframe高度(iframe高度自适应)

Rainbow702

JavaScriptiframecontentDocument高度自适应局部刷新

如果需要对画面中的部分区域作局部刷新,大家可能都会想到使用ajax。

但有些情况下,须使用在页面中嵌入一个iframe来作局部刷新。

对于使用iframe的情况,发现有一个问题,就是iframe中的页面的高度可能会很高,但是外面页面并不会被iframe内部页面给撑开,如下面的结构:

<div id="content">

<div id=&quo

- 用Rapael做图表

tntxia

rap

function drawReport(paper,attr,data){

var width = attr.width;

var height = attr.height;

var max = 0;

&nbs

- HTML5 bootstrap2网页兼容(支持IE10以下)

xiaoluode

html5bootstrap

<!DOCTYPE html>

<html>

<head lang="zh-CN">

<meta charset="UTF-8">

<meta http-equiv="X-UA-Compatible" content="IE=edge">