Verilog 常用操作符,以及$display系统函数 ModelSim 仿真

verilog的操作符主要包括—

算数操作符、Arithmetic Operators

关系操作符、Relational Operators

相等操作符、Equality Operators

逻辑操作符、Logical Operators

按位操作符、Bit-wise Operators

归约操作符、Reduction Operators (也叫缩减运算符)

移位操作符、Shift Operators

条件操作符、Conditional Operators

连接操作符、Concatenation Operator

赋值操作符、assignment operator;

一、算术操作符、Arithmetic Operators

| Operator | Description |

|---|---|

| + | binary plus |

| - | binary minus |

| * | multiply |

| / | divide |

| + | unary (sign) plus 符号操作符 |

| - | unary (sign) minus 符号操作符 |

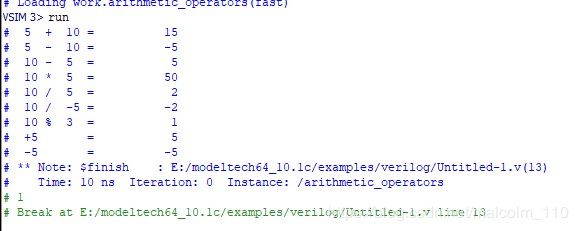

仿真代码

module arithmetic_operators();

initial begin

$display (" 5 + 10 = %d", 5 + 10);

$display (" 5 - 10 = %d", 5 - 10);

$display (" 10 - 5 = %d", 10 - 5);

$display (" 10 * 5 = %d", 10 * 5);

$display (" 10 / 5 = %d", 10 / 5);

$display (" 10 / -5 = %d", 10 / -5);

$display (" 10 %s 3 = %d","%", 10 % 3);

$display (" +5 = %d", +5);

$display (" -5 = %d", -5);

#10 $finish;

end

endmodule

仿真:

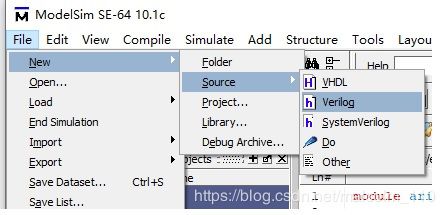

1.打开modlesim, File – new – source ,输入上面的代码。

-

Saveas

-

点击compile,找到刚才存储文件的路径,选中文件。会提示是否创建work文件夹,先点击Compile,然后点击done。

-

点击simulate,在弹出串口中,点击最上面work前面的加号,选中跟module相同名字的选项,点右下角OK。

二、关系操作符、Relational Operators

关系操作符的结果为1或0,即真或假。

| Operator | Description |

|---|---|

| a < b | a less than b |

| a > b | a greater than b |

| a <= b | a less than or equal to b |

| a >= b | a greater than or equal to b |

仿真代码

module relational_operators();

initial begin

$display (" 5 <= 10 = %b", (5 <= 10));

$display (" 5 >= 10 = %b", (5 >= 10));

$display (" 1'bx <= 10 = %b", (1'bx <= 10));

$display (" 1'bz <= 10 = %b", (1'bz <= 10));

#10 $finish;

end

endmodule

仿真步骤可以参照上面的算术操作符里提到的,这里省略了,只贴出结果。

5 <= 10 = 1

5 >= 10 = 0

1'bx <= 10 = x

1'bz <= 10 = x

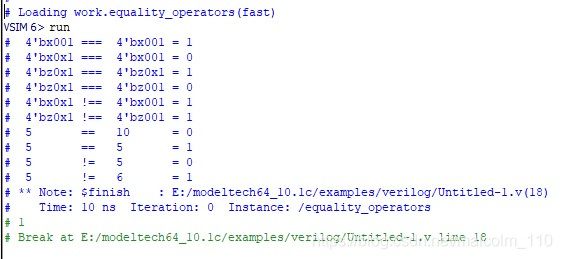

三、相等操作符、Equality Operators

| Operator | Description |

|---|---|

| a === b | a equal to b, including x and z (Case equality) |

| a !== b | a not equal to b, including x and z (Case inequality) |

| a == b | a equal to b, result may be unknown (logical equality) |

| a != b | a not equal to b, result may be unknown (logical equality) |

仿真代码:

module equality_operators();

initial begin

// Case Equality

$display (" 4'bx001 === 4'bx001 = %b", (4'bx001 === 4'bx001));

$display (" 4'bx0x1 === 4'bx001 = %b", (4'bx0x1 === 4'bx001));

$display (" 4'bz0x1 === 4'bz0x1 = %b", (4'bz0x1 === 4'bz0x1));

$display (" 4'bz0x1 === 4'bz001 = %b", (4'bz0x1 === 4'bz001));

// Case Inequality

$display (" 4'bx0x1 !== 4'bx001 = %b", (4'bx0x1 !== 4'bx001));

$display (" 4'bz0x1 !== 4'bz001 = %b", (4'bz0x1 !== 4'bz001));

// Logical Equality

$display (" 5 == 10 = %b", (5 == 10));

$display (" 5 == 5 = %b", (5 == 5));

// Logical Inequality

$display (" 5 != 5 = %b", (5 != 5));

$display (" 5 != 6 = %b", (5 != 6));

#10 $finish;

end

endmodule

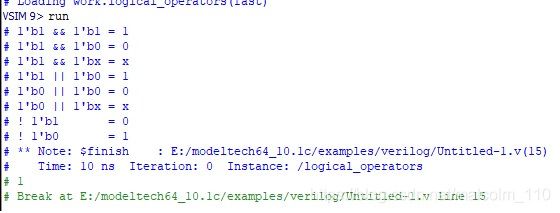

四、逻辑操作符、Logical Operators

| Operator | Description |

|---|---|

| ! | logic negation 逻辑取反 |

| && | logical and |

| || | logical or |

仿真代码:

module logical_operators();

initial begin

// Logical AND

$display ("1'b1 && 1'b1 = %b", (1'b1 && 1'b1));

$display ("1'b1 && 1'b0 = %b", (1'b1 && 1'b0));

$display ("1'b1 && 1'bx = %b", (1'b1 && 1'bx));

// Logical OR

$display ("1'b1 || 1'b0 = %b", (1'b1 || 1'b0));

$display ("1'b0 || 1'b0 = %b", (1'b0 || 1'b0));

$display ("1'b0 || 1'bx = %b", (1'b0 || 1'bx));

// Logical Negation

$display ("! 1'b1 = %b", (! 1'b1));

$display ("! 1'b0 = %b", (! 1'b0));

#10 $finish;

end

endmodule

五、按位操作符、Bit-wise Operators

| Operator | Description |

|---|---|

| ~ | negation |

| & | and |

| | | inclusive or 同或 |

| ^ | exclusive or 异或 |

| ^~ 或 ~^ | exclusive nor (equivalence) |

按位操作有时会不容易观察,特别是多个运算符在一起的时候,为了避免阅读上的障碍,尽量多用括号。

仿真代码

module bitwise_operators();

initial begin

// Bit Wise Negation

$display (" ~4'b0001 = %b", (~4'b0001));

$display (" ~4'bx001 = %b", (~4'bx001));

$display (" ~4'bz001 = %b", (~4'bz001));

// Bit Wise AND

$display (" 4'b0001 & 4'b1001 = %b", (4'b0001 & 4'b1001));

$display (" 4'b1001 & 4'bx001 = %b", (4'b1001 & 4'bx001));

$display (" 4'b1001 & 4'bz001 = %b", (4'b1001 & 4'bz001));

// Bit Wise OR

$display (" 4'b0001 | 4'b1001 = %b", (4'b0001 | 4'b1001));

$display (" 4'b0001 | 4'bx001 = %b", (4'b0001 | 4'bx001));

$display (" 4'b0001 | 4'bz001 = %b", (4'b0001 | 4'bz001));

// Bit Wise XOR

$display (" 4'b0001 ^ 4'b1001 = %b", (4'b0001 ^ 4'b1001));

$display (" 4'b0001 ^ 4'bx001 = %b", (4'b0001 ^ 4'bx001));

$display (" 4'b0001 ^ 4'bz001 = %b", (4'b0001 ^ 4'bz001));

// Bit Wise XNOR

$display (" 4'b0001 ~^ 4'b1001 = %b", (4'b0001 ~^ 4'b1001));

$display (" 4'b0001 ~^ 4'bx001 = %b", (4'b0001 ~^ 4'bx001));

$display (" 4'b0001 ~^ 4'bz001 = %b", (4'b0001 ~^ 4'bz001));

#10 $finish;

end

endmodule

六、归约操作符、Reduction Operators

也叫缩减运算符、递减运算符,这部分请参照之前的一篇博文

https://blog.csdn.net/malcolm_110/article/details/90487935

七、移位操作符、Shift Operators

| Operator | Description |

|---|---|

| << | left shift |

| >> | right shift |

仿真代码

module shift_operators();

initial begin

// Left Shift

$display (" 4'b1001 << 1 = %b", (4'b1001 << 1));

$display (" 4'b10x1 << 1 = %b", (4'b10x1 << 1));

$display (" 4'b10z1 << 1 = %b", (4'b10z1 << 1));

// Right Shift

$display (" 4'b1001 >> 1 = %b", (4'b1001 >> 1));

$display (" 4'b10x1 >> 1 = %b", (4'b10x1 >> 1));

$display (" 4'b10z1 >> 1 = %b", (4'b10z1 >> 1));

#10 $finish;

end

endmodule

仿真结果

4'b1001 << 1 = 0010

4'b10x1 << 1 = 0x10

4'b10z1 << 1 = 0z10

4'b1001 >> 1 = 0100

4'b10x1 >> 1 = 010x

4'b10z1 >> 1 = 010z

八、条件操作符、Conditional Operators

条件操作符就是代码中常见的形式如下的结构

cond_expr ? true_expr : false_expr

九、连接操作符、Concatenation Operator

连接操作符的作用就是实现位拼接。

{a[3:0], 4'b1001}

结果为8位。

还有一种叫Replication Operator,重复连接操作,形如:

{3{a}}

效果等同于 {a, a, a}

十、赋值操作符、assignment operator

| Operator | Description |

|---|---|

| = | blocking assignment |

| <= | Non-blocking assignment |

blocking assignment 阻塞赋值,用于组合逻辑里面,赋值不分先后顺序,可能造成竞争与冒险。

Non-blocking assignment 非阻塞赋值,用于时序逻辑里面,赋值是分先后顺序,这部分可参考其它资料。