解读Datasheet系列:M95080W(ST,SPI EEPROM)

本文只对 M95080W 数据手册的一部分进行解读,其涵盖的内容基本足够开发标准 SPI 接口的 EEPROM 驱动。完整的 Datasheet 下载:

https://download.csdn.net/download/luckydarcy/10443186

M95160-x 和 M95080-x 是电可擦除非易失性存储器(EEPROM)设备,通过高速 SPI 兼容总线进行访问,存储器阵列被组织成 2048 x 8bit(M95160-x)和 1024 x 8bit(M95080-x)。

M95080-x 读写

- 8Kbit(1K Byte)

- Page:32 Byte(一共32页)

- 可以按字节写入,也可以按页写入

- 允许对片内每一个字节进行读/写操作

16 Kbit and 8 Kbit serial SPI bus EEPROM with high speed clock

特性

- 速度高达10MHz

- 状态寄存器带硬件保护

- 字节和页写入方式(最多32字节)

- 可调节只读的EEPROM区域大小

- 超过一百万次写操作

- 数据保存超过40年

电压:

- 4.5V to 5.5V for M95xxx

- 2.5V to 5.5V for M95xxx-W

- 1.8V to 5.5V for M95xxx-R

- 1.7V to 5.5V for M95xxx-F

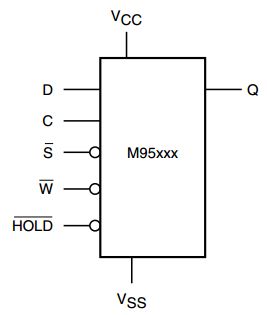

信号连接

设备通过一个简单的 SPI 串行接口进行访问,总线信号是 C、D 和 Q。

当片选信号被拉低时,设备被选中。设备的通信能够被 Hold 信号中断。

我们项目的电路连接:

信号描述

- 在所有操作期间,Vcc 必须在合法范围内保持稳定的电平输出,即 Vcc(min) 到 Vcc(max)

- 所有的输入/输出信号必须保持高或低。

Serial Data output(Q)

此输出信号用于将数据串行地从设备中传输出去。数据将在时钟信号的下降沿被 shift out。

Serial Data input(D)

此输入信号用于将数据串行地传输到设备端。例如接收指令、地址以及即将写入的数据,所有数据将在时钟信号的上升沿被捕获。

Serial Clock(C)

此输入信号为串行通信提供时序控制。在串行数据输入信号线(D)中出现的指令、地址和数据将在时钟线(C)的上升沿被捕获。而在串行数据输出信号线(Q)的数据将在时钟线(C)的下降沿被发送。

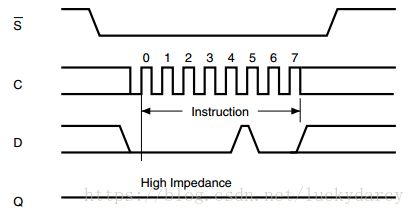

Chip Select(/S)

当此输入信号为高电平,设备处于未被选中的状态,此时串行数据输出(Q)为高阻态。如果此时设备内部的写周期仍在进行,则设备进入 Standby Power 模式。当片选信号(/S)被设置为低电平,取而代之的是 Active Power 模式。

上电之后,在开始传输任何指令之前,必须先触发此片选管脚的下降沿信号。

Hold(/HOLD)

Write Protect(/W)

Vcc supply voltage

Vss ground

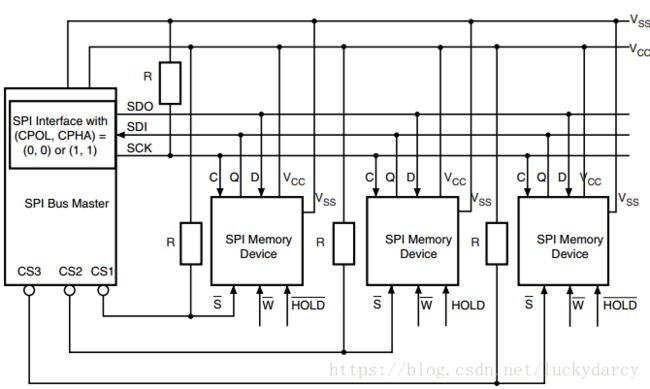

连接到 SPI 总线

M95080 和 M95160 完全兼容 SPI 协议。

所有的指令、地址和输入数据被移位到设备(most significant bit first),当片选信号被拉低后,串行数据输入(D)的信号将会在时钟信号线(C)的第一个上升沿被采集。

所有输出数据字节都会被移位出设备(most significant bit first),在传输完指令之后,串行数据输出(Q)的信号将在时钟信号线(C)的下降沿被发送。

下图表示了三个设备通过 SPI 总线连接到 MCU 的情况,同一时刻只有一个设备被选中,因此在同一时刻只有一个设备驱动串行数据输出(Q)信号线,其他未被选中的则处于高阻态。

当 SPI master 使片选信号线处于高阻态时,上拉电阻 R 确保了设备在处于未选中的状态。

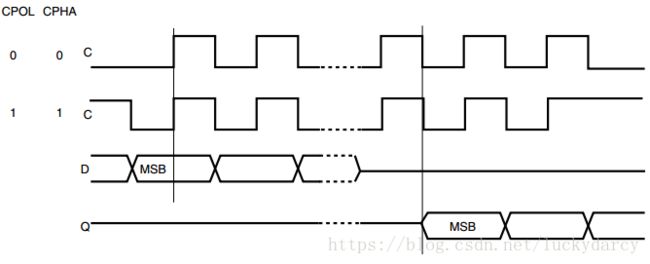

SPI 模式

当微处理器的 SPI 控制器为以下模式时,设备能被驱动

- CPOL=0, CPHA=0

- CPOL=1, CPHA=1

对于这两种模式,输入数据在时钟上升沿时被采集,输出数据在时钟下降沿时被发送。

两种模式的不同之处在于时钟极性(clock polarity),也就是说当 master 处于 Stand-by 模式且没有数据传输时,时钟信号线:

- 保持低电平(CPOL=0, CPHA=0)

- 保持高电平(CPOL=1, CPHA=1)

指令

指令以一个单字节码开头。如果发送了一个不合法的指令(不在下表中),设备会自动的取消选择自己。

(1)Write Enable(WREN)

在发送 WRITE 和 WRSR 指令前,必须先设置 Write Enable Latch(WEL)位。而唯一的设置方法就是 master 发送写使能指令(WREN)到 slave 设备。

(2)Write Disable(WRDI)

复位 Write Enable Latch(WEL)位的一个办法是往设备端发送 WRDI 指令。

实际上,以下事件都会使得 Write Enable Latch(WEL)位复位:

- 上电

- 执行 WRDI 指令

- WRSR 指令完成后

- WRITE 指令完成后

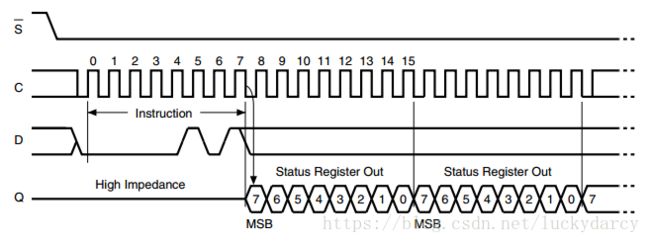

(3)Read Status Register(RDSR)

读状态寄存器(RDSR)指令允许 master 去访问设备的状态寄存器。状态寄存器在任何时候都可能被访问,即便是在一个写周期,甚至是写状态寄存器周期。如果这些写操作仍在进行中,建议在给设备端发送新的指令前先检查 Write In Progress(WIP)位。

也有可能会连续地读状态寄存器:

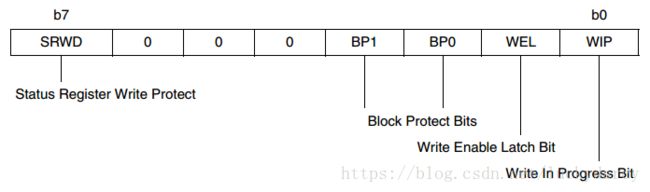

状态寄存器中具体的状态位和控制位介绍如下:

WIP bit

Write In Progress(WIP)位指示设备内存是否处于繁忙状态(WRITE 和 WRSR 周期)。如果 WIP 被置1,则表示相关写操作正在进行,如果 WIP 被置0,则没有。

WEL bit

Write Enable Latch(WEL)位指示内部写使能锁的状态。如果 WEL 被置1,则表示内部写使能锁被锁上(使能),如果 WEL 被置0,则表示内部写使能锁被打开(复位),此时将不能使用 WRITE 和 WRSR 指令。

BP1, BP0 bits

Block Protect 块保护(BP1,BP0)位是非易失性的。它们用来定义通过软件保护来避免写指令操作的区域大小,这些位通过写状态寄存器(WRSR)指令来修改。当 BP1 和 BP0 中的一个或两个被置1,相关的内存区域就会被保护起来,避免被 WRITE 指令操作。

注意:当硬件保护模式没有设置时,块保护(BP1,BP0)位才能被设置。

SRWD bit

Status Register Write Disable 状态寄存器写禁止(SRWD)位需要与写保护(/W)信号一起操作。SRWD 位和写保护(/W)信号允许设备置于硬件设备保护模式中(当 SRWD 位被置1,写保护被拉低)。在这种模式下,状态寄存器中的非易失性位(SRWD, BP1, BP0)将变成只读的,同时读状态寄存器(WRSR)指令将不被接受执行。

(4)Write Status Register(WRSR)

Write Status Register 写状态寄存器(WRSR)指令允许把新的值写入状态寄存器。但是写之前必须先执行 WREN 指令。

WRSR 指令先发送指令码(0x01),紧接着是一个字节的数据(即将设置的状态寄存器的值)。

WRSR 指令允许用户修改状态寄存器的 BP1,BP0 和 SRWD 位。

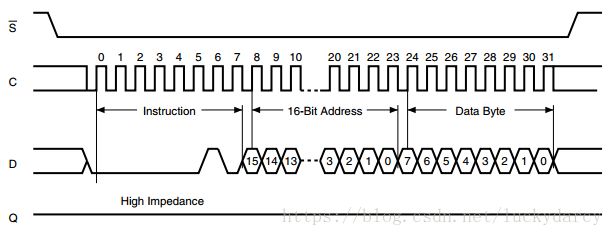

(5)Read from Memory Array(READ)

在片选信号拉低后,在串行数据输入(D)信号线上发送读指令(0x03)到设备,紧接着是16位的地址。然后设备会从串行数据输出(Q)信号线上移位出来。

如果片选信号继续保持低电平状态,还可以发送下一个地址,然后该地址的值被移位出来。

当到达最高的地址时,地址计数器会清零,允许无限循环地读。因此,整个存储器可以用一条指令读取。

读周期可以被片选信号中断,也就是说,在读周期期间,片选管脚的上升沿信号会中断读操作。

寻址的第一个字节可以是任意 Page 中的任意字节。

如果当前正在进行写周期,则设备不接受该指令,也不执行该指令。

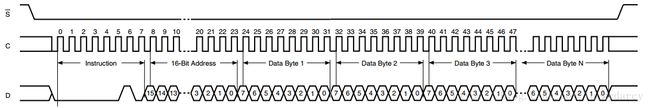

(6)Write to Memory Array(WRITE)

在片选信号拉低后,在串行数据输入(D)信号线上发送读指令(0x02)到设备,紧接着是16位的地址,以及至少一个字节的数据。

如下图所示,在数据字节的第八位被锁存后,如果片选信号被拉高,则表明指令被用来写一个字节。

但是,如果片选信号继续被拉低,如下图所示,则输入数据的下一个字节被移位,因此,从给定地址往后直到本页结束的多个字节,可以在同一个内部写周期中写入。

每次移动一个新的数据字节时,内部地址计数器的最小有效位都会增加。如果发送到设备的数据字节数超过页边界,则内部地址计数器将滚到页的开头,所以先前的数据将会被传入的数据所覆盖。(M95160 和 M95080 的页大小为 32 字节)

在下列一些情况中,WRITE 指令将不会被接受和执行:

- WEL 位还没置1(执行 WREN 指令);

- 写周期正在进行中;

- 设备没有被选中,在字节边界处,片选被拉高;

- 寻址的页属于保护区域(块保护)。