LLVM libc++的RISCV支持

libc++的官方主页:http://libcxx.llvm.org/

libc++文档主页:https://libcxx.llvm.org/docs/

简介:

libc++ is an implementation of the C++ standard library, targeting C++11, C++14 and above.

All of the code in libc++ is dual licensed under the MIT license and the UIUC License (a BSD-like license).

对标的产品:

1、 Apache's libstdcxx

2、GNU's libstdc++

3、STLport

目前状态:(来源:http://libcxx.llvm.org/ 和 https://libcxx.llvm.org/docs/)

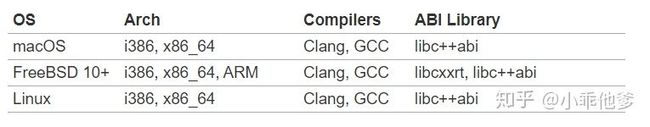

1、操作系统和硬件平台支持状况

libc++ is known to work on the following platforms, using gcc and clang. (Note that functionality provided by

2、编译器版本支持

- Clang 4.0 and above

- GCC 5.0 and above.

The C++03 dialect is only supported for Clang compilers.

3、C++版本支持情况

- C++11 - Complete

- C++14 - Complete(http://libcxx.llvm.org/cxx1y_status.html)

- C++17 - In Progress(http://libcxx.llvm.org/cxx1z_status.html)

- C++2a - In Progress(http://libcxx.llvm.org/cxx2a_status.html)

- Post C++14 Technical Specifications - In Progress(http://libcxx.llvm.org/ts1z_status.html)

- C++ Feature Test Macro Status(https://libcxx.llvm.org/docs/FeatureTestMacroTable.html#feature-status)

编译与测试:(来源:https://libcxx.llvm.org/docs/BuildingLibcxx.html#getting-started)

$ git clone https://github.com/llvm/llvm-project.git

$ cd llvm-project $ mkdir build && cd build

$ cmake -DCMAKE_C_COMPILER=clang \ -DCMAKE_CXX_COMPILER=clang++ \ -DLLVM_ENABLE_PROJECTS="libcxx;libcxxabi" \ ../llvm

$ make # Build $ make check-cxx # Test

$ make install-cxx install-cxxabi # Install

注意:make check-cxx 无法执行,执行llvm-lit libcxx/test/目录,得到结果:

源码中与RISC-V相关的内容:

1、/libcxx/utils/google-benchmark/src/cycleclock.h中有关于riscv架构时钟的一些内容:

#elif defined(__riscv) // RISC-V

// Use RDCYCLE (and RDCYCLEH on riscv32)

#if __riscv_xlen == 32

uint32_t cycles_lo, cycles_hi0, cycles_hi1;

// This asm also includes the PowerPC overflow handling strategy, as above.

// Implemented in assembly because Clang insisted on branching.

asm volatile(

"rdcycleh %0\n"

"rdcycle %1\n"

"rdcycleh %2\n"

"sub %0, %0, %2\n"

"seqz %0, %0\n"

"sub %0, zero, %0\n"

"and %1, %1, %0\n"

: "=r"(cycles_hi0), "=r"(cycles_lo), "=r"(cycles_hi1));

return (static_cast(cycles_hi1) << 32) | cycles_lo;

#else

uint64_t cycles;

asm volatile("rdcycle %0" : "=r"(cycles));

return cycles;

#endif

发布于 10:17