- (179)时序收敛--->(29)时序收敛二九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (180)时序收敛--->(30)时序收敛三十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (158)时序收敛--->(08)时序收敛八

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛八(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (159)时序收敛--->(09)时序收敛九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (160)时序收敛--->(10)时序收敛十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (153)时序收敛--->(03)时序收敛三

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (121)DAC接口--->(006)基于FPGA实现DAC8811接口

FPGA系统设计指南针

FPGA接口开发(项目实战)fpga开发FPGAIC

1目录(a)FPGA简介(b)IC简介(c)Verilog简介(d)基于FPGA实现DAC8811接口(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电

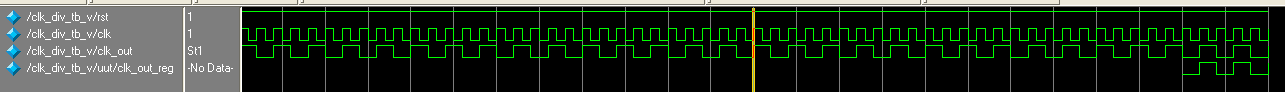

- FPGA复位专题---(3)上电复位?

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发

(3)上电复位?1目录(a)FPGA简介(b)Verilog简介(c)复位简介(d)上电复位?(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限

- (182)时序收敛--->(32)时序收敛三二

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三二(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- Quartus sdc UI界面设置(二)

落雨无风

IC设计fpgafpga开发

Quartussdc设置根据一配置quartus综合简单流程(一)上次文章中,说了自己写sdc需要配置的分类点,这次将说明在UI界面配置sdc。1.在Quartus软件中,导入verilog设计之后,打开Tools/TimeQuestTimingAnalyzer界面大致分为上下两部分,上半部分左侧显示Report、Tasks,右侧显示欢迎界面;下半部分显示Console和History,此处缺图,

- 牛客Verilog语法刷题Day 1

SAChemAdvance

刷题fpga开发

校验器的输入是由原始数据位和校验位组成对于奇偶校验,若合法编码中奇数位发生了错误,也就是编码中的1变成0或0变成1,则编码中1的个数的奇偶性就发生了变化,从而可以发现错误,但不能检测出是哪些位出错。对于一个设置为50MHz的移位寄存器,把16左移到128,需要()nsA.30B.40C.50D.60本题答案选D,从16到128需要3位,50MHz的时钟为20ns,移动3位则为60ns时间(s)=1

- 连续发送多个数据(uart串口RS232协议/verilog详细代码+仿真)

勇敢牛牛(FPGA学习版)

fpga开发嵌入式硬件matlab智能硬件

写在前言以下内容详细源文件,已经上传个人主页资源,需要自取~目录写在前言需求分析UART简介整体架构流程小结需求分析使用串口(rs232协议)间隔1s连续发送16byte的数据。由于每次发送的数据只有8bit,16byte=128bit,所以要发送16帧。UART简介这里实验所使用的参数有:rs232通信协议+9600bps+quartus18.0+modelsim2020异步通信:UART是一种

- 第11周作业---HLS编程环境入门

pss_runner

目录HLS概念HLS是什么HLS与VHDL/Verilog有什么关系?HLS技术问题HLS开发步骤环境搭建编写test.cpp文件预编译cpp文件HLS概念HLS是什么高层次综合(High-levelSynthesis)简称HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括C、C++、SystemC等,通常有着较高的抽象度,并且往往不具有时

- VCS简介

XtremeDV

VCS快速实战指南

1.2.1关于VCSVCS是VerilogCompiledSimulator的缩写。VCSMX®是一个编译型的代码仿真器。它使你能够分析,编译和仿真Verilog,VHDL,混合HDL,SystemVerilog,OpenVera和SystemC描述的设计。它还为您提供了一系列仿真和调试功能,以验证您的设计。这些功能提供了源码调试和仿真结果查看功能。vcs提供了一系列的feature,如下图:业界

- vcs 入门

hemmingway

Xilinx/FPGA

synopsysvcs软件是仿真和验证的软件,必须掌握。vcs即verilogcompilesimulator支持verilog,systemVerilog,openvera,systemC等语言,同时也有代码覆盖率检测等功能。可以合第三方软件集合使用,例如Vera,Debussy,Specman等等。在linux下调用vcs,需要设置相应的环境变量。1、学习vcs最好的资料肯定是官方的说明书,安

- Xilinx Vivado的RTL分析(RTL analysis)、综合(synthesis)和实现

2401_84185145

程序员fpga开发

理论上,FPGA从编程到下载实现预期功能的过程最少仅需要上述7个步骤中的4、5、6和7,即RTL分析、综合、实现和下载。其中的RTL分析、综合、实现的具体含义和区别又是什么?2、RTL分析(RTLanalysis)一般来讲,通常的设计输入都是Verilog、VHDL或者SystemVerilog等硬件描述语言HDL编写的文件,RTL分析这一步就是将HDL语言转化成逻辑电路图的过程。比如HDL语言描

- 1. Verilog2. C语言3. 数组4. 关键词5. 模块

行者..................

c语言fpga开发开发语言FPGA

###5.2.4Verilog数组VSC语言数组####Verilog数组在Verilog语言中,数组通常被称作内存。以下是一个定义的例子:```verilog(*ram_style="distributed"*)reg[0:31]MyMem[0:7]```这行代码定义了一个长度为32位,包含7个元素的数组。具体来说:-`reg[0:31]`表示每个数组元素是一个32位的寄存器。-`MyMem[0

- (170)时序收敛--->(20)时序收敛二十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- 初识 Verilog

栀栀栀

笔记

Verilog综述:类C,并行,自顶向下,硬件描述语言,VHDL,VerilogHDL。VHDL,VerilogHDL,两种不同描述语言。Verilog语言(并行,硬件)类似C语言(串行,软件)。基础知识:1.Verilog的四值逻辑系统0低电平1高电平X不确定Z高阻态2.Verilog的数据类型寄存器数据类型表示一个抽象的数据存储单元,只能在always语句和initial语句等过程语句中被赋值

- Verilog刷题笔记31

十六追梦记

笔记

题目:Supposeyouaredesigningacircuittocontrolacellphone’sringerandvibrationmotor.Wheneverthephoneneedstoringfromanincomingcall(),yourcircuitmusteitherturnontheringer()orthemotor(),butnotboth.Ifthephoneis

- Quartus网盘资源下载与安装 附图文安装教程

学习天使Alice

fpga开发学习

如大家所了解的,Quartus是一种FPGA设计软件(相信理工科的小伙伴,很多都接触或学习过FPGA),旨在为数字电路设计师提供一个高效、便捷的开发环境。它可以帮助用户完成数字逻辑电路的设计、仿真、综合和布局,以及与外围设备进行通信和控制。Quartus支持多种编程语言,包括VHDL、Verilog等,并具有丰富的功能和工具库,可满足不同级别、不同规模的数字电路设计需求。收藏的Quartus安装包

- Verilog刷题笔记59

十六追梦记

笔记

题目:Exams/m2014q6c解题:moduletop_module(input[6:1]y,inputw,outputY2,outputY4);assignY2=y[1]&w==0;assignY4=(y[2]&w==1)|(y[3]&w==1)|(y[5]&w==1)|(y[6]&w==1);endmodule结果正确:注意点:起初,我的代码有错误,代码如下:moduletop_modul

- Verilog刷题笔记62

十六追梦记

笔记fpga开发

题目:Exams/review2015fancytimerThisisthefifthcomponentinaseriesoffiveexercisesthatbuildsacomplexcounteroutofseveralsmallercircuits.Youmaywishtodothefourpreviousexercisesfirst(counter,sequencerecognizerF

- Verilog刷题笔记60

十六追梦记

笔记fpga开发

题目:Exams/2013q2bfsmConsiderafinitestatemachinethatisusedtocontrolsometypeofmotor.TheFSMhasinputsxandy,whichcomefromthemotor,andproducesoutputsfandg,whichcontrolthemotor.Thereisalsoaclockinputcalledclk

- vivado U_SET

cckkppll

fpga开发

将具有附加相对位置(RLOC)约束的设计元素分组,这些约束是分布在整个设计层次结构中,形成一个集合。U_SET是HDL设计源文件中的一个属性,不会出现在综合或实施的设计。U_SET在定义相对放置宏时使用,或者RTL设计中的RPM。有关使用这些属性和定义的更多信息RPM,请参阅《Vivado设计套件用户指南:使用约束》(UG903)[参考文献19]。而H_SET或HU_SET用于根据设计定义逻辑元素

- verilog中简单的one-hot 状态机转换

Lambor_Ma

verilog数字

简单的one-hot状态机转换one-hot编码verilog中写法one-hot编码0001001001001000如上例每次只有1个bit位置high其余low的状态叫one-hot,相反只有1个bitlow其余bithigh叫one-cold。verilog中写法一般状态机转换中我们会先paremeterA=0001,B=0010,C=0100,D=1000;像这样预设值,这里介绍一种新的方

- verilog中 blocking assignment 和non-blocking assignment的区别(阻塞赋值和非阻塞赋值的区别)

Lambor_Ma

verilog数字

阻塞赋值与非阻塞赋值:1.阻塞赋值“=”(组合逻辑电路),非阻塞赋值“<=”(时序逻辑电路);2.Verilog模块编程的8个原则:(1)时序电路建模时,用非阻塞赋值。(2)锁存器电路建模时,用非阻塞赋值。(3)用always块建立组合逻辑模型时,用阻塞赋值。(4)在同一个always块中建立时序和组合逻辑电路时,用非阻塞赋值。(5)在同一个always块中不要既用非阻塞赋值又用阻塞赋值。(6)不

- verilog中 case写法避免写default的巧妙写法

Lambor_Ma

verilog数字

always@(*)beginout='1;//'1isaspecialliteralsyntaxforanumberwithallbitssetto1.//'0,'x,and'zarealsovalid.//Iprefertoassignadefaultvalueto'out'insteadofusinga//defaultcase.case(sel)4'h0:out=a;4'h1:out=b;

- SOC学习历程概述

weixin_30376509

操作系统嵌入式运维

从开始接触soc到现在大概有两年半左右的时间了,经历了ORSOC到minsoc再到mkg-soc的搭建,以及现在的大小核系统的搭建首先先讲下学习的前期需要具备的知识,前面3点是必须,后面3点可以中间学习的过程再学习。之所以有这些要求主要是以防中间的学习过程中,有些东西看不懂而走弯路。学习的前期准备:1、学过数电,有一定的电路基础。2、熟练掌握verilog语言。3、对于计算机组成原理,体系结构有一

- FPGA上板项目(四)——FIFO测试

_做个辣妹

FPGAfpga开发

目录实验内容实验原理FIFOIP核时序绘制HDL代码仿真综合实现上板测试实验内容理解FIFO原理调用FIFOIP核完成数据读写实验原理FIFO:FirstInFirstOut,先入先出式数据缓冲器,用来实现数据先入先出的读写方式。可分类为同步FIFO和异步FIFO,读写时钟相同即为同步FIFO,读写时钟不同即为异步FIFO。FIFO框图:FIFO端口定义与说明:写端口说明读端口说明wr_clk写时

- HQL之投影查询

归来朝歌

HQLHibernate查询语句投影查询

在HQL查询中,常常面临这样一个场景,对于多表查询,是要将一个表的对象查出来还是要只需要每个表中的几个字段,最后放在一起显示?

针对上面的场景,如果需要将一个对象查出来:

HQL语句写“from 对象”即可

Session session = HibernateUtil.openSession();

- Spring整合redis

bylijinnan

redis

pom.xml

<dependencies>

<!-- Spring Data - Redis Library -->

<dependency>

<groupId>org.springframework.data</groupId>

<artifactId>spring-data-redi

- org.hibernate.NonUniqueResultException: query did not return a unique result: 2

0624chenhong

Hibernate

参考:http://blog.csdn.net/qingfeilee/article/details/7052736

org.hibernate.NonUniqueResultException: query did not return a unique result: 2

在项目中出现了org.hiber

- android动画效果

不懂事的小屁孩

android动画

前几天弄alertdialog和popupwindow的时候,用到了android的动画效果,今天专门研究了一下关于android的动画效果,列出来,方便以后使用。

Android 平台提供了两类动画。 一类是Tween动画,就是对场景里的对象不断的进行图像变化来产生动画效果(旋转、平移、放缩和渐变)。

第二类就是 Frame动画,即顺序的播放事先做好的图像,与gif图片原理类似。

- js delete 删除机理以及它的内存泄露问题的解决方案

换个号韩国红果果

JavaScript

delete删除属性时只是解除了属性与对象的绑定,故当属性值为一个对象时,删除时会造成内存泄露 (其实还未删除)

举例:

var person={name:{firstname:'bob'}}

var p=person.name

delete person.name

p.firstname -->'bob'

// 依然可以访问p.firstname,存在内存泄露

- Oracle将零干预分析加入网络即服务计划

蓝儿唯美

oracle

由Oracle通信技术部门主导的演示项目并没有在本月较早前法国南斯举行的行业集团TM论坛大会中获得嘉奖。但是,Oracle通信官员解雇致力于打造一个支持零干预分配和编制功能的网络即服务(NaaS)平台,帮助企业以更灵活和更适合云的方式实现通信服务提供商(CSP)的连接产品。这个Oracle主导的项目属于TM Forum Live!活动上展示的Catalyst计划的19个项目之一。Catalyst计

- spring学习——springmvc(二)

a-john

springMVC

Spring MVC提供了非常方便的文件上传功能。

1,配置Spring支持文件上传:

DispatcherServlet本身并不知道如何处理multipart的表单数据,需要一个multipart解析器把POST请求的multipart数据中抽取出来,这样DispatcherServlet就能将其传递给我们的控制器了。为了在Spring中注册multipart解析器,需要声明一个实现了Mul

- POJ-2828-Buy Tickets

aijuans

ACM_POJ

POJ-2828-Buy Tickets

http://poj.org/problem?id=2828

线段树,逆序插入

#include<iostream>#include<cstdio>#include<cstring>#include<cstdlib>using namespace std;#define N 200010struct

- Java Ant build.xml详解

asia007

build.xml

1,什么是antant是构建工具2,什么是构建概念到处可查到,形象来说,你要把代码从某个地方拿来,编译,再拷贝到某个地方去等等操作,当然不仅与此,但是主要用来干这个3,ant的好处跨平台 --因为ant是使用java实现的,所以它跨平台使用简单--与ant的兄弟make比起来语法清晰--同样是和make相比功能强大--ant能做的事情很多,可能你用了很久,你仍然不知道它能有

- android按钮监听器的四种技术

百合不是茶

androidxml配置监听器实现接口

android开发中经常会用到各种各样的监听器,android监听器的写法与java又有不同的地方;

1,activity中使用内部类实现接口 ,创建内部类实例 使用add方法 与java类似

创建监听器的实例

myLis lis = new myLis();

使用add方法给按钮添加监听器

- 软件架构师不等同于资深程序员

bijian1013

程序员架构师架构设计

本文的作者Armel Nene是ETAPIX Global公司的首席架构师,他居住在伦敦,他参与过的开源项目包括 Apache Lucene,,Apache Nutch, Liferay 和 Pentaho等。

如今很多的公司

- TeamForge Wiki Syntax & CollabNet User Information Center

sunjing

TeamForgeHow doAttachementAnchorWiki Syntax

the CollabNet user information center http://help.collab.net/

How do I create a new Wiki page?

A CollabNet TeamForge project can have any number of Wiki pages. All Wiki pages are linked, and

- 【Redis四】Redis数据类型

bit1129

redis

概述

Redis是一个高性能的数据结构服务器,称之为数据结构服务器的原因是,它提供了丰富的数据类型以满足不同的应用场景,本文对Redis的数据类型以及对这些类型可能的操作进行总结。

Redis常用的数据类型包括string、set、list、hash以及sorted set.Redis本身是K/V系统,这里的数据类型指的是value的类型,而不是key的类型,key的类型只有一种即string

- SSH2整合-附源码

白糖_

eclipsespringtomcatHibernateGoogle

今天用eclipse终于整合出了struts2+hibernate+spring框架。

我创建的是tomcat项目,需要有tomcat插件。导入项目以后,鼠标右键选择属性,然后再找到“tomcat”项,勾选一下“Is a tomcat project”即可。具体方法见源码里的jsp图片,sql也在源码里。

补充1:项目中部分jar包不是最新版的,可能导

- [转]开源项目代码的学习方法

braveCS

学习方法

转自:

http://blog.sina.com.cn/s/blog_693458530100lk5m.html

http://www.cnblogs.com/west-link/archive/2011/06/07/2074466.html

1)阅读features。以此来搞清楚该项目有哪些特性2)思考。想想如果自己来做有这些features的项目该如何构架3)下载并安装d

- 编程之美-子数组的最大和(二维)

bylijinnan

编程之美

package beautyOfCoding;

import java.util.Arrays;

import java.util.Random;

public class MaxSubArraySum2 {

/**

* 编程之美 子数组之和的最大值(二维)

*/

private static final int ROW = 5;

private stat

- 读书笔记-3

chengxuyuancsdn

jquery笔记resultMap配置ibatis一对多配置

1、resultMap配置

2、ibatis一对多配置

3、jquery笔记

1、resultMap配置

当<select resultMap="topic_data">

<resultMap id="topic_data">必须一一对应。

(1)<resultMap class="tblTopic&q

- [物理与天文]物理学新进展

comsci

如果我们必须获得某种地球上没有的矿石,才能够进行某些能量输出装置的设计和建造,而要获得这种矿石,又必须首先进行深空探测,而要进行深空探测,又必须获得这种能量输出装置,这个矛盾的循环,会导致地球联盟在与宇宙文明建立关系的时候,陷入困境

怎么办呢?

- Oracle 11g新特性:Automatic Diagnostic Repository

daizj

oracleADR

Oracle Database 11g的FDI(Fault Diagnosability Infrastructure)是自动化诊断方面的又一增强。

FDI的一个关键组件是自动诊断库(Automatic Diagnostic Repository-ADR)。

在oracle 11g中,alert文件的信息是以xml的文件格式存在的,另外提供了普通文本格式的alert文件。

这两份log文

- 简单排序:选择排序

dieslrae

选择排序

public void selectSort(int[] array){

int select;

for(int i=0;i<array.length;i++){

select = i;

for(int k=i+1;k<array.leng

- C语言学习六指针的经典程序,互换两个数字

dcj3sjt126com

c

示例程序,swap_1和swap_2都是错误的,推理从1开始推到2,2没完成,推到3就完成了

# include <stdio.h>

void swap_1(int, int);

void swap_2(int *, int *);

void swap_3(int *, int *);

int main(void)

{

int a = 3;

int b =

- php 5.4中php-fpm 的重启、终止操作命令

dcj3sjt126com

PHP

php 5.4中php-fpm 的重启、终止操作命令:

查看php运行目录命令:which php/usr/bin/php

查看php-fpm进程数:ps aux | grep -c php-fpm

查看运行内存/usr/bin/php -i|grep mem

重启php-fpm/etc/init.d/php-fpm restart

在phpinfo()输出内容可以看到php

- 线程同步工具类

shuizhaosi888

同步工具类

同步工具类包括信号量(Semaphore)、栅栏(barrier)、闭锁(CountDownLatch)

闭锁(CountDownLatch)

public class RunMain {

public long timeTasks(int nThreads, final Runnable task) throws InterruptedException {

fin

- bleeding edge是什么意思

haojinghua

DI

不止一次,看到很多讲技术的文章里面出现过这个词语。今天终于弄懂了——通过朋友给的浏览软件,上了wiki。

我再一次感到,没有辞典能像WiKi一样,给出这样体贴人心、一清二楚的解释了。为了表达我对WiKi的喜爱,只好在此一一中英对照,给大家上次课。

In computer science, bleeding edge is a term that

- c中实现utf8和gbk的互转

jimmee

ciconvutf8&gbk编码

#include <iconv.h>

#include <stdlib.h>

#include <stdio.h>

#include <unistd.h>

#include <fcntl.h>

#include <string.h>

#include <sys/stat.h>

int code_c

- 大型分布式网站架构设计与实践

lilin530

应用服务器搜索引擎

1.大型网站软件系统的特点?

a.高并发,大流量。

b.高可用。

c.海量数据。

d.用户分布广泛,网络情况复杂。

e.安全环境恶劣。

f.需求快速变更,发布频繁。

g.渐进式发展。

2.大型网站架构演化发展历程?

a.初始阶段的网站架构。

应用程序,数据库,文件等所有的资源都在一台服务器上。

b.应用服务器和数据服务器分离。

c.使用缓存改善网站性能。

d.使用应用

- 在代码中获取Android theme中的attr属性值

OliveExcel

androidtheme

Android的Theme是由各种attr组合而成, 每个attr对应了这个属性的一个引用, 这个引用又可以是各种东西.

在某些情况下, 我们需要获取非自定义的主题下某个属性的内容 (比如拿到系统默认的配色colorAccent), 操作方式举例一则:

int defaultColor = 0xFF000000;

int[] attrsArray = { andorid.r.

- 基于Zookeeper的分布式共享锁

roadrunners

zookeeper分布式共享锁

首先,说说我们的场景,订单服务是做成集群的,当两个以上结点同时收到一个相同订单的创建指令,这时并发就产生了,系统就会重复创建订单。等等......场景。这时,分布式共享锁就闪亮登场了。

共享锁在同一个进程中是很容易实现的,但在跨进程或者在不同Server之间就不好实现了。Zookeeper就很容易实现。具体的实现原理官网和其它网站也有翻译,这里就不在赘述了。

官

- 两个容易被忽略的MySQL知识

tomcat_oracle

mysql

1、varchar(5)可以存储多少个汉字,多少个字母数字? 相信有好多人应该跟我一样,对这个已经很熟悉了,根据经验我们能很快的做出决定,比如说用varchar(200)去存储url等等,但是,即使你用了很多次也很熟悉了,也有可能对上面的问题做出错误的回答。 这个问题我查了好多资料,有的人说是可以存储5个字符,2.5个汉字(每个汉字占用两个字节的话),有的人说这个要区分版本,5.0

- zoj 3827 Information Entropy(水题)

阿尔萨斯

format

题目链接:zoj 3827 Information Entropy

题目大意:三种底,计算和。

解题思路:调用库函数就可以直接算了,不过要注意Pi = 0的时候,不过它题目里居然也讲了。。。limp→0+plogb(p)=0,因为p是logp的高阶。

#include <cstdio>

#include <cstring>

#include <cmath&