- AXI总线之相关应用

逾越TAO

fpga开发硬件工程笔记

AXI总线作为现代SoC设计的核心互连协议,其应用场景极为广泛,覆盖移动设备、AI加速器、FPGA、存储控制器等多个领域。以下是AXI在不同应用中的关键角色及具体实现案例:一、移动处理器与SoC应用场景:智能手机、平板电脑的SoC(如高通骁龙、苹果A系列、华为麒麟)中,AXI用于连接多核CPU、GPU、ISP(图像信号处理器)、DDR控制器等模块。典型案例:ARMCortex-A系列多核集群:AX

- 【FPGA教程案例31】通信案例1——基于FPGA的ASK调制信号产生

fpga和matlab

★教程2:fpga入门100例fpga开发FPGA教程ASK调制verilog

FPGA教程目录MATLAB教程目录---------------------------------------------------------------------------------------目录1.软件版本2.ASK调制原理3.ASK调制过程的FPGA实现4.操作步骤与仿真结论5.参考文献1.软件版本vivado2019.22.ASK调制原理幅度键控(Amplitude-Shi

- 【教程4>第2章>第30节】本章整体思维导图与学习总结

fpga和matlab

#第3章·通信—高阶调制解调FPGA教程4学习总结高阶调制解调

教程4.目录.目录1.本章节目录2.本章节思维导图3.本章节学习案例与实际应用欢迎订阅FPGA/MATLAB/Simulink系列教程《★教程1:matlab入门100例》《★教程2:fpga入门100例》《★教程3:simulink入

- 算力未来演进与多场景创新

智能计算研究中心

其他

内容概要算力作为数字经济的核心生产力,其技术架构与应用场景正经历多维突破。从技术架构层面来看,异构计算通过整合CPU、GPU、FPGA等多元芯片实现性能跃升,边缘计算则借助分布式节点降低时延并提升响应效率,而量子计算在特定领域的指数级加速潜力已进入验证阶段。在应用场景维度,工业互联网通过实时数据分析优化产线效率,智能安防依托视频流结构化处理增强预警能力,元宇宙则依赖高密度渲染与低延迟传输构建沉浸式

- FPGA中级项目3——IP核之时钟管理单元

霖00

fpga开发经验分享嵌入式硬件fpga网络时序数据库

FPGA中级项目3——IP核之时钟管理单元时钟还需要管理?什么是时钟管理单元?我们常熟知FPGA本身有晶振单元,源源不断的提供的50Mhz的频率波。但是这样往往无法满足一些设计需求。使用Verilog代码设计倍频分频等又不可避免的出现毛刺等其他状况,且提升了代码复杂度。因此在FPGA设计中,时钟管理单元(ClockManagementUnit,CMU)IP核是关键组件,用于生成、调整和分配系统时钟

- 【从零开始学习计算机科学】硬件设计与FPGA原理

贫苦游商

【从零开始学习计算机】硬件设计fpga开发学习数字逻辑verilogHDL硬件设计硬件工程

硬件设计硬件设计流程在设计硬件电路之前,首先要把大的框架和架构要搞清楚,这要求我们搞清楚要实现什么功能,然后找找有否能实现同样或相似功能的参考电路板(要懂得尽量利用他人的成果,越是有经验的工程师越会懂得借鉴他人的成果)。如果你找到了的参考设计,最好还是先看懂并理解,这一方面能提高我们的电路理解能力,而且能避免设计中的错误。在开始做硬件设计前,根据自己的项目需求,可以去找能够满足硬件功能设计的,有很

- 【无标题】采集板设计

weixin_42366388

测试工具

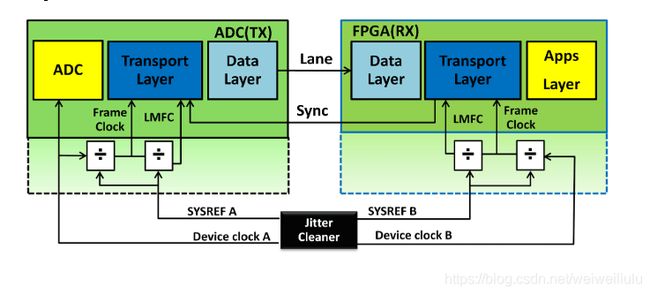

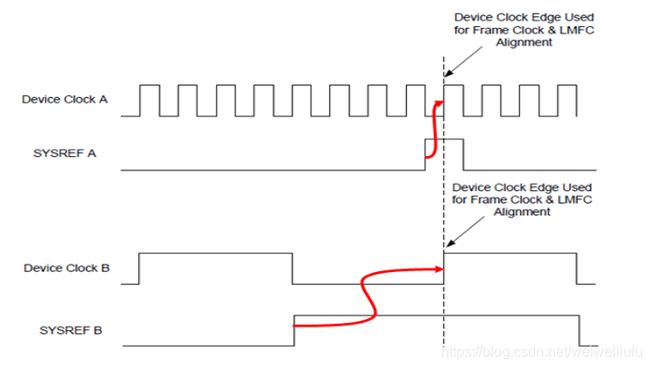

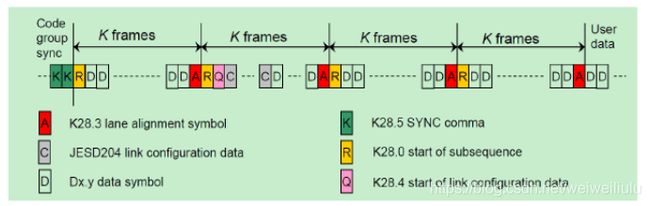

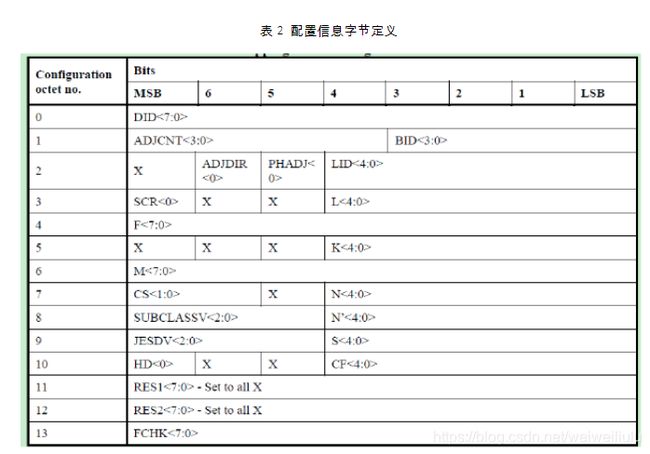

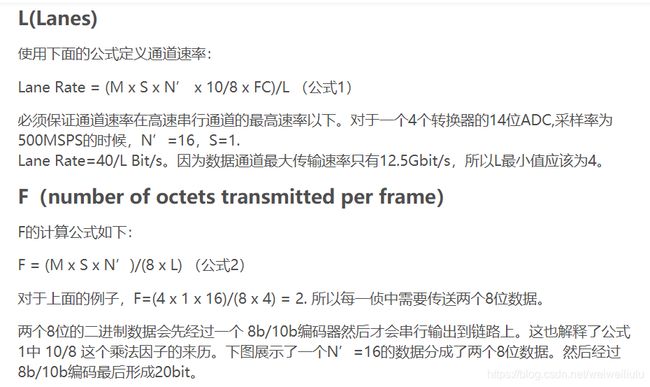

设计包含16片AD9680ADC和XilinxXC7V690FPGA的电路板需要解决高速数据接口、电源管理、时钟同步及PCB布局等关键挑战。**1.系统架构设计**####**核心组件**-**ADC**:16片AD9680(双通道14-bit1GSPS,JESD204B接口)-**FPGA**:XilinxXC7V690T-2FFG1761I(含48个GTX收发器,12.5Gbps/通道)-**

- FPGA为何要尽量减少组合逻辑的使用

昇柱

fpga开发

在FPGA设计中,组合逻辑的使用确实需要谨慎,尤其是要尽量减少它的复杂性。这并不是因为组合逻辑本身不好,而是因为它在实际应用中容易引发一系列问题,而这些问题往往与FPGA的设计哲学和硬件特性相冲突。让我从几个关键点来和你聊聊这件事。组合逻辑的即时性,是一把双刃剑组合逻辑的最大特点是即时性——它的输出完全由当前输入决定,没有存储功能。这种特性让它在某些场景下非常高效,比如简单的逻辑判断或者快速的数据

- fpga驱动rgb液晶屏_以ARM+FPGA结构驱动高分辨率液晶显示设计与效果测试

奶油小馒头

fpga驱动rgb液晶屏

摘要:结合ARM操作灵活和FPGA实时处理的优点,提出采用ARM+FPGA结构驱动高分辨率RGB888液晶显示屏。ARM接口丰富、操作灵活可以满足客户操作方便的需求;FPGA模块采用FPGA+DDR形式,数据存取速度达到400MB/s可以满足画面刷新速度较快的需求;FPGA操作DDR方式采用双端口64bit模式,设计32bit数据读取宽度,实现RGB888数据无失真显示。通过ARM处理器LPC17

- 基于NXP+FPGA轨道交通3U机箱结构远程输入/输出模块(RIOM)

深圳信迈主板定制专家

轨道交通NXP+FPGAfpga开发人工智能大数据边缘计算运维

基于NXP+FPGA轨道交通6U机箱结构远程输入/输出模块(RIOM)RIOM使得数据通过就近的I/O源输入和输出。也可以直接将I/O源连接到列车计算机(如VCU),可以减少电缆用量从而节约成本。关键特性支持模拟和数字输入/输出。可配置的模块包括DI、DIO、MDO、RDO、AIO、PTI等。接口选项MVBRIOM设备支持MVB/CAN/串行链路三种接口;TRDPRIOM设备知此恨TRDP/CAN

- 基于NXP+FPGA永磁同步电机牵引控制单元(单板结构/机箱结构)

深圳信迈主板定制专家

轨道交通NXP+FPGAfpga开发边缘计算人机交互嵌入式硬件人工智能

永磁同步电机牵引控制单元(单板结构/机箱结构)永磁同步电机牵引控制单元(TCU-PMSM)用于牵引逆变器-永磁同步电机构成的牵引电传动系统,采用轴控方式。执行高性能永磁同步电机复矢量控制策略,具有响应迅速、有效可靠的防空转·滑行控制功能以及平稳、无冲击的带速重投技术。最大转矩电流比(MTPA)控制和弱磁控制用于轨道交通领域的PMSM的控制目标为:控制牵引电机提供足够大的转矩;控制牵引电机在保持恒定

- 全国产飞腾+FPGA架构,支持B码+12网口+多串电力通讯管理机解决方案

深圳信迈科技DSP+ARM+FPGA

飞腾+FPGA电力新能源fpga开发架构电力通讯管理机全国产

行业痛点:中国的电力网络已经成为当今世界覆盖范围最广、结构最为复杂的人造科技系统。随着国家和各部委颁布了一系列法律法规,如国家颁布的《中华人民共和国网络安全法》、工信部颁布的《工业控制系统信息安全防护指南》、发改委颁布的14号令《电力监控系统安全防护规定》、国家能源局颁布的《关于印发电力监控系统安全防护总体方案等安全防护方案和评估规范的通知》,凸显了电力行业的网络安全防护工作的重要性。基于电力行业

- 基于NXP+FPGA轨道交通3U机箱结构牵引控制单元

深圳信迈主板定制专家

轨道交通NXP+FPGAX86+FPGAfpga开发边缘计算人工智能大数据嵌入式硬件

基于NXP+FPGA轨道交通异步电机牵引控制单元(TCU-IM)异步电机牵引控制单元(TCU-IM)用于牵引逆变器-异步电机构成的牵引电传动系统,可采用车控或架控方式。执行高性能异步电机复矢量控制策略,具有响应迅速、有效可靠的防空转·滑行控制功能以及平稳、无冲击的带速重投技术。无速度传感器控制通过转速观察算法,推算出准确的转速和转子位置,在实际应用中,达到省去速度传感器的目的,降低成本并减少故障点

- petalinxu 在zynq的FPGA下的ST7735S的驱动配置

qqssbb123

zynqpetalinuxdtsst7735

spi的接线:【TFT模块排针8】【开发板spi,gpio】【antminers9】VCC-----------3.3V-----------3.3VGND-----------GND-----------GNDBLK(背光)-------GPIO-----------BANK34_L4N_RXD2(w13;j2.12;gpio[2])RST(复位)-------GPIO-----------BA

- 4644 DCDC 电源芯片典型应用场景分析(详细版)

国科安芯

科普fpga开发

4644DCDC电源是一款高集成度、四输出的降压型模组稳压器,专为需要低纹波和高效率的供电场合设计,如FPGA、DSP等供电。本文将探讨如何利用4644电源芯片的特性实现FPGA、DSP等SERDES供电的优化设计。FPGA因其高速性和灵活性,在数据通信领域得到广泛应用。FPGA对电源的要求极为严格,需要低纹波、高稳定性的电源供应以保证信号的完整性和系统的性能。4644电源芯片以其高集成度和优异的

- [Vivado] IP核学习之Block Memory Generator

奕天者

FPGA学习学习fpga开发ip

具体参考Xilinx文档,pg058-blk-mem-genVersion8.4。一、BlockMemoryGenerator有什么用?BlockMemoryGenerator是Vivado中的IP核,即块存储器生成器。BlockMemoryGeneratorIP核是一种高级内存构造器,可使用Xilinxfpga中的嵌入式块RAM资源来生成面积和性能优化的内存空间。BlockMemoryGener

- FPGA 学习笔记:Vivado 2020.2 MicroBlaze MIG 测试 DDR3 篇二

zhangsz_sh

FPGA开发技术fpga开发学习

前言因为FPGADDR3测试的工程搭建步骤比较的多,所以分成几篇来写,这样利于把复杂的事情拆分,利于理解与实际的操作上一篇搭建了初步的HelloWorld工程,还没写什么代码或者改什么配置,所以FPGA开发,并不是上来就写VerilogHDL,而是要把更多的时间用在:目标是什么?DDR3测试,正常DDR3能否当RAM一样使用清楚要做什么,这里通过搭建嵌入式软核处理器的方式,快速验证实现与验证:搭建

- FPGA行业三大岗位详细介绍,0基础入门必读

博览鸿蒙

FPGAfpga开发

很多人想要转行FPGA,但不知道该如何选择岗位,也不了解这些岗位的具体工作内容以及需要哪些技能?选择合适的岗位对职业发展至关重要,尤其是在FPGA行业,选择时需要根据自己的条件和兴趣来定位岗位。前端设计工程师读文档,写文档:数字前端设计工程师需要阅读大量的协议文档,如PCIe、Ethernet、USB等,文档内容涉及到硬件协议、设计需求等。工作中,文档的编写和理解是非常重要的,比如Function

- 绿色算力网络构建与智能调度实践

智能计算研究中心

其他

内容概要绿色算力网络的构建需以能效优化为核心,通过智能调度系统实现算力资源的高效整合与动态分配。当前架构设计包含三大核心模块:异构计算集群(涵盖GPU、FPGA及量子计算单元)、跨区域网络互联协议(适配东数西算的传输需求)以及能耗监测平台(基于实时数据建模的碳足迹追踪)。下表示例展示了典型算力节点的关键参数对比:节点类型计算密度(TFLOPS/m²)功耗比(TOPS/W)延迟控制(ms)量子计算集

- 算力安全创新驱动未来趋势endofsentence

智能计算研究中心

其他

内容概要算力安全与技术创新正在重塑全球算力生态,其核心驱动力来自异构计算、边缘计算及量子计算等前沿技术的深度融合。当前算力架构正经历从集中式向分布式演进,通过异构加速芯片、动态资源调度算法及绿色能效优化,显著提升算力基础设施的可扩展性与可靠性。例如,异构计算通过CPU、GPU、FPGA的协同加速,使复杂模型训练效率提升40%以上。关键数据:根据IDC预测,到2025年全球智能算力需求将增长30倍,

- 从基础到实践(十三):无源晶振和有源晶振的应用指南

硬件进化论

php开发语言硬件工程人工智能模块测试

无源晶振与有源晶振是电子系统的核心时钟源,共同支撑现代数字设备的精准运行。无源晶振因结构简单、成本低、功耗小,广泛用于基础时钟生成(如MCU、消费电子),但其依赖外部电路设计,稳定性受环境制约。有源晶振集成振荡电路,直接输出稳定时钟信号,具备高精度(±0.1ppm)、低抖动、抗干扰强等特性,是通信设备(5G基站)、卫星导航、高速接口(PCIe/USB)等高性能场景的刚需。二者在成本、精度、复杂度上

- FPGA学习——verilog捕捉信号上升沿下降沿

or_to

FPGAfpga开发学习

在FPGA使用中,常常需要进行信号的边沿检测,如在串口通信中,需要检测接收信号的下降沿来判断串口的的起始位。常用的方法就是:设计两个一位的寄存器,用来接收被检测的信号,系统时钟来一次记一次输入信号,如果用了两个寄存器直接异或就可以了;使用高频的时钟对信号进行采样,因此要实现上升沿检测,时钟频率至少要在信号最高频率的2倍以上,否则就可能出现漏检测。代码如下:moduleedge_detect(sys

- IBUF和BUFG

起床学FPGA

fpga开发

在代码中,DATA_IN和CLK_IN都通过IBUF实例进行缓冲。IBUF负责将外部信号转换到FPGA内部标准并驱动内部信号线。这不仅在物理上是必要的一步(没有IBUF就无法直接驱动内部逻辑),而且还允许我们指定引脚的约束(如电平标准等)。BUFG全局时钟缓冲:bufg_clk实例将时钟连接到了全局时钟网络。这样做的直接好处是降低时钟的偏斜(skew)和抖动(jitter)。时钟偏斜指FPGA内不

- FPGA学习篇——Verilog学习4(常见语句)

ooo-p

Verilog学习fpga开发学习

1.1结构语句结构语句主要是initial语句和always语句,initial语句它在模块中只执行一次,而always语句则不断重复执行,以下是一个比较好解释的图:(图片来源于知乎博主罗成,画的很好很直观!)1.1.1initial语句initial语句它在模块中只执行一次。它常用于测试文件的编写,用来产生仿真测试信号(激励信号),或者用于对存储器变量赋初值。语法格式:initialbegin.

- FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

贾saisai

FPGA学习fpga开发学习1024程序员节

FPGA系列文章目录一、FPGA学习笔记(一)入门背景、软件及时钟约束二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)三、FPGA学习笔记(三)流水灯入门FPGA设计流程四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真六、FPGA学习笔记(六)Modelsim单独仿真和Quartus

- FPGA面试前该做哪些准备?一文为你讲解清楚

博览鸿蒙

FPGAfpga开发

很多人在面试FPGA工程师岗位前感到焦虑,不知道该如何准备,尤其是第一次参加面试时更容易紧张。那么,FPGA面试前该做哪些准备?如何才能充分展现自己的能力?本文将从面试准备、技术要点和常见面试问题三个方面,帮助你理清思路,从容应对面试。一.了解FPGA设计流程在面试FPGA工程师岗位时,首先需要清楚FPGA开发的完整流程,从前期需求分析到最终实现的每个环节都可能成为面试官考察的重点。以下是一个典型

- Verilog学习方法—基础入门篇(一)

博览鸿蒙

FPGAfpga开发

前言:在FPGA开发中,VerilogHDL(硬件描述语言)是工程师必须掌握的一项基础技能。它不仅用于描述数字电路,还广泛应用于FPGA的逻辑设计与验证。对于初学者来说,掌握Verilog的核心概念和基本语法,是深入FPGA开发的第一步。本篇文章将从Verilog基础入门的角度,帮助你快速建立学习框架,逐步掌握Verilog的使用方法。1.了解Verilog的基本概念1.1什么是Verilog?V

- FPGA 的 LBC 总线详解

美好的事情总会发生

接口FPGA嵌入式硬件硬件工程linux

1.LBC总线的定义LBC总线(LocalBusController,局部总线控制器)是FPGA(现场可编程门阵列)中用于高速连接处理器核(如PowerPC、MicroBlaze)与外部设备的并行总线接口。核心作用:提供低延迟、高带宽的数据传输通道,支持处理器与外部存储器(如Flash、SRAM)、外设控制器(如GPIO、UART)的直接通信。典型应用:嵌入式系统、工业控制、通信设备中,用于扩展F

- 高速PCB设计(布局规划)

四代目 水门

高速PCB设计学习笔记fpga开发嵌入式硬件

高速PCB设计笔记以下基于用户提供的结构设计流程与高速PCB设计规范整合,结合行业最佳实践与信号完整性原则,总结关键设计要点:一、设计规划与功能梳理1.核心功能模块划分项目类型识别:明确单板类型(数字/模拟/射频/电源等),划分输入/输出模块、电源模块、信号处理模块、时钟/复位模块。核心器件定位:聚焦FPGA、DSP、高速ADC/DAC、时钟芯片等,优先布局以缩短关键信号路径。2.设计要求确认电源

- 使用Modelsim手动仿真

寒听雪落

FPGA专栏_verilogfpga开发

FPGA设计流程在设计输入之后,设计综合前进行RTL级仿真,称为综合前仿真,也称为前仿真或功能仿真。前仿真也就是纯粹的功能仿真,主旨在于验证电路的功能是否符合设计要求,其特点是不考虑电路门延迟与线延迟。在完成一个设计的代码编写工作之后,可以直接对代码进行仿真,检测源代码是否符合功能要求。这时,仿真的对象为HDL代码,可以比较直观的观察波形的变化,在设计的最初阶段发现问题,节省大量的精力。在布局布线

- ViewController添加button按钮解析。(翻译)

张亚雄

c

<div class="it610-blog-content-contain" style="font-size: 14px"></div>// ViewController.m

// Reservation software

//

// Created by 张亚雄 on 15/6/2.

- mongoDB 简单的增删改查

开窍的石头

mongodb

在上一篇文章中我们已经讲了mongodb怎么安装和数据库/表的创建。在这里我们讲mongoDB的数据库操作

在mongo中对于不存在的表当你用db.表名 他会自动统计

下边用到的user是表明,db代表的是数据库

添加(insert):

- log4j配置

0624chenhong

log4j

1) 新建java项目

2) 导入jar包,项目右击,properties—java build path—libraries—Add External jar,加入log4j.jar包。

3) 新建一个类com.hand.Log4jTest

package com.hand;

import org.apache.log4j.Logger;

public class

- 多点触摸(图片缩放为例)

不懂事的小屁孩

多点触摸

多点触摸的事件跟单点是大同小异的,上个图片缩放的代码,供大家参考一下

import android.app.Activity;

import android.os.Bundle;

import android.view.MotionEvent;

import android.view.View;

import android.view.View.OnTouchListener

- 有关浏览器窗口宽度高度几个值的解析

换个号韩国红果果

JavaScripthtml

1 元素的 offsetWidth 包括border padding content 整体的宽度。

clientWidth 只包括内容区 padding 不包括border。

clientLeft = offsetWidth -clientWidth 即这个元素border的值

offsetLeft 若无已定位的包裹元素

- 数据库产品巡礼:IBM DB2概览

蓝儿唯美

db2

IBM DB2是一个支持了NoSQL功能的关系数据库管理系统,其包含了对XML,图像存储和Java脚本对象表示(JSON)的支持。DB2可被各种类型的企 业使用,它提供了一个数据平台,同时支持事务和分析操作,通过提供持续的数据流来保持事务工作流和分析操作的高效性。 DB2支持的操作系统

DB2可应用于以下三个主要的平台:

工作站,DB2可在Linus、Unix、Windo

- java笔记5

a-john

java

控制执行流程:

1,true和false

利用条件表达式的真或假来决定执行路径。例:(a==b)。它利用条件操作符“==”来判断a值是否等于b值,返回true或false。java不允许我们将一个数字作为布尔值使用,虽然这在C和C++里是允许的。如果想在布尔测试中使用一个非布尔值,那么首先必须用一个条件表达式将其转化成布尔值,例如if(a!=0)。

2,if-els

- Web开发常用手册汇总

aijuans

PHP

一门技术,如果没有好的参考手册指导,很难普及大众。这其实就是为什么很多技术,非常好,却得不到普遍运用的原因。

正如我们学习一门技术,过程大概是这个样子:

①我们日常工作中,遇到了问题,困难。寻找解决方案,即寻找新的技术;

②为什么要学习这门技术?这门技术是不是很好的解决了我们遇到的难题,困惑。这个问题,非常重要,我们不是为了学习技术而学习技术,而是为了更好的处理我们遇到的问题,才需要学习新的

- 今天帮助人解决的一个sql问题

asialee

sql

今天有个人问了一个问题,如下:

type AD value

A

- 意图对象传递数据

百合不是茶

android意图IntentBundle对象数据的传递

学习意图将数据传递给目标活动; 初学者需要好好研究的

1,将下面的代码添加到main.xml中

<?xml version="1.0" encoding="utf-8"?>

<LinearLayout xmlns:android="http:/

- oracle查询锁表解锁语句

bijian1013

oracleobjectsessionkill

一.查询锁定的表

如下语句,都可以查询锁定的表

语句一:

select a.sid,

a.serial#,

p.spid,

c.object_name,

b.session_id,

b.oracle_username,

b.os_user_name

from v$process p, v$s

- mac osx 10.10 下安装 mysql 5.6 二进制文件[tar.gz]

征客丶

mysqlosx

场景:在 mac osx 10.10 下安装 mysql 5.6 的二进制文件。

环境:mac osx 10.10、mysql 5.6 的二进制文件

步骤:[所有目录请从根“/”目录开始取,以免层级弄错导致找不到目录]

1、下载 mysql 5.6 的二进制文件,下载目录下面称之为 mysql5.6SourceDir;

下载地址:http://dev.mysql.com/downl

- 分布式系统与框架

bit1129

分布式

RPC框架 Dubbo

什么是Dubbo

Dubbo是一个分布式服务框架,致力于提供高性能和透明化的RPC远程服务调用方案,以及SOA服务治理方案。其核心部分包含: 远程通讯: 提供对多种基于长连接的NIO框架抽象封装,包括多种线程模型,序列化,以及“请求-响应”模式的信息交换方式。 集群容错: 提供基于接

- 那些令人蛋痛的专业术语

白糖_

springWebSSOIOC

spring

【控制反转(IOC)/依赖注入(DI)】:

由容器控制程序之间的关系,而非传统实现中,由程序代码直接操控。这也就是所谓“控制反转”的概念所在:控制权由应用代码中转到了外部容器,控制权的转移,是所谓反转。

简单的说:对象的创建又容器(比如spring容器)来执行,程序里不直接new对象。

Web

【单点登录(SSO)】:SSO的定义是在多个应用系统中,用户

- 《给大忙人看的java8》摘抄

braveCS

java8

函数式接口:只包含一个抽象方法的接口

lambda表达式:是一段可以传递的代码

你最好将一个lambda表达式想象成一个函数,而不是一个对象,并记住它可以被转换为一个函数式接口。

事实上,函数式接口的转换是你在Java中使用lambda表达式能做的唯一一件事。

方法引用:又是要传递给其他代码的操作已经有实现的方法了,这时可以使

- 编程之美-计算字符串的相似度

bylijinnan

java算法编程之美

public class StringDistance {

/**

* 编程之美 计算字符串的相似度

* 我们定义一套操作方法来把两个不相同的字符串变得相同,具体的操作方法为:

* 1.修改一个字符(如把“a”替换为“b”);

* 2.增加一个字符(如把“abdd”变为“aebdd”);

* 3.删除一个字符(如把“travelling”变为“trav

- 上传、下载压缩图片

chengxuyuancsdn

下载

/**

*

* @param uploadImage --本地路径(tomacat路径)

* @param serverDir --服务器路径

* @param imageType --文件或图片类型

* 此方法可以上传文件或图片.txt,.jpg,.gif等

*/

public void upload(String uploadImage,Str

- bellman-ford(贝尔曼-福特)算法

comsci

算法F#

Bellman-Ford算法(根据发明者 Richard Bellman 和 Lester Ford 命名)是求解单源最短路径问题的一种算法。单源点的最短路径问题是指:给定一个加权有向图G和源点s,对于图G中的任意一点v,求从s到v的最短路径。有时候这种算法也被称为 Moore-Bellman-Ford 算法,因为 Edward F. Moore zu 也为这个算法的发展做出了贡献。

与迪科

- oracle ASM中ASM_POWER_LIMIT参数

daizj

ASMoracleASM_POWER_LIMIT磁盘平衡

ASM_POWER_LIMIT

该初始化参数用于指定ASM例程平衡磁盘所用的最大权值,其数值范围为0~11,默认值为1。该初始化参数是动态参数,可以使用ALTER SESSION或ALTER SYSTEM命令进行修改。示例如下:

SQL>ALTER SESSION SET Asm_power_limit=2;

- 高级排序:快速排序

dieslrae

快速排序

public void quickSort(int[] array){

this.quickSort(array, 0, array.length - 1);

}

public void quickSort(int[] array,int left,int right){

if(right - left <= 0

- C语言学习六指针_何谓变量的地址 一个指针变量到底占几个字节

dcj3sjt126com

C语言

# include <stdio.h>

int main(void)

{

/*

1、一个变量的地址只用第一个字节表示

2、虽然他只使用了第一个字节表示,但是他本身指针变量类型就可以确定出他指向的指针变量占几个字节了

3、他都只存了第一个字节地址,为什么只需要存一个字节的地址,却占了4个字节,虽然只有一个字节,

但是这些字节比较多,所以编号就比较大,

- phpize使用方法

dcj3sjt126com

PHP

phpize是用来扩展php扩展模块的,通过phpize可以建立php的外挂模块,下面介绍一个它的使用方法,需要的朋友可以参考下

安装(fastcgi模式)的时候,常常有这样一句命令:

代码如下:

/usr/local/webserver/php/bin/phpize

一、phpize是干嘛的?

phpize是什么?

phpize是用来扩展php扩展模块的,通过phpi

- Java虚拟机学习 - 对象引用强度

shuizhaosi888

JAVA虚拟机

本文原文链接:http://blog.csdn.net/java2000_wl/article/details/8090276 转载请注明出处!

无论是通过计数算法判断对象的引用数量,还是通过根搜索算法判断对象引用链是否可达,判定对象是否存活都与“引用”相关。

引用主要分为 :强引用(Strong Reference)、软引用(Soft Reference)、弱引用(Wea

- .NET Framework 3.5 Service Pack 1(完整软件包)下载地址

happyqing

.net下载framework

Microsoft .NET Framework 3.5 Service Pack 1(完整软件包)

http://www.microsoft.com/zh-cn/download/details.aspx?id=25150

Microsoft .NET Framework 3.5 Service Pack 1 是一个累积更新,包含很多基于 .NET Framewo

- JAVA定时器的使用

jingjing0907

javatimer线程定时器

1、在应用开发中,经常需要一些周期性的操作,比如每5分钟执行某一操作等。

对于这样的操作最方便、高效的实现方式就是使用java.util.Timer工具类。

privatejava.util.Timer timer;

timer = newTimer(true);

timer.schedule(

newjava.util.TimerTask() { public void run()

- Webbench

流浪鱼

webbench

首页下载地址 http://home.tiscali.cz/~cz210552/webbench.html

Webbench是知名的网站压力测试工具,它是由Lionbridge公司(http://www.lionbridge.com)开发。

Webbench能测试处在相同硬件上,不同服务的性能以及不同硬件上同一个服务的运行状况。webbench的标准测试可以向我们展示服务器的两项内容:每秒钟相

- 第11章 动画效果(中)

onestopweb

动画

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- windows下制作bat启动脚本.

sanyecao2314

javacmd脚本bat

java -classpath C:\dwjj\commons-dbcp.jar;C:\dwjj\commons-pool.jar;C:\dwjj\log4j-1.2.16.jar;C:\dwjj\poi-3.9-20121203.jar;C:\dwjj\sqljdbc4.jar;C:\dwjj\voucherimp.jar com.citsamex.core.startup.MainStart

- Java进行RSA加解密的例子

tomcat_oracle

java

加密是保证数据安全的手段之一。加密是将纯文本数据转换为难以理解的密文;解密是将密文转换回纯文本。 数据的加解密属于密码学的范畴。通常,加密和解密都需要使用一些秘密信息,这些秘密信息叫做密钥,将纯文本转为密文或者转回的时候都要用到这些密钥。 对称加密指的是发送者和接收者共用同一个密钥的加解密方法。 非对称加密(又称公钥加密)指的是需要一个私有密钥一个公开密钥,两个不同的密钥的

- Android_ViewStub

阿尔萨斯

ViewStub

public final class ViewStub extends View

java.lang.Object

android.view.View

android.view.ViewStub

类摘要: ViewStub 是一个隐藏的,不占用内存空间的视图对象,它可以在运行时延迟加载布局资源文件。当 ViewSt