基于FPGA的多路TS流复用

一、一些基本概念

1.数据流的分类:数据流主要分为以下三种

①ES流(elementary stream):基本码流。包含视频、音频或数据的连续码流,为音视频层的负载单元(音视频采集编码后等待打包的单元)。可以是视频一帧。

②PES流(packet ES):打包后的基本码流。将ES流根据需要分成长度不等的数据包并加上包头,为视频编码层之上的单元。在PS流中PES最大为65535B,分包存储界限为2B(2^16),在TS流中没有大小限制(按188B分割,不满188B的TS包由填充字段补满)。已插入PTS和DTS,一般一个PES是一帧图像。PES层的类型区别为stream_id。

③TS流(transport stream):传输流。固定长度为188B,含有独立时基的一个或多个节目,适用于误码较多的环境。TS的传输速率是可变的,由其节目时钟参考PCR决定,PCR有时也单独封装成一个TS包。TS层类型区别为PID。

2.TS包有效负载的信息主要有四类:

①音视频和PES包及附加数据;

②描述单路节目信息的PMT和描述多路节目复用信息的PAT及对接收系统所要求的条件访问表CAT;

③网络信息表NIT、业务描述表SDT、节目段信息表EIT、时间日期表TDT等,以上几种表均为强制性的;

④DVB数据广播信息。

3.补充说明:

①PSI(program special information):节目特殊信息。TS把PES和PSI封装成188B单位的TS流。PSI包括PMT和PAT。

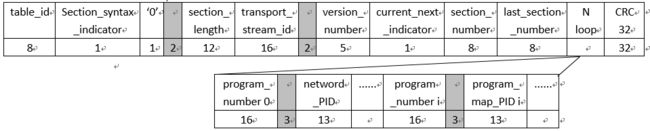

②PAT(program association table):用于描述当前TS流中有多少个节目、每个节目的PMT的PID是多少。TS流需要周期发送PAT信息,而PS流则只有一个PAT。PAT整体字头长为8B,其中的program_map_PID字段为PMT的PID。PAT需要单独封装成一个TS包。

③PMT(program map table):TS流中每路节目均对应一个PMT表。PMT表中包含当前节目所包含的音视频流信息,包括PID信息。PMT整体字头长为12B,其中的elementary_PID为对应音视频的PID。PMT需要单独封装成一个TS包。

④PTS(presentation time stamp):播出时间标记,是最基本的时间标记,它规定在某时刻应从解码器缓冲区中删除一个访问单元,并解码和播放。

⑤DTS(decoding time stamp):解码时间标记,它规定在某时刻应从解码器缓冲区中删除一个访问单元并解码,但不播放,而是临时性缓存以备以后播放。DTS不会单独出现,总是伴随着一个PTS(规定该临时性缓存的图像何时播放)。

⑥PCR:每套节目的时钟采样成为PCR,能使解码器时钟与待解码器的节目时钟同步。编码器有一个系统时钟,用来生成一个共同时序使音/视频正确解码和播放。一般为44比特。

⑦CAT、NIT、SDT、EIT的PID分别为:0x01、0x10、0x11、0x12。

4.如何获取TS包中音视频数据:

①先遍历TS包,找到包头PID为0的TS包,该包为PAT,其中包含PMT的PID号;

②通过该PID找到对应PMT,PMT中包含了video/audio TS包的PID和codec,指示了数据所在位置和选用何种解码器;

③遍历这些TS包,找到第一个包中payload_unit_start_indicator字段为1的包,直到下一个payload_unit_start_indicator字段为1的包,这些中间的TS包组成一个PES(一帧数据)。

二、基本流程及各数据结构

1.打包复用基本流程:如下图

2.TS包结构:

3.PES包结构:

①包起始码前缀(packet start code prefix):是一个固定码字结构,值为0x000001,用于收发PES同步。

②PES包长度(PES packet length):长度可变,最大为65535B,TS流中设为0表示包长大于65535。

③PES包头(optional PES HEADER):包含PTS和DTS。

4.PAT包结构:

5.PMT包结构:

三、多路复用原理

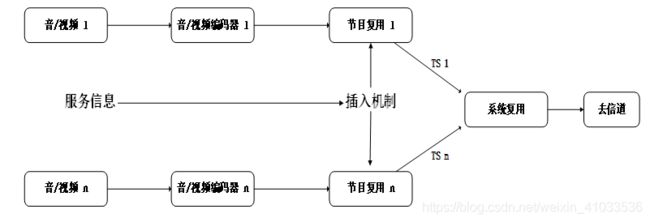

多路复用主要分为音/视频PES包的节目复用和TS包的系统复用,大体流程如下图:

1.音频PES包长度恒定,视频PES包长度可变。

2.节目复用:将V-ES/A-ES通过打包器打包成V-PES/A-PES(V-PES一般一帧一个PES包,而A-PES一般不超过64kb)。与PSI插入、附加数据共同经过编码器节目复用,赋予并插入PID,形成188B的TS传送包。

3.系统复用:先对各路节目的PID、PSI、PCR等值进行滤波处理,对不同节目可能出现的相同PID值进行修改,产生复用后新的PSI,插入符合DVB-SI规范的SI信息,并在携带调整字段的TS包中判断PCR值进行校正。该过程也叫信道复用。

4.系统层的PCR域调整和PSI信息重构,是系统复用的两项关键技术。当多路TS复用成一路TS流时,先将各路TS流的PSI进行搜集和码流分析,丢弃原有PSI信息并修改多路TS流中冲突的PID。

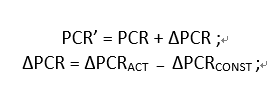

5.PCR的抖动需要在带有PCR标志的TS包离开复用器时进行校验。设PCR为输入TS流的PCR,PCR’为校正后的PCR,∆PCRACT为PCR实际延迟,∆PCRCONST为PCR固定延迟,则计算公式如下:

四、基于FPGA的复用器设计

基于FPGA的复用器大体有两种设计思路,一是完全通过逻辑电路实现功能,该方法更稳定,速率也更高,但设计复杂度更高,功能也相对简;二是逻辑电路只完成硬件所需操作,而各类操作指令的判定与生成交由NIOS完成,该方法功能更丰富,可复用性更高,但更容易受硬件环境影响。以下主要介绍第一种设计思路,分为预处理部分、输入部分和复用部分。

1.预处理部分:包括同步检测模块、PSI提取模块和PSI修改模块

2.输入部分:由并行接口、包检测模块、PCR检测模块及输入FIFO组成

①包检测:PID=0x0000为PAT,PID=0x1fff为空包,空包与PAT不写入输入FIFO。

②复用缓存:包括输入与输出FIFIO。输入FIFO的参考大小设计为376B(两帧TS流长度),必须支持异步读写功能,它是一个双端RAM,可同时进行读写,有一个写时钟和一个读时钟。

一般把clk_W转变为一个由clk_R触发的W_en,用读时钟为基准时钟来控制读写。当FIFO缓存超过188B时,产生一个半满信号给复用控制模块,产生读使能读出数据。

③重构的PAT从PMT中读复用标志。若选择复用则将PID和PMT_PID写入,再加上4B的CRC检验字段,用0xff填充至188B。复用控制模块每40ms发一个读使能,将重构好的PAT包写入输出FIFO。

3.复用控制逻辑:包括中断模块、复用控制模块、输出FIFO、空包写入模块、PAT插入及PCR修正模块。控制模块检测0~n个FIFO是否有半满信号,若有则发送该路TS流至输出FIFO,否则发送空包(有空包包头和0x0组成),并以T=40ms的周期发送重构的PAT。

4.PCR校正:PCR补偿计数器由两部分组成,一部分为9比特计数器,对本地时钟(27MHZ)计数;另一部分是33比特计数器,对本地时钟的300分频(90kHZ)计数。对PCR的校正即为在TS包的PCR域离开复用器时,在原有PCR上加上该TS包在复用器中实际经历时间∆PCR(一般直接用∆PCRACT代替∆PCR)。