- 山东大学FPGA课程实验一 加法器设计

小田不甜~

fpga开发

【实验题目】设计一个16位二进制全加器模块。用层次化设计方法,设计一个16位二进制全加器模块。设计一个16位二进制超前进位全加器模块。设计一个16-bit8421-BCD码全加器模块。【实验软件工具】QuartusII;ModelSimSE.【实验要求】实验内容与原理说明(包括框图、逻辑表达式和真值表);实验模块程序代码(设计模块DesignBlock)和激励代码(激励模块TestBench);仿

- FPGA设计的时序分析概要

cycf

FPGA之道fpga开发

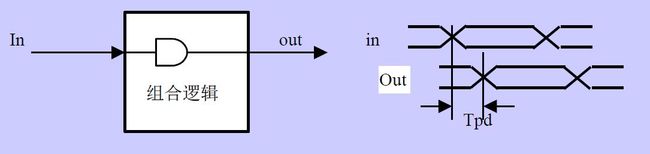

FPGA设计的时序分析文章目录FPGA设计的时序分析时序分析的概念和必要性时序分析的分类映射后时序分析时序约束与时序分析的关系特殊情况小总结时序分析的概念和必要性时序分析,也叫静态时序分析(StaticTimingAnalysis,简称STA),它通过完整的分析方式判断IC是否能在使用者的时序环境下正常工作,为确保IC品质提供了一个很好的解决方案。也许有人会问,我的FPGA设计已经通过了功能仿真,

- Xilinx FPGA ICAP原语实现多重配置

whik1194

ISEVivadoMicroBlaze系列教程FPGAxilinxICAPMultiboot多重配置

文章目录1.FPGA可以运行几个固件2.XilinxICAP原语简介3.ICAP原语模板的使用4.ICAP在Spartan-6上的使用5.ICAP在Kintex-7上的使用工程下载1.FPGA可以运行几个固件众所周知,常见的FPGA通常为SRAM结构,固件程序一般存放在外置的串行Flash中,比如SPIFlash,M25P16或N25Q128等。FPGA启动时,一般先从SPI起始地址开始加载数据到

- 基于 Kintex UltraScale 系列 2 路 QSFP+40G 光纤 PCIe 数据传输卡 / 光纤适配器(5GByte/s 带宽KU060光纤 PCIe 数据传输卡)

F_white

数据中心视频与图像采集处理机器视觉

PCIE732是一款基于PCIE总线架构的高性能数据传输卡,板卡具有1个PCIex8主机接口、2个QSFP+40G光纤接口,可以实现2路QSFP+40G光纤的数据实时采集、传输。板卡采用Xilinx的高性能KintexUltraScale系列FPGA作为实时处理器,板载2组独立的72位DDR4SDRAM大容量缓存。板卡具有1个RJ45千兆以太网口以及若干IO信号。一般应用于基于服务器的雷

- 中科亿海微SoM模组——基于FPGA+RSIC-V的计算机板卡

ehiway

fpga开发

基于FPGA+RSIC-V的计算机板卡主芯片使用中科亿海微EQ6HL45-CSG324FPGA芯片和高性能微控制器HPM6880,并集合ADCLHA6958H、6通道数字隔离器SiLM5760、SiLM5763、内存W634GU6QB等器件,板卡实现了大容量配置存储等功能的融合,为模拟信号采集、数字信号处理、逻辑控制等应用提供高性能混合信号处理通用硬件平台。图板卡硬件整体框图图板卡实物图EQ6HL

- mb_bootloop_le.elf是使用microblaze默认的elf文件,这个文件包括哪些内容?

hahaha6016

硬件设计fpga开发

一、mb_bootloop_le.elf说明1.mb_bootloop_le.elf是使用microblaze的FPGA的时候的默认的elf文件;2.XilinxSDK中的.elf文件全称为“ExecutableandLinkingFormat”(ELF)文件3.fpga开发中xilinxsdk的elf文件就是arm程序文件;elf文件大小就决定了你的堆栈大小要分配多大二、mb_bootloop

- 可编程逻辑器件的演进与对比分析

cycf

FPGA之道fpga开发

可编程逻辑器件的演进与对比分析目录离散逻辑芯片与早期PLD的限制CPLD的诞生与结构特点FPGA的架构创新CPLD与FPGA的核心差异总结1.离散逻辑芯片与早期PLD的限制在还没有发明出可编程逻辑器件(PLD:ProgrammableLogicDevice)之前,设计师们只能使用一些专用的小芯片来搭建系统,这些小芯片被称为离散逻辑芯片。这些早期的PLD产品日渐不能满足人们的需求,于是新的可编程逻辑

- Linux configfs机制

liujiliei

1、在使用intelSOC过程中,驱动的DTS需要在内核启动以后把FPGAcoreload以后加载PL侧设备的DTS,此时使用的是Linux的dts的overlay机制,该机制本质是使用Linux的configfs机制,在此分析。2、Linux内核驱动中使用的设备树作为驱动match的方法,在内核初始化时候会对dts解析,然后生成一个个的devicenode,根据node中的compatile与d

- FPGA和嵌入式系统的核心区别

2301_82243800

fpga开发

灵活性:FPGA具有高度的灵活性,可以根据需要重新编程以实现不同的功能。嵌入式系统的硬件功能通常是固定的,无法进行大规模的硬件级别的修改。开发周期:FPGA的开发周期相对较短,因为它可以通过重新编程来实现新功能,快速原型设计和迭代能力可以缩短开发周期。嵌入式系统的开发周期相对较长,因为它需要进行硬件设计、芯片制造和软件开发等多个环节。性能:FPGA芯片具有并行处理的能力,可以实现高性能计算和数据处

- [FPGA]嵌入式系统FPGA设计资源

元直数字电路验证

数模混合电路设计与仿真fpga开发嵌入式硬件

嵌入式系统FPGA设计资源一、供应商https://www.altera.com-AlteraFPGA供应商网站https://www.altera.com/events/northamerica/intel-soc-fpga-developer-forum/overview.html-SoC开发人员论坛https://www.altera.com/content/dam/altera-www/g

- FPGA(现场可编程门阵列)是什么?

Yashar Qian

#嵌入式fpga开发计算机体系结构嵌入式硬件

FPGA(现场可编程门阵列)是什么?FPGA(现场可编程门阵列,Field-ProgrammableGateArray)是一种可通过编程配置硬件电路的半导体芯片,其核心特点是硬件逻辑可重构,既能像软件一样灵活修改,又能像专用芯片(ASIC)一样高效运行。以下是通俗易懂的解析:⚙️术语拆解Field-Programmable(现场可编程):芯片出厂后,用户可通过硬件描述语言(如Verilog/VHD

- 异构计算解决方案(兼容不同硬件架构)

ARM2NCWU

硬件架构

异构计算解决方案通过整合不同类型处理器(如CPU、GPU、NPU、FPGA等),实现硬件资源的高效协同与兼容,满足多样化计算需求。其核心技术与实践方案如下:一、硬件架构设计异构处理器组合主从协作模式:采用通用CPU(如ARMCortex-M3)作为主处理器,搭配专用协处理器(如MSP430微控制器)处理特定任务(如射频通信),通过串口/USB/以太网实现通信。众核架构:集成CPU、GPU、N

- FPGA与Verilog实现的Cordic算法测试项目

weixin_42668301

本文还有配套的精品资源,点击获取简介:Cordic算法是一种在FPGA和Verilog硬件描述语言中实现高效的数值计算技术,它简化了硬件资源需求,特别适合资源有限的嵌入式系统。通过模块化设计,Cordic算法可以拆分为多个子模块来实现,包括旋转步骤、误差校正和控制逻辑等。该算法通过迭代过程逼近目标值,无需乘法器,从而减少了硬件资源消耗并提高了效率。在实现时需要考虑位宽、迭代次数和误差处理等因素,以

- 实时解码技术:基于FPGA芯片的即时错误诊断与修正系统,实现计算过程中的动态纠错

百态老人

fpga开发

以下基于资料构建的基于FPGA的实时动态纠错系统技术框架,涵盖原理、实现路径与典型应用:一、FPGA芯片的核心特性支撑实时动态纠错FPGA(现场可编程门阵列)的硬件可重构性和并行架构是动态纠错系统的物理基础:可编程逻辑单元(CLB)与分布式计算:FPGA内部由可配置逻辑块(CLB)和查找表(LUT)构成,支持并行执行多个逻辑运算,为实时错误检测提供硬件级并发能力。计算过程分散在空间分布的基本单元中

- 零起步的 FPGA 学习圣经:Project F 开源项目深度解读

OpenFPGA

fpga开发学习

在FPGA学习过程中,你是否也曾遇到过这些问题:教材晦涩难懂,电路图和代码脱节?找不到既系统又实战的开源学习资料?工具链配置复杂,不知从何下手?如果你点头了,那么今天推荐的开源项目ProjectF,可能就是你期待已久的答案。什么是ProjectF?ProjectF是一个完全开源的、面向学习者的FPGA教程项目,由英国开发者WillGreen维护,旨在帮助开发者从零开始学习数字逻辑和硬件设计。项目口

- 基于FPGA的数字图像处理【1.5】

BinaryStarXin

FPGA图像处理fpga开发FPGA与图像处理FPGA技术优势硬件工程dsp开发射频工程驱动开发

第2章FPGA与图像处理随着图像分辨率的大幅度提升和图像处理算法复杂度的提升,传统的串行处理器已经越来越不能满足图像处理的实时性需求。多核结构处理、GPU处理及FPGA很快在实时性图像处理领域得到了迅速的发展。本章将重点介绍基于FPGA的实时性图像处理。FPGA通过为每个功能建立单独的硬件来实现整个应用程序所需要的逻辑功能,这使其很适合图像处理,尤其是采用流水线来处理视频流,可以在同一个时刻进行多

- 【教程4>第7章>第23节】基于FPGA的RS(204,188)译码verilog实现7——欧几里得迭代算法模块

fpga和matlab

#第7章·通信—信道编译码fpga开发RS译码欧几里得迭代教程4

目录1.软件版本2.RS译码器逆元欧几里得算法模块原理分析3.RS译码器逆元欧几里得算法模块的verilog实现3.1RS译码器逆元欧几里得算法模块verilog程序3.2程序解析欢迎订阅FPGA/MATLAB/Simulink系列教程《★教程1:matlab入门100例》《★教程2:fpga入门100例》《★教程3:simulink入门60例》

- FPGA的星辰大海

forgeda

fpga开发硬件架构SEUEmulationEDA硬件辅助验证商业航天

编者按时下风头正盛的DeepSeek,正值喜好宏大叙事的米国大统领二次上岗就业,OpenAI、软银、甲骨文等宣布投资高达5000亿美元“星际之门”之际,对比尤为强烈。某种程度上,,是低成本创新理念的直接落地。包括来自开源社区的诸多赞誉是,并非体现技术有多“超越”,而是让更多的人可以直接体验,把通往AGI的门票,从奢侈品变成了日用品。四十年前的上世纪八十年代初,美国发起的星球大战,高昂的重金投入比拼

- 基于高云GW5AT-15 FPGA的SLVS-EC桥MIPI设计方案分享

_Hello_Panda_

杂文随笔fpga开发SLVS-ECGW5ATMIPID-PHY

作者:Hello,Panda一、设计需求设计一个4LanesSLVS-EC桥接到2组4lanesMIPIDPHY接口的电路模块:(1)CMOS芯片:IMX537-AAMJ-C,输出4lanesSLVS-EC4.752GbpsLane速率;(2)FPGA:高云GW5AT-LV15MG132C1/I0;(3)输出:MIPID-PHY4lanes2.5Gbps一组+MIPID-PHY2.0Gbps一组,

- 基于ARM+FPGA+ADC的储能协调控制器/EMS,支持全国产,支持实时系统

深圳信迈主板定制专家

电力新能源人工智能网络fpga开发arm开发

协调控制器是一款灵活可定制逻辑的多功能控制装置,可根据实际应用环境需求定制对应的控制逻辑,应用范围广泛,既可作为新能源站(光伏、风电、储能)的协调控制器,也可作为微网控制器或者综合控制器。产品特点1、支持图形化逻辑组态工具实现装置接口信号、处理逻辑、输出控制及事故告警的现场可视化组态、程序升级,可根据现场需求灵活定制功能;2、具备多路信号采集、多路控制输出;3、具有多种通讯接口,具备强大快速的通信

- 7a系列mrcc xilinx_Xilinx 7 Series FPGA!型号列表

Xilinx7SeriesFPGA型号列表SupportedDevice(1),(2)CoreVersionSignalingEnvironmentVirtex-5XC5VFX70T-FF1136-2C/I(3)(regionalclock)v43.3VonlyVirtex-5XC5VLX50-FF1153-2C/I(3)(regionalclock)v43.3VonlyVirtex-5XC5VL

- XC7K160T-1FBG484I、XC7A100T-2CSG324I FPGA可编程门阵列 PDF规格书

Summer-明佳达电子

电子元器件fpga开发嵌入式硬件

1、XC7K160T-1FBG484I说明:Kintex®-7FPGA有-3、-2、-1、-1L和-2L速度等级,其中-3具有最高的性能。-2L器件被筛选为较低的最大静态功率,并且可以在较低的核心电压下运行,以获得比-2器件更低的动态功率。-2L工业(I)温度器件仅在VCCINT=0.95V下工作。-2L扩展(E)温度器件可以在VCCINT=0.9V或1.0V下工作。在VCCINT=1.0V下运行

- 调试HDMI音频能8通道播放声音

hxHardway

Android/Linux功能实现文档音视频linux

一、使用场景我们是通过rk主控的hdmi接口播放音视频给到ite68051芯片解析出8声道数据,分别通过4路i2s的数据脚给给到fpga去解析调试步骤:1.根据相关手册配置hdmi输出,hdmi声卡注册,如下:hdmi0_sound:hdmi0-sound{ status="disabled"; compatible="rockchip,hdmi"; rockchip,mclk-

- ModelSim在FPGA设计中的功能仿真与时序仿真

chao189844

fpga开发

在FPGA(现场可编程门阵列)设计的复杂流程中,仿真环节扮演着至关重要的角色。它不仅能够帮助设计师在物理实现之前发现并修正设计错误,还能通过模拟实际工作环境来评估设计的性能和稳定性。ModelSim作为业界领先的HDL(硬件描述语言)仿真工具,以其强大的功能、灵活的配置和直观的界面赢得了广泛的应用。本文将深入探讨ModelSim在FPGA设计中如何进行功能仿真和时序仿真,并介绍其在实际应用中的优势

- VIVADO导出仿真数据到MATLAB中进行分析

FPGA与信号处理

FPGA学习记录VIVADOSIMULATION导出仿真数据TXTMATLAB

VIVADO导出仿真数据到MATLAB中进行分析目录前言一、导出仿真数据需要编写的RTL代码二、MATLAB读入txt文件中的数据三、需要注意的点总结前言在使用XilinxVivado进行FPGA开发时,如何将RTL仿真生成的数据导出,进行进一步分析与可视化,是很多开发者常遇到的问题。Vivado自带仿真工具不支持直接导出仿真数据,但是我们可以通过编写一段简单的RTL代码即可将需要的仿真数据保存到

- VxWorks在Zynq平台上的移植详细流程

缪超争Lighthearted

VxWorks在Zynq平台上的移植详细流程【下载地址】VxWorks在Zynq平台上的移植详细流程本资源文档全面解析了将WindRiver的嵌入式操作系统VxWorks移植至XilinxZynq系列SoC平台的过程。Zynq平台以其独特的FPGA与ARMCortex-A处理单元结合的设计,广泛应用于工业控制、航空航天、通信设备等多个领域。本文档深入浅出,旨在帮助开发者理解和掌握如何在这一平台上成

- TeleScan PE

fei_sun

计算机网络单片机stm32嵌入式硬件

目录物理层深度剖析通道结构信号完整性关键技术链路训练(LinkTraining)协议层核心技术TLP(事务层包)结构虚拟通道管理原子操作(PCIe5.0+)硬件实现关键FPGA实现方案信号完整性设计规范总结:PCIe技术本质TeleScanPE是一个免费的PCIExpress/NVMe配置空间读/写实用程序,允许用户扫描、解码、显示和写入PCIExpress/NVMe配置空间寄存器。windows

- SPI代码详解FPGA-verilog部分(FPGA+STM32)(一)

MinJohnson

STM32FPGA/Verilogstm32fpgaspi

声明:本篇文章面向在已对SPI的四种时序有所了解的人我们采用SPI3模式以及将FPGA作从机,STM32作主机的方式讲解,在STM32控制部分采用的是半双工模式,但其实半双工与全双工区别不大,稍加修改即可本文章属于SPI的升级版,将原本的片选线CS_N再多加一根,变成spi_cs_cmd和spi_cs_data,当spi_cs_cmd拉低的时候表示传送的是命令(命令只由单片机发送),当cs_dat

- 混沌保密音频传输系统设计与评估

神经网络15044

算法大数据单片机音视频macos策略模式算法开发语言网络

混沌保密音频传输系统设计与评估摘要:本文设计并实现了一套基于混沌动力学的实时音频信号保密传输系统。系统核心采用改进型Rössler混沌系统产生密钥流,通过异或运算对音频信号进行加密/解密。详细阐述了系统架构、混沌电路实现、FPGA/微控制器平台部署方案,并制定了全面的评估指标体系(包括音频失真度、误码率、加密/解密时间、密钥空间、敏感性分析、统计特性等)。测试结果表明,该系统在保持音频质量的同时,

- FPGA基础 -- Verilog 锁存器简介

sz66cm

FPGA基础fpga开发

由浅入深地讲解Verilog中的锁存器(Latch)**,包括:什么是锁存器(定义与作用)锁存器的分类(透明锁存器vs边沿触发器)Verilog中锁存器的建模方式锁存器与触发器的区别锁存器的时序特性与设计陷阱实际应用与避免锁存器的最佳实践综合工具识别锁存器的方式与调试技巧一、什么是锁存器(Latch)?锁存器是一种电平敏感的时序逻辑单元,用于在特定控制信号(如enable或clk为高电平)时锁存输

- apache ftpserver-CentOS config

gengzg

apache

<server xmlns="http://mina.apache.org/ftpserver/spring/v1"

xmlns:xsi="http://www.w3.org/2001/XMLSchema-instance"

xsi:schemaLocation="

http://mina.apache.o

- 优化MySQL数据库性能的八种方法

AILIKES

sqlmysql

1、选取最适用的字段属性 MySQL可以很好的支持大数据量的存取,但是一般说来,数据库中的表越小,在它上面执行的查询也就会越快。因此,在创建表的时候,为了获得更好的 性能,我们可以将表中字段的宽度设得尽可能小。例如,在定义邮政编码这个字段时,如果将其设置为CHAR(255),显然给数据库增加了不必要的空间,甚至使用VARCHAR这种类型也是多余的,因为CHAR(6)就可以很

- JeeSite 企业信息化快速开发平台

Kai_Ge

JeeSite

JeeSite 企业信息化快速开发平台

平台简介

JeeSite是基于多个优秀的开源项目,高度整合封装而成的高效,高性能,强安全性的开源Java EE快速开发平台。

JeeSite本身是以Spring Framework为核心容器,Spring MVC为模型视图控制器,MyBatis为数据访问层, Apache Shiro为权限授权层,Ehcahe对常用数据进行缓存,Activit为工作流

- 通过Spring Mail Api发送邮件

120153216

邮件main

原文地址:http://www.open-open.com/lib/view/open1346857871615.html

使用Java Mail API来发送邮件也很容易实现,但是最近公司一个同事封装的邮件API实在让我无法接受,于是便打算改用Spring Mail API来发送邮件,顺便记录下这篇文章。 【Spring Mail API】

Spring Mail API都在org.spri

- Pysvn 程序员使用指南

2002wmj

SVN

源文件:http://ju.outofmemory.cn/entry/35762

这是一篇关于pysvn模块的指南.

完整和详细的API请参考 http://pysvn.tigris.org/docs/pysvn_prog_ref.html.

pysvn是操作Subversion版本控制的Python接口模块. 这个API接口可以管理一个工作副本, 查询档案库, 和同步两个.

该

- 在SQLSERVER中查找被阻塞和正在被阻塞的SQL

357029540

SQL Server

SELECT R.session_id AS BlockedSessionID ,

S.session_id AS BlockingSessionID ,

Q1.text AS Block

- Intent 常用的用法备忘

7454103

.netandroidGoogleBlogF#

Intent

应该算是Android中特有的东西。你可以在Intent中指定程序 要执行的动作(比如:view,edit,dial),以及程序执行到该动作时所需要的资料 。都指定好后,只要调用startActivity(),Android系统 会自动寻找最符合你指定要求的应用 程序,并执行该程序。

下面列出几种Intent 的用法

显示网页:

- Spring定时器时间配置

adminjun

spring时间配置定时器

红圈中的值由6个数字组成,中间用空格分隔。第一个数字表示定时任务执行时间的秒,第二个数字表示分钟,第三个数字表示小时,后面三个数字表示日,月,年,< xmlnamespace prefix ="o" ns ="urn:schemas-microsoft-com:office:office" />

测试的时候,由于是每天定时执行,所以后面三个数

- POJ 2421 Constructing Roads 最小生成树

aijuans

最小生成树

来源:http://poj.org/problem?id=2421

题意:还是给你n个点,然后求最小生成树。特殊之处在于有一些点之间已经连上了边。

思路:对于已经有边的点,特殊标记一下,加边的时候把这些边的权值赋值为0即可。这样就可以既保证这些边一定存在,又保证了所求的结果正确。

代码:

#include <iostream>

#include <cstdio>

- 重构笔记——提取方法(Extract Method)

ayaoxinchao

java重构提炼函数局部变量提取方法

提取方法(Extract Method)是最常用的重构手法之一。当看到一个方法过长或者方法很难让人理解其意图的时候,这时候就可以用提取方法这种重构手法。

下面是我学习这个重构手法的笔记:

提取方法看起来好像仅仅是将被提取方法中的一段代码,放到目标方法中。其实,当方法足够复杂的时候,提取方法也会变得复杂。当然,如果提取方法这种重构手法无法进行时,就可能需要选择其他

- 为UILabel添加点击事件

bewithme

UILabel

默认情况下UILabel是不支持点击事件的,网上查了查居然没有一个是完整的答案,现在我提供一个完整的代码。

UILabel *l = [[UILabel alloc] initWithFrame:CGRectMake(60, 0, listV.frame.size.width - 60, listV.frame.size.height)]

- NoSQL数据库之Redis数据库管理(PHP-REDIS实例)

bijian1013

redis数据库NoSQL

一.redis.php

<?php

//实例化

$redis = new Redis();

//连接服务器

$redis->connect("localhost");

//授权

$redis->auth("lamplijie");

//相关操

- SecureCRT使用备注

bingyingao

secureCRT每页行数

SecureCRT日志和卷屏行数设置

一、使用securecrt时,设置自动日志记录功能。

1、在C:\Program Files\SecureCRT\下新建一个文件夹(也就是你的CRT可执行文件的路径),命名为Logs;

2、点击Options -> Global Options -> Default Session -> Edite Default Sett

- 【Scala九】Scala核心三:泛型

bit1129

scala

泛型类

package spark.examples.scala.generics

class GenericClass[K, V](val k: K, val v: V) {

def print() {

println(k + "," + v)

}

}

object GenericClass {

def main(args: Arr

- 素数与音乐

bookjovi

素数数学haskell

由于一直在看haskell,不可避免的接触到了很多数学知识,其中数论最多,如素数,斐波那契数列等,很多在学生时代无法理解的数学现在似乎也能领悟到那么一点。

闲暇之余,从图书馆找了<<The music of primes>>和<<世界数学通史>>读了几遍。其中素数的音乐这本书与软件界熟知的&l

- Java-Collections Framework学习与总结-IdentityHashMap

BrokenDreams

Collections

这篇总结一下java.util.IdentityHashMap。从类名上可以猜到,这个类本质应该还是一个散列表,只是前面有Identity修饰,是一种特殊的HashMap。

简单的说,IdentityHashMap和HashM

- 读《研磨设计模式》-代码笔记-享元模式-Flyweight

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

import java.util.ArrayList;

import java.util.Collection;

import java.util.HashMap;

import java.util.List;

import java

- PS人像润饰&调色教程集锦

cherishLC

PS

1、仿制图章沿轮廓润饰——柔化图像,凸显轮廓

http://www.howzhi.com/course/retouching/

新建一个透明图层,使用仿制图章不断Alt+鼠标左键选点,设置透明度为21%,大小为修饰区域的1/3左右(比如胳膊宽度的1/3),再沿纹理方向(比如胳膊方向)进行修饰。

所有修饰完成后,对该润饰图层添加噪声,噪声大小应该和

- 更新多个字段的UPDATE语句

crabdave

update

更新多个字段的UPDATE语句

update tableA a

set (a.v1, a.v2, a.v3, a.v4) = --使用括号确定更新的字段范围

- hive实例讲解实现in和not in子句

daizj

hivenot inin

本文转自:http://www.cnblogs.com/ggjucheng/archive/2013/01/03/2842855.html

当前hive不支持 in或not in 中包含查询子句的语法,所以只能通过left join实现。

假设有一个登陆表login(当天登陆记录,只有一个uid),和一个用户注册表regusers(当天注册用户,字段只有一个uid),这两个表都包含

- 一道24点的10+种非人类解法(2,3,10,10)

dsjt

算法

这是人类算24点的方法?!!!

事件缘由:今天晚上突然看到一条24点状态,当时惊为天人,这NM叫人啊?以下是那条状态

朱明西 : 24点,算2 3 10 10,我LX炮狗等面对四张牌痛不欲生,结果跑跑同学扫了一眼说,算出来了,2的10次方减10的3次方。。我草这是人类的算24点啊。。

然后么。。。我就在深夜很得瑟的问室友求室友算

刚出完题,文哥的暴走之旅开始了

5秒后

- 关于YII的菜单插件 CMenu和面包末breadcrumbs路径管理插件的一些使用问题

dcj3sjt126com

yiiframework

在使用 YIi的路径管理工具时,发现了一个问题。 <?php

- 对象与关系之间的矛盾:“阻抗失配”效应[转]

come_for_dream

对象

概述

“阻抗失配”这一词组通常用来描述面向对象应用向传统的关系数据库(RDBMS)存放数据时所遇到的数据表述不一致问题。C++程序员已经被这个问题困扰了好多年,而现在的Java程序员和其它面向对象开发人员也对这个问题深感头痛。

“阻抗失配”产生的原因是因为对象模型与关系模型之间缺乏固有的亲合力。“阻抗失配”所带来的问题包括:类的层次关系必须绑定为关系模式(将对象

- 学习编程那点事

gcq511120594

编程互联网

一年前的夏天,我还在纠结要不要改行,要不要去学php?能学到真本事吗?改行能成功吗?太多的问题,我终于不顾一切,下定决心,辞去了工作,来到传说中的帝都。老师给的乘车方式还算有效,很顺利的就到了学校,赶巧了,正好学校搬到了新校区。先安顿了下来,过了个轻松的周末,第一次到帝都,逛逛吧!

接下来的周一,是我噩梦的开始,学习内容对我这个零基础的人来说,除了勉强完成老师布置的作业外,我已经没有时间和精力去

- Reverse Linked List II

hcx2013

list

Reverse a linked list from position m to n. Do it in-place and in one-pass.

For example:Given 1->2->3->4->5->NULL, m = 2 and n = 4,

return

- Spring4.1新特性——页面自动化测试框架Spring MVC Test HtmlUnit简介

jinnianshilongnian

spring 4.1

目录

Spring4.1新特性——综述

Spring4.1新特性——Spring核心部分及其他

Spring4.1新特性——Spring缓存框架增强

Spring4.1新特性——异步调用和事件机制的异常处理

Spring4.1新特性——数据库集成测试脚本初始化

Spring4.1新特性——Spring MVC增强

Spring4.1新特性——页面自动化测试框架Spring MVC T

- Hadoop集群工具distcp

liyonghui160com

1. 环境描述

两个集群:rock 和 stone

rock无kerberos权限认证,stone有要求认证。

1. 从rock复制到stone,采用hdfs

Hadoop distcp -i hdfs://rock-nn:8020/user/cxz/input hdfs://stone-nn:8020/user/cxz/运行在rock端,即源端问题:报版本

- 一个备份MySQL数据库的简单Shell脚本

pda158

mysql脚本

主脚本(用于备份mysql数据库): 该Shell脚本可以自动备份

数据库。只要复制粘贴本脚本到文本编辑器中,输入数据库用户名、密码以及数据库名即可。我备份数据库使用的是mysqlump 命令。后面会对每行脚本命令进行说明。

1. 分别建立目录“backup”和“oldbackup” #mkdir /backup #mkdir /oldbackup

- 300个涵盖IT各方面的免费资源(中)——设计与编码篇

shoothao

IT资源图标库图片库色彩板字体

A. 免费的设计资源

Freebbble:来自于Dribbble的免费的高质量作品。

Dribbble:Dribbble上“免费”的搜索结果——这是巨大的宝藏。

Graphic Burger:每个像素点都做得很细的绝佳的设计资源。

Pixel Buddha:免费和优质资源的专业社区。

Premium Pixels:为那些有创意的人提供免费的素材。

- thrift总结 - 跨语言服务开发

uule

thrift

官网

官网JAVA例子

thrift入门介绍

IBM-Apache Thrift - 可伸缩的跨语言服务开发框架

Thrift入门及Java实例演示

thrift的使用介绍

RPC

POM:

<dependency>

<groupId>org.apache.thrift</groupId>