使用Quartus II进行FPGA实验之Switches, Lights, and Multiplexers

使用Quartus设计FPGA,简单包括以下流程:

- 新建工程,写代码

- 编译工程,找错误

- 分配引脚,重编译

- 下载配置,到硬件

为保证设计的正确性,在编译后,一般还需要做仿真验证,然后下载至硬件,有两种仿真方式:

- 功能仿真

- 时序仿真https://blog.csdn.net/alexanderrr/article/details/51615254

Quartus II软件可以使用原理图形式和RTL级代码来设计FPGA,使用原理图可以直接调用FPGA上的资源,省去了一些模块的编写。一般采用写Verilog代码的形式来设计FPGA。

简单列出Quartus II操作步骤:

新建工程 ![]() 选择FPGA开发板Cyclone IV EP4CE115F29C7

选择FPGA开发板Cyclone IV EP4CE115F29C7 ![]() finish

finish ![]() 新建一个Verilog文件(保持这个文件名和顶层模块名相同)

新建一个Verilog文件(保持这个文件名和顶层模块名相同)![]() 写好代码点绿色三角编译

写好代码点绿色三角编译 ![]() 在files标签页将此文件设置为顶层文件

在files标签页将此文件设置为顶层文件 ![]() debug编译成功

debug编译成功

至此就可以分配引脚后重编译烧到板子里了。

几个简单的练习:

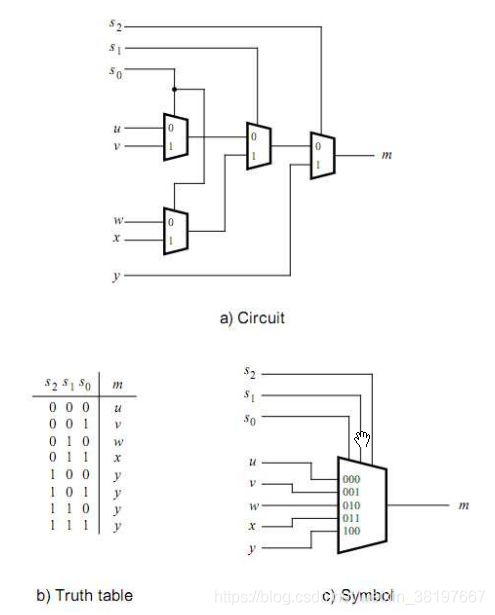

五选一选择器

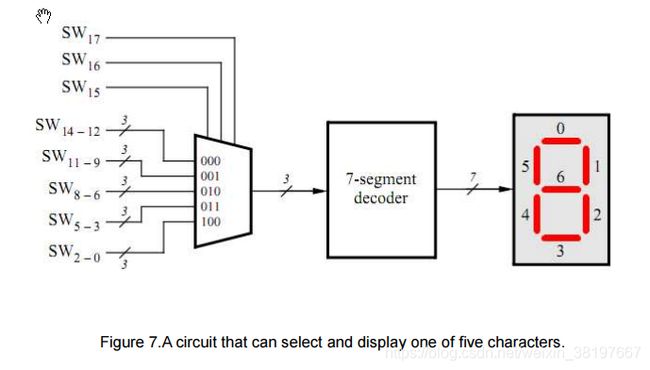

X选一的选择器是比较简单的电路,可以通过直接观察真值表使用case语句来描述电路,要求如下:

module part3(

input [17:0]SW,// S2 S1 S0 U V W X Y

output [17:0] LEDR,// indicte sw state

output reg[2:0]LEDG// M

);

assign LEDR = SW;

always@(*)

casez(SW[17:15])

3'b000: LEDG[2:0] = SW[14:12];

3'b001: LEDG[2:0] = SW[11:9];

3'b010: LEDG[2:0] = SW[8:6];

3'b011: LEDG[2:0] = SW[5:3];

3'b1??: LEDG[2:0] = SW[2:0];

endcase

endmodule数码管控制电路

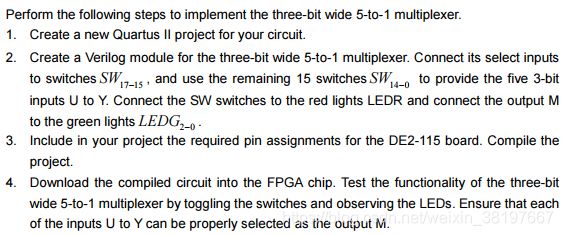

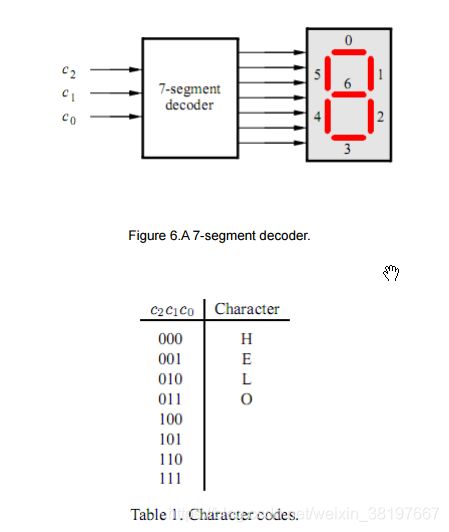

数码管的控制也可用case语句把真值表描述下来,输出直接连接到数码管即可:

module part4(

input [2:0]SW,//c2 c1 c0

output reg[0:6]HEX0_D

);

always@(*) begin

HEX0_D = 'b1;// not work

case(SW[2:0])

3'b000: HEX0_D = 7'b1001000;//H

3'b001: HEX0_D = 7'b0110000;//E

3'b010: HEX0_D = 6'b1110001;//L

3'b011: HEX0_D = 6'b0000001;//O?

endcase

end

endmodule

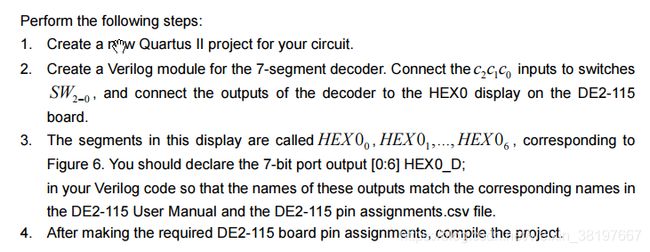

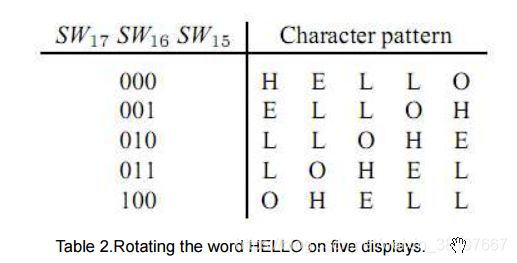

同时控制5个数码管

题目要求用了非常多的端口去控制5个数码管来显示英文单词HELLO,但是从真值表可以看到直接用case语句就可以实现:

module part5 (

input [17:15] SW, // toggle switches

output reg[0:6] HEX0_D,HEX1_D,HEX2_D,HEX3_D,HEX4_D //5 7-seg displays

);

parameter H = 7'b1001000;

parameter E = 7'b0110000;

parameter L = 7'b1110001;

parameter O = 7'b0000001;

always@(*) begin

{HEX0_D,HEX1_D,HEX2_D,HEX3_D,HEX4_D} = 'b1;// not display,blank

case(SW[17:15])

3'b000: {HEX0_D,HEX1_D,HEX2_D,HEX3_D,HEX4_D} = {H,E,L,L,O};

3'b001: {HEX0_D,HEX1_D,HEX2_D,HEX3_D,HEX4_D} = {E,L,L,O,H};

3'b010: {HEX0_D,HEX1_D,HEX2_D,HEX3_D,HEX4_D} = {L,L,O,H,E};

3'b011: {HEX0_D,HEX1_D,HEX2_D,HEX3_D,HEX4_D} = {L,O,H,E,L};

3'b100: {HEX0_D,HEX1_D,HEX2_D,HEX3_D,HEX4_D} = {O,H,E,L,L};

endcase

end

endmodule做完了实验一值得注意的有以下几点:

- 实体名称未定义的报错是因为没有设置Verilog文件为顶层设计文件,参上。

- case语句适用于较为复杂的电路,简单电路直接用连续赋值语句条件语句即可完成选择。

- 使用case语句一定要设置默认值,避免锁存器的产生。可以case前赋值,也可以最后写default项。

下面贴几张开发板照片: