petalinux安装问题总结

1,安装所需要的库

apt install build-essential vim tofrodos

解决:1、 sudo rm /var/cache/apt/archives/lock

2、sudo rm /var/lib/dpkg/lock

3、sudo dpkg --configure -a

4、sudo apt-get update

执行其他的命令出现此问题同样的方式解决。如果apt install不行,请使用apt-get install

2、运行petalinux安装包

1、chmod 777 petalinux-v2018.3-final-installer.run

2、exit退出root模式,必须得普通的用户状态才行。

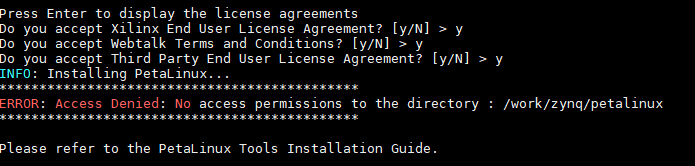

3、./petalinux-v2018.3-final-installer.run /work/zynq/petalinux

4、如果安装失败需要重新安装得删除 .log文件,就在安装包目录下。

5、出现无法访问的问题,直接mkdir建立的petalinux文件夹没有访问权限

解决方法1、创建petalinux的时候使用 mkdir -p petalinux

2、chmod 777 petalinux修改文件夹的权限

6、由于分区的问题,导致安装空间不足,于是使用以下命令查看分区,选择合适大小的目录

1、du -sh

2、sudo df -h

3、修改安装目录重新安装

7、出现如下警告![]()

解决:1、sudo apt-get install tftpd tftp openbsd-inetd

2、gedit /etc/inetd.conf

添加如下内容:

tftp dgram udp wait nobody /usr/sbin/tcpd /usr/sbin/in.tftpd /tftproot

保存并退出:

3、mkdir /tftproot

chmod 777 /tftproot

/etc/init.d/openbsd-inetd restart

netstat -an | more | grep udp

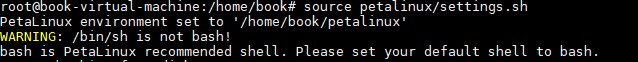

8、出现,因为UG1144手册中提到,所用的/bin/sh都是需要bash的,而Ubuntu默认的/bin/sh是dash,所以直接把原来的删除,链接/bin/sh到bash //参考文章:https://www.cnblogs.com/vacajk/p/6146146.html

解决方法1、cp /bin/sh /bin/sh1

2、rm /bin/sh

3、ln -s /bin/bash /bin/sh

4、ls -al /bin/sh

自此:所有的petalinux安装问题已解决

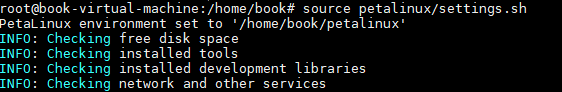

输入:source petalinux/settings.sh

注:中间会出现license argreement按提示操作就行

完成安装:总的用时20分钟左右