AI芯片发展的前世今生

来源:数学与人工智能,以上文章观点仅代表文章作者,仅供参考,以抛砖引玉!

人工智能芯片的分类

2.1 传统CPU困局

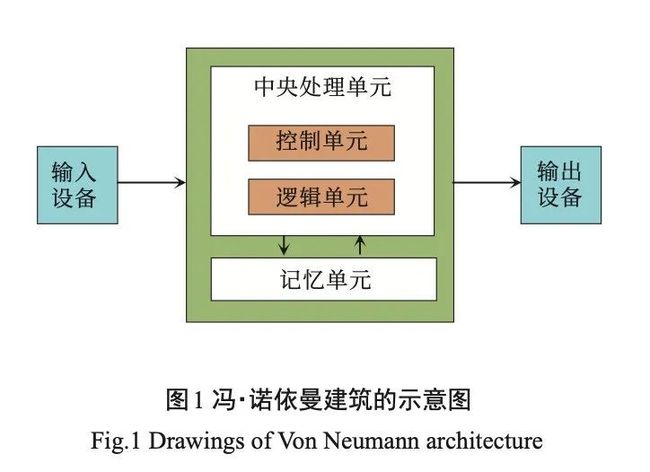

自20个世纪60年代早期开始,CPU(中央处理器)开始出现并使用在计算机工业中。现如今,虽然CPU 在设计和实现上都发生了巨大变化 ,但是基于 冯 · 诺依曼架构的 CPU 基本工作原理却一直没有发 生很大变化。如图 1 所示 ,冯 · 诺依曼架构分为中央 处理单元(CPU)和存储器,CPU主要由控制器和运 算器两大部件组成[15]。在工作时 ,CPU 每执行一条指令都需要从存储器中读取数据 ,根据指令对数据 进行相应的操作,因此CPU不仅负责数据运算,而且 需要执行存储读取 、指令分析 、分支跳转等命令。同 时可以通过提升单位时间内执行指令的条数 ,即主 频 ,来提升计算速度。但在人工智能深度学习领域 中程序指令相对较少 ,但对大数据的计算需求很大 , 需要进行海量的数据处理。当用 CPU 执行 AI 算法 时 ,CPU 将花费大量的时间在数据/指令的读取分析 上 ,在一定的功耗前提下 ,不能够通过无限制的加快CPU 频率和内存带宽来达到指令执行速度无限制的 提升。因此在这种情形下 ,传统 CPU 结构缺点明显 , 在人工智能芯片领域中的算力瓶颈问题很难解决 。

2.2 人工智能芯片中的后CPU时代

基于 CPU 的算力问题 ,近年来人工智能芯片领域的科学家们进行了富有成果的广泛研究 ,主要集 中在 AI 芯片目前的两种发展方向。一个方向是继 续延续经典的冯 · 诺依曼计算架构 ,以加速计算能力 为发展目标,主要分为并行加速计算的GPU(图形处 理单元)、半定制化的 FPGA(现场可编程门阵列)、全 定制化的 ASIC(专用集成电路)。另一个方向就是 颠覆传统的冯 · 诺依曼计算架构 ,采用基于类脑神经 结构的神经拟态芯片来解决算力问题。下面将对这 两个方向的人工智能芯片特点进行详细描述。

2.2.1 按架构分类

(1)图 形 处 理 单 元(graphics processing unit ,GPU)。GPU 是相对较早的加速计算处理器 ,具 有速度快、芯片编程灵活简单等特点。由于传统CPU 的计算指令遵循串行执行方式 ,不能发挥出芯片的全部潜力 ,而 GPU 具有高并行结构 ,在处理图形 数据和复杂算法方面拥有比 CPU 更高的效率。在结 构上 ,CPU 主要由控制器和寄存器组成 ,而 GPU 则拥 有更多的逻辑运算单元(arithmetic logic unit,ALU) 用于数据处理,这样的结构更适合对密集型数据进 行并行处理 ,程序在 GPU 系统上的运行速度相较于 单核 CPU 往往提升几十倍乃至上千倍。同时 ,GPU拥有了更加强大的浮点运算能力 ,可以缓解深度学 习算法的训练难题,释放人工智能的潜能。但是GPU 也有一定的局限性。深度学习算法分为训练和 推断两部分 ,GPU 平台在算法训练上非常高效。但 在推断中对于单项输入进行处理的时候 ,并行计算 的优势不能完全发挥出来 。

(2)现场可编程门阵列(field programmable gate array ,FPGA )。FPGA 是 在 PAL 、GAL 、CPLD 等 可 编 程器件基础上进一步发展的产物。其基本原理是在FPGA 芯片内集成大量的基本门电路以及存储器 ,用 户可以通过更新FPGA配置文件(即烧入)来定义这 些门电路以及存储器之间的连线。这种烧入不是一 次性的,因此,它既解决了定制电路灵活性的不足, 又克服了原有可编程器件门电路数有限的缺点。与GPU 不同 ,FPGA 同时拥有进行数据并行和任务并行 计算的能力 ,适用于以硬件流水线方式处理一条数 据 ,且整数运算性能更高 ,因此常用于深度学习算法 中的推断阶段。不过 FPGA 通过硬件的配置实现软 件算法 ,因此在实现复杂算法方面有一定的难度 。

将FPGA和CPU对比可以发现两个特点,一是FPGA没有内存和控制所带来的存储和读取部分,速度更快,二是FPGA没有读取指令操作,所以功耗更低。劣势是价格比较高,编程复杂,整体运算能力不是很高。功耗方面 ,从体系结构而言 ,FPGA 也具有天生 的优势。传统的冯氏结构中,执行单元(如CPU核) 执行任意指令,都需要有指令存储器 、译码器 、各种 指令的运算器及分支跳转处理逻辑参与运行,而FPGA每个逻辑单元的功能在重编程(即烧入)时就已经确定 ,不需要指令,无需共享内存 ,从而可以极 大地降低单位执行的功耗 ,提高整体的能耗比。FPGA最值得注意的例子可能是 CNP [16] ,它进一步改 进并重命名为 NeuFlow [17] ,后来改编为 nn-X [18]。这些设计可以实现 10~100 KM/s 操作(GOPS),功率仅 为10W以下。

(3)专用集成电路(application-specific integrated circuit,ASIC)。目前以深度学习为代表的人工智能 计算需求,主要采用GPU、FPGA等已有的适合并行 计算的通用芯片来实现加速。在产业应用没有大规 模兴起之时 ,使用这类 GPU 、FPGA 已有的通用芯片 可以避免专门研发定制芯片( ASIC )的高投入和高风 险。但是,由于这类通用芯片设计初衷并非专门针 对深度学习 ,因而天然存在性能 、功耗等方面的局限 性。随着人工智能应用规模的扩大 ,这类问题日益 突显。

GPU 作为图像处理器 ,设计初衷是为了应对图像 处理中的大规模并行计算。因此 ,在应用于深度学习 算法时无法充分发挥并行计算优势。深度学习包含 训练和推断两个计算环节 ,GPU 在深度学习算法训练 上非常高效 ,但对于单一输入进行推断的场合 ,并行 度的优势不能完全发挥。其次,GPU采用SIMT计算 模式 ,硬件结构相对固定 ,无法灵活配置硬件结构 。此外,运行深度学习算法能效低于FPGA。

虽然 FPGA 倍受看好 ,但其毕竟不是专门为了适 用深度学习算法而研发 ,实际应用中为了实现可重 构特性 ,FPGA 内部有大量极细粒度的基本单元 ,但 是每个单元的计算能力都远低于 CPU 和 GPU 中的ALU 模块;其次 ,为实现可重构特性 ,FPGA 内部大 量资源被用于可配置的片上路由与连线 ,因此计算 资源占比相对较低;再者,速度和功耗相对专用定制 芯片(ASIC)仍然存在不小差距;而且FPGA价格较 为昂贵,在规模放量的情况下单块FPGA的成本要远 高于专用定制芯片。

因此 ,随着人工智能算法和应用技术的日益发 展,以及人工智能专用芯片ASIC产业环境的逐渐成 熟 ,全定制化人工智能 ASIC 也逐步体现出自身的优 势。ASIC是专用定制芯片,定制的特性有助于提高ASIC 的性能功耗比 ,缺点是电路设计需要定制 ,相 对开发周期长 ,功能难以扩展。但在功耗 、可靠性 、 集成度等方面都有优势 ,尤其在要求高性能 、低功耗 的移动应用端体现明显。比如谷歌的 TPU、寒武纪 的 GPU ,地平线的 BPU 都属于 ASIC 芯片 。

(4)神经拟态芯片(类脑芯片)。在人工智能芯片中,传统的冯·诺依曼架构存在着“冯·诺依曼瓶 颈”,它降低了系统的整体效率和性能[19]。为了从 根本上克服这个问题 ,神经形态计算近年来已成为 基于冯 · 诺依曼系统的这些传统计算架构的最有吸 引力的替代方案。术语“神经形态计算”首先由Mead[20] 在 1990 年提出 ,它是一种受大脑认知功能 启发的新计算范式。与传统的 CPU / GPU 不同 ,生 物脑(例如哺乳动物的大脑)能够以高效率和低功 耗在小区域中并行处理大量信息。因此 ,神经形态 计算的最终目标是开发神经形态硬件加速器 ,模拟 高效生物信息处理,以弥合网络和真实大脑之间的 效率差距[21] ,这被认为是下一代人工智能的主要驱 动力。

神经拟态芯片不采用经典的冯 · 诺依曼架构 ,而 是基于神经形态架构设计 ,是模拟生物神经网络的 计算机制 ,如果将神经元和突触权重视为大脑的“处 理器”和“记忆”,它们会分布在整个神经皮层[22]。神 经拟态计算从结构层面去逼近大脑 ,其研究工作可 分为两个层次 ,一是神经网络层面,与之相应的是神 经拟态架构和处理器 ,以 IBM Truenorth 为代表 ,这 种芯片把定制化的数字处理内核当作神经元 ,把内存作为突触。

其逻辑结构与传统冯·诺依曼结构不同:内存、CPU和通信部件完全集成在一起,因此信 息的处理在本地进行 ,克服了传统计算机内存与CPU 之间的速度瓶颈问题。同时神经元之间可以方 便快捷地相互沟通 ,只要接收到其他神经元发过来 的脉冲(动作电位),这些神经元就会同时做动作;二 是神经元与神经突触层面 ,与之相应的是元器件层 面的创新。如 IBM 苏黎世研究中心宣布制造出世界 上首个人造纳米尺度的随机相变神经元,可实现高 速无监督学习 。

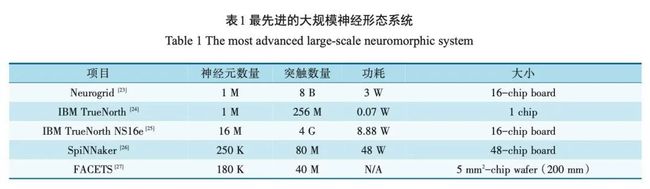

当前 ,最先进的神经拟态芯片仍然远离人类大 脑的规模(1010个神经元,每个神经元有103~104个突 触),至多达到104 倍,如表1所示。为了达到在人脑 中规模,应将多个神经拟态芯片集成在电路板或背 板上 ,以构成超大规模计算系统。神经拟态芯片的 设计目的不再仅仅局限于加速深度学习算法 ,而是 在芯片基本结构甚至器件层面上改变设计 ,希望能 够开发出新的类脑计算机体系结构,比如采用忆阻 器和 ReRAM 等新器件来提高存储密度。这类芯片 技术尚未完全成熟 ,离大规模应用还有很长的距离 , 但是长期来看类脑芯片有可能会带来计算机体系结构的革命 。

2.2.2 按功能分类

根据机器学习算法步骤 ,可分为训练(training)和推断( inference )两个环节 。训练环节通常需要通过大量的数据输入,训练出一个复杂的深度神经网络模型。训练过程由于涉 及海量的训练数据和复杂的深度神经网络结构 ,运 算量巨大 ,需要庞大的计算规模 ,对于处理器的计算 能力 、精度 、可扩展性等性能要求很高。目前市场上通常使用英伟达的 GPU 集群来完成 ,Google 的TPU2.0/3.0 也支持训练环节的深度网络加速 。

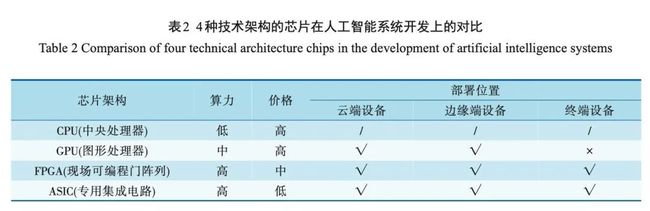

推断环节是指利用训练好的模型 ,使用新的数 据去“推断”出各种结论。这个环节的计算量相对训 练环节少很多 ,但仍然会涉及到大量的矩阵运算 。在推断环节中 ,除了使用 CPU 或 GPU 进行运算外 ,FPGA 以及 ASIC 均能发挥重大作用。表 2 是 4 种技 术架构的芯片在人工智能系统开发上的对比 。

2.2.3 按应用场景分类

主要分为用于服务器端(云端)和用于移动端( 终 端 )两 大 类 。

服务器端:在深度学习的训练阶段 ,由于数据量及运算量巨大 ,单一处理器几乎不可能独立完成 1 个 模型的训练过程 ,因此 ,负责 AI 算法的芯片采用的是 高性能计算的技术路线 ,一方面要支持尽可能多的网 络结构以保证算法的正确率和泛化能力;另一方面必 须支持浮点数运算;而且为了能够提升性能必须支持 阵列式结构(即可以把多块芯片组成一个计算阵列以 加速运算)。在推断阶段,由于训练出来的深度神经 网络模型仍非常复杂 ,推断过程仍然属于计算密集型 和存储密集型 ,可以选择部署在服务器端 。

移 动 端( 手 机 、智 能 家 居 、无 人 车 等 ):移 动 端 AI芯片在设计思路上与服务器端 AI 芯片有着本质的 区别。首先,必须保证很高的计算能效;其次,在高 级辅助驾驶 ADAS 等设备对实时性要求很高的场 合 ,推断过程必须在设备本身完成 ,因此要求移动端 设备具备足够的推断能力。而某些场合还会有低功 耗 、低延迟 、低成本的要求 ,从而导致移动端的 AI 芯 片多种多样 。

未来智能实验室的主要工作包括:建立AI智能系统智商评测体系,开展世界人工智能智商评测;开展互联网(城市)云脑研究计划,构建互联网(城市)云脑技术和企业图谱,为提升企业,行业与城市的智能水平服务。

如果您对实验室的研究感兴趣,欢迎加入未来智能实验室线上平台。扫描以下二维码或点击本文左下角“阅读原文”

![]()