- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- PyTorch & TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)

阿牛的药铺

算法移植部署pytorchtensorflowfpga开发

PyTorch&TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)引言:为什么算法移植工程师必须掌握框架基础?针对光学类产品算法FPGA移植岗位需求(如可见光/红外图像处理),深度学习框架是算法落地的"桥梁"——既要用PyTorch/TensorFlow验证算法可行性,又要将训练好的模型(如CNN、目标检测)转换为FPGA可部署的格式(ONNX、TFLite)。本文采用"

- FPGA 设计中的 “Create HDL Wrapper“ 和 “Generating Output Products“ 的区别

行者..................

fpga开发

CreateHDLWrapper(创建HDL包装器)目的:为顶层设计模块(通常是BlockDesign/IPIntegrator设计)创建一个HDL包装文件功能:将图形化/框图设计的BlockDesign转换为可综合的HDL代码(Verilog或VHDL)创建一个顶层模块,将所有IP核和连接实例化使用场景:当使用IPIntegrator创建BlockDesign后需要将图形化设计转换为HDL代码以

- STM32与FPGA用FMC进行通讯

weixin_43554366

单片机stm32fpga物联网人工智能

stm32正常按读写SDRAM进行配置,FPGA进行信号采集。FPGA信号采集发现SDWNE是高但H7手册上时序显示是低,造成无法像FPGA模拟的SDRAM无法写入数据FPGA采集信号应该在时钟下降沿,上升沿采集,数据会发生错误。

- Xilinx Vivado开发环境快速导出hdf文件(bat批处理)

XilinxFPGA使用Vivado开发环境创建MicroBlaze软核或ZYNQPS侧SDK逻辑工程时,需要FPGA侧搭建的硬件平台文件,即hdf文件,常规方式是编译完成生成bit流文件后,通过File->Export->ExportHardware菜单来导出,在弹出的菜单再选择要导出的路径和文件名称等,这个过程比较繁琐,通过观察TCL终端窗口:update_compile_order-file

- Xilinx系FPGA学习笔记(三)Vivado的仿真及ILA使用

贾saisai

FPGA学习fpga开发学习笔记

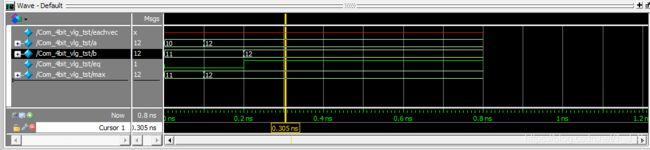

系列文章目录文章目录系列文章目录前言仿真验证(类似modelsim)ILA在线调试工具添加ILAILA的例化ILA的使用前言接着学习vivado的使用方法仿真验证(类似modelsim)首先类似添加.v文件的方法,在File-AddSource中选择Addorcreatesimulationsources或者直接在Sources里面选就行然后就编写testbench,类似之前介绍的modelsim

- FPGA 47 ,MIG 内存接口生成器深度解析( FPGA 中的 MIG 技术 )

北城笑笑

fpga开发fpga

目录前言一、基础理论1.1MIG介绍1.2结构框架1.2.1主要模块①用户接口层(UserInterfaceLayer)②控制逻辑层(ControLogicLayer)③校准逻辑(CalibrationLogic)④初始化与时序控制(Initialization&TimingControl)⑤物理层接口(PHY–PhysicalLayer)⑥IO引脚驱动(引脚分配与IO配置:Pinout&IOSt

- 基于FPGA的数字密码锁

阿智605

fpga开发notepad++

基于FPGA的数字密码锁顶层文件modulelock(inputclk,//时钟inputrst_n,//复位input[3:0]number_in,//输入inputkey_open1,inputkey_lock1,//inputkey_reset1,outputbeep,//蜂鸣器outputlock_flag,//锁标志位output[3:0]dtube_cs_n,//7段数码管位选信号ou

- 基于FPGA的设计:简易电子密码锁嵌入式实现

程序员杨弋

嵌入式开发fpga开发嵌入式

简介:本文介绍了如何使用FPGA(现场可编程逻辑门阵列)来设计和实现一款简易的电子密码锁。电子密码锁是一种常见的安全访问控制系统,通过输入正确的密码来解锁。嵌入式系统采用FPGA作为核心处理器,结合适当的外设和编程逻辑,能够实现密码输入、验证和控制功能。本文将详细介绍电子密码锁的设计和源代码。设计原理:输入设备:本设计采用数字键盘作为密码输入设备。数字键盘通过FPGA的GPIO(通用输入输出)引脚

- 多通路fpga 通信_FMC与FPGA双口ram通讯

weixin_39796752

多通路fpga通信

硬件环境:ARM+FPGA通过FMC互联,STM32F767和EP4CE15F23I7FMC设置,STM的系统时钟HCLK为216MHz1/*FMCinitializationfunction*/2voidMX_FMC_Init(void)3{4FMC_NORSRAM_TimingTypeDefTiming;56/**PerformtheNOR1memoryinitializationsequen

- [硬件接口]HDMI和DP 区别

DisplayPort和HDMI在FPGA应用场景的实现使用与区别概述DisplayPort(DP)和HDMI是两种主流的数字音视频接口,广泛应用于视频传输场景。在FPGA(现场可编程门阵列)应用中,DP和HDMI常用于视频处理、显示驱动和高带宽数据传输。本文档比较两者在FPGA实现中的使用方式、应用场景及主要区别,并以Markdown格式呈现。1.FPGA实现概述1.1DisplayPort在F

- [FPGA工具]FPGA 文件格式转换工具

S&Z3463

FPGA开发工具fpga开发

SZFPGA文件格式转换工具概述SZFPGA文件格式转换工具(版本V1.0.0)是一款专为FPGA文件格式转换设计的工具,旨在帮助用户将基于Vivado的FPGA文档格式转换为适用于XilinxVivado工具链的格式。本工具支持多种FPGA文档格式的转换,包括BIT转BIN、BIT转MCS、MCS转BIN以及SPIFlash加载等功能。本文档将详细介绍工具的主要功能、使用需求、转换要求、SPI使

- [FPGA AXI IP] AXI Crossbar

AXICrossbarIP详细介绍概述AXICrossbar是属于AXIInterconnectIPSuite的一部分,专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过交叉开关(Crossbar)架构实现高效的数据路由,支持多主多从的点对点连接,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联

- [AXI] AXI Interconnect

AXIInterconnectIP详细介绍概述AXIInterconnect专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过模块化架构实现高效的数据路由、协议转换、数据宽度转换和时钟域转换,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联的场景,如多核处理器系统、视频处理、网络通信和硬件加速器

- [FPGA Video IP] Video Processing Subsystem

S&Z3463

FPGAVideoIPfpga开发tcp/ip网络协议Video

XilinxVideoProcessingSubsystemIP(PG231)详细介绍概述XilinxLogiCORE™IPVideoProcessingSubsystem(VPSS)(PG231)是一个高度可配置的视频处理模块,设计用于在单一IP核中集成多种视频处理功能,包括缩放(Scaling)、去隔行(Deinterlacing)、颜色空间转换(ColorSpaceConversion,CS

- 基于FPGA的二维FFT实现

廉连曼

基于FPGA的二维FFT实现【下载地址】基于FPGA的二维FFT实现本项目提供了一种基于FPGA的高效二维FFT实现方案,专为数字信号处理和图像处理领域设计。通过并行使用两个一维FFT单元,本方案显著提升了二维FFT变换的计算效率,并基于Xilinx的FFTIP核,确保易于集成到其他FPGA设计中。该方案适用于各类频谱分析场景,尤其适合图像处理系统。经过Verilog编程和Modelsim仿真测试

- FPGA电子系统设计项目实战VHDL语言第2版王振红:深入掌握FPGA设计

姜奇惟Sparkling

FPGA电子系统设计项目实战VHDL语言第2版王振红:深入掌握FPGA设计【下载地址】FPGA电子系统设计项目实战VHDL语言第2版王振红这是一本专注于FPGA电子系统设计的实战指南,适合初学者和进阶开发者。全书共11章,从FPGA设计基础到VHDL语言应用,再到综合电子系统设计实例,内容全面且实用。通过深入浅出的讲解,读者不仅能掌握FPGA设计方法,还能具备实际应用能力。书中详细介绍了Quart

- 基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码

基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码【下载地址】基于FPGA的Verilog电子密码锁设计资源文件基于FPGA和Verilog语言设计的电子密码锁项目,提供完整的硬件设计原理图、Verilog代码、仿真波形图和硬件描述文档。通过FPGA的可编程特性,实现密码设置、验证及锁定功能,适合学术研究、教学演示或个人兴趣学习。项目文件清晰,包含详细的使用说明,帮助用户快速

- 【FFT】基于FPGA的FFT傅里叶变换和相位计算系统设计

fpga和matlab

★FPGA项目经验板块19:信号发生器fpga开发FFT相位计算

1.软件版本ISE14.7,modeslimSE,10.1c2.系统仿真与分析第1步:信号源的产生主要通过rom将产生的数据保存到rom中,然后,我们再仿真的时候调用即可。这个部分仿真效果如下所示,你给的程序中,这个部分主要有两个数据源,一个是1025,一个是N为1024,我们这里分别将这两个数据量化之后保存到rom中,仿真如下所示:

- 基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用

风吹麦很

fpga开发嵌入式

基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用快速傅里叶变换(FastFourierTransform,FFT)是一种重要的信号处理算法,在许多领域中都得到广泛的应用,例如通信系统、雷达技术、图像处理等。为了提高FFT的计算性能和实时性,将其设计为硬件加速器常常是一个明智的选择。本文将介绍基于现场可编程门阵列(Field-ProgrammableGateArray,FPGA)的FF

- FPGA电子系统设计项目实战 VHDL语言 第2版 王振红

幸刚磊Thomas

FPGA电子系统设计项目实战VHDL语言第2版王振红【下载地址】FPGA电子系统设计项目实战VHDL语言第2版王振红这是一本专注于FPGA电子系统设计的实战指南,适合初学者和进阶开发者。全书共11章,从FPGA设计基础到VHDL语言应用,再到综合电子系统设计实例,内容全面且实用。通过深入浅出的讲解,读者不仅能掌握FPGA设计方法,还能具备实际应用能力。书中详细介绍了QuartusⅡ工具的使用、VH

- xilinx fpga芯片的结温

hahaha6016

硬件设计fpga开发

xilinxfpga芯片的结温,结温这个含义是啥1.“结温”是半导体器件(比如XilinxFPGA芯片)常用的一个术语,全称是“结温”(JunctionTemperature),指的是芯片内部晶体管结点(PN结)的温度2.结温是芯片内部最关键的温度点,代表晶体管内部结点的实际温度,通常比芯片表面的温度或者散热器的温度要高。3.结温对芯片性能、稳定性和寿命影响很大。如果结温过高,芯片可能会出现性能下

- XILINX FPGA如何做时序分析和时序优化?

InnoLink_1024

FPGAVerilogRTL设计fpga开发

时序分析和时序优化是FPGA开发流程中关键步骤,确保设计在目标时钟频率下正确运行,避免时序违例(如建立时间或保持时间不足)。以下以XilinxKintex-7系列FPGA为例,详细介绍时序分析和时序优化的方法、工具、流程及实用技巧,结合Vivado工具链,力求清晰、全面且实用。1.时序分析概述时序分析的目的是验证FPGA设计是否满足时序约束,即信号在规定时间内正确传递,确保逻辑功能和性能。时序分析

- FPGA设计中的数据存储

cycf

FPGA之道fpga开发

文章目录FPGA设计中的数据存储为什么需要数据存储FPGA芯片内部的载体触发器查找表块存储FPGA芯片外部的资源RAM应用场合ROM特征简介实现载体应用场合FIFO特征简介FIFO使用小技巧之冗余法FIFO写接口缓存FIFO读接口缓存“冗余法”总结根据数据流的稳定性与存储操作的容错性,决定采用RAM模式还是FIFO模式STACK特征简介实现载体应用场合SummaryFPGA设计中的数据存储为什么需

- FDMA读写AXI BRAM交互:FPGA高速数据传输的核心技术

芯作者

D1:ZYNQ设计fpga开发

在图像处理系统中,当1080P视频流以每秒60帧的速度传输时,传统DMA每帧会浪费27%的带宽在地址管理上——而FDMA技术能将这些损失降至3%以内现代FPGA系统中,高效数据搬运往往是性能瓶颈的关键所在。当你在手机上流畅播放4K视频、在自动驾驶系统中实时处理激光雷达点云时,背后都依赖于FDMA(FlexibleDirectMemoryAccess)与AXIBRAM的高效交互技术。本文将深入探讨这

- XILINX Ultrascale+ Kintex系列FPGA的架构

InnoLink_1024

FPGARTL设计芯片fpga开发架构

Xilinx(现为AMD)KintexUltraScale+系列FPGA是基于16nmFinFET工艺的高性能、中等成本的现场可编程门阵列,专为高带宽、低功耗和成本效益的应用设计,广泛用于5G通信、数据中心、视频处理、航空航天等领域。以下详细介绍KintexUltraScale+系列FPGA的架构,结合其关键组件、特性和功能模块,并提供示例代码以展示时序约束的定义。1.KintexUltraSca

- 【技术架构解析】国产化双复旦微FPGA+飞腾D2000核心板架构

Future_Comtech

fpga开发fpga数据采集数据处理

本文就一款基于飞腾D2000核心板与两片高性能FPGA的国产化开发主板进行技术解析,包括系统架构、主要硬件模块、关键接口及软件环境,重点阐述各子系统间的数据路径与协同工作方式,旨在为行业内同类产品设计与应用提供参考。随着国产化要求的加速以及国产处理器芯片的性能不断提升,主板均基本可实现全国产化方案。本方案设计之初主要面向高速网络通信场景,提供高带宽、低延迟的数据收发能力。采用飞腾D20008核处理

- 前沿FPGA开发:技术与管理的有效结合

AI天才研究院

AI大模型企业级应用开发实战AgenticAI实战AI人工智能与大数据fpga开发ai

前沿FPGA开发:技术与管理的有效结合关键词:FPGA开发、技术管理、前沿技术、项目管理、资源优化摘要:本文深入探讨了前沿FPGA开发中技术与管理有效结合的重要性和具体方法。在FPGA技术不断发展的今天,单纯依靠技术或管理都难以实现项目的成功。通过将先进的FPGA技术与科学的管理理念相结合,能够提高开发效率、优化资源配置、降低成本并提升产品质量。文章详细阐述了FPGA开发的核心概念、相关算法原理、

- 基于 STM32+FPGA 的快速傅里叶频域图像在 TFT 中显示的设计与实现(项目资料)(ID:8)

嵌入式资料库

嵌入式项目合集fpga开发stm32嵌入式硬件单片机

目录摘要1绪论1.1研究背景与意义1.2国内外研究现状1.3研究内容与目标2系统方案设计2.1总体架构设计2.2硬件方案设计2.2.1主控模块选型2.2.2FPGA模块选型2.2.3TFT显示模块选型2.2.4通信方案设计2.3软件方案设计2.3.1FFT算法实现方案2.3.2频域图像渲染方案3硬件电路设计3.1STM32最小系统电路3.2FPGA模块电路3.3TFT显示模块电路3.4软件IIC通

- 【优秀文章】7月优秀文章推荐

优秀文章智能自主运动体与人工智能技术——环境感知、SLAM定位、路径规划、运动控制、多智能体协同作者:fpga和matlabC++之红黑树认识与实现作者:zzh_zao【手把手带你刷好题】–C语言基础编程题(十)作者:草莓熊Lotso飞算JavaAI:从“码农”到“代码指挥官”的终极进化论作者:可涵不会debug前端网页开发学习(HTML+CSS+JS)有这一篇就够!作者:一颗小谷粒

- SQL的各种连接查询

xieke90

UNION ALLUNION外连接内连接JOIN

一、内连接

概念:内连接就是使用比较运算符根据每个表共有的列的值匹配两个表中的行。

内连接(join 或者inner join )

SQL语法:

select * fron

- java编程思想--复用类

百合不是茶

java继承代理组合final类

复用类看着标题都不知道是什么,再加上java编程思想翻译的比价难懂,所以知道现在才看这本软件界的奇书

一:组合语法:就是将对象的引用放到新类中即可

代码:

package com.wj.reuse;

/**

*

* @author Administrator 组

- [开源与生态系统]国产CPU的生态系统

comsci

cpu

计算机要从娃娃抓起...而孩子最喜欢玩游戏....

要让国产CPU在国内市场形成自己的生态系统和产业链,国家和企业就不能够忘记游戏这个非常关键的环节....

投入一些资金和资源,人力和政策,让游

- JVM内存区域划分Eden Space、Survivor Space、Tenured Gen,Perm Gen解释

商人shang

jvm内存

jvm区域总体分两类,heap区和非heap区。heap区又分:Eden Space(伊甸园)、Survivor Space(幸存者区)、Tenured Gen(老年代-养老区)。 非heap区又分:Code Cache(代码缓存区)、Perm Gen(永久代)、Jvm Stack(java虚拟机栈)、Local Method Statck(本地方法栈)。

HotSpot虚拟机GC算法采用分代收

- 页面上调用 QQ

oloz

qq

<A href="tencent://message/?uin=707321921&Site=有事Q我&Menu=yes">

<img style="border:0px;" src=http://wpa.qq.com/pa?p=1:707321921:1></a>

- 一些问题

文强chu

问题

1.eclipse 导出 doc 出现“The Javadoc command does not exist.” javadoc command 选择 jdk/bin/javadoc.exe 2.tomcate 配置 web 项目 .....

SQL:3.mysql * 必须得放前面 否则 select&nbs

- 生活没有安全感

小桔子

生活孤独安全感

圈子好小,身边朋友没几个,交心的更是少之又少。在深圳,除了男朋友,没几个亲密的人。不知不觉男朋友成了唯一的依靠,毫不夸张的说,业余生活的全部。现在感情好,也很幸福的。但是说不准难免人心会变嘛,不发生什么大家都乐融融,发生什么很难处理。我想说如果不幸被分手(无论原因如何),生活难免变化很大,在深圳,我没交心的朋友。明

- php 基础语法

aichenglong

php 基本语法

1 .1 php变量必须以$开头

<?php

$a=” b”;

echo

?>

1 .2 php基本数据库类型 Integer float/double Boolean string

1 .3 复合数据类型 数组array和对象 object

1 .4 特殊数据类型 null 资源类型(resource) $co

- mybatis tools 配置详解

AILIKES

mybatis

MyBatis Generator中文文档

MyBatis Generator中文文档地址:

http://generator.sturgeon.mopaas.com/

该中文文档由于尽可能和原文内容一致,所以有些地方如果不熟悉,看中文版的文档的也会有一定的障碍,所以本章根据该中文文档以及实际应用,使用通俗的语言来讲解详细的配置。

本文使用Markdown进行编辑,但是博客显示效

- 继承与多态的探讨

百合不是茶

JAVA面向对象 继承 对象

继承 extends 多态

继承是面向对象最经常使用的特征之一:继承语法是通过继承发、基类的域和方法 //继承就是从现有的类中生成一个新的类,这个新类拥有现有类的所有extends是使用继承的关键字:

在A类中定义属性和方法;

class A{

//定义属性

int age;

//定义方法

public void go

- JS的undefined与null的实例

bijian1013

JavaScriptJavaScript

<form name="theform" id="theform">

</form>

<script language="javascript">

var a

alert(typeof(b)); //这里提示undefined

if(theform.datas

- TDD实践(一)

bijian1013

java敏捷TDD

一.TDD概述

TDD:测试驱动开发,它的基本思想就是在开发功能代码之前,先编写测试代码。也就是说在明确要开发某个功能后,首先思考如何对这个功能进行测试,并完成测试代码的编写,然后编写相关的代码满足这些测试用例。然后循环进行添加其他功能,直到完全部功能的开发。

- [Maven学习笔记十]Maven Profile与资源文件过滤器

bit1129

maven

什么是Maven Profile

Maven Profile的含义是针对编译打包环境和编译打包目的配置定制,可以在不同的环境上选择相应的配置,例如DB信息,可以根据是为开发环境编译打包,还是为生产环境编译打包,动态的选择正确的DB配置信息

Profile的激活机制

1.Profile可以手工激活,比如在Intellij Idea的Maven Project视图中可以选择一个P

- 【Hive八】Hive用户自定义生成表函数(UDTF)

bit1129

hive

1. 什么是UDTF

UDTF,是User Defined Table-Generating Functions,一眼看上去,貌似是用户自定义生成表函数,这个生成表不应该理解为生成了一个HQL Table, 貌似更应该理解为生成了类似关系表的二维行数据集

2. 如何实现UDTF

继承org.apache.hadoop.hive.ql.udf.generic

- tfs restful api 加auth 2.0认计

ronin47

目前思考如何给tfs的ngx-tfs api增加安全性。有如下两点:

一是基于客户端的ip设置。这个比较容易实现。

二是基于OAuth2.0认证,这个需要lua,实现起来相对于一来说,有些难度。

现在重点介绍第二种方法实现思路。

前言:我们使用Nginx的Lua中间件建立了OAuth2认证和授权层。如果你也有此打算,阅读下面的文档,实现自动化并获得收益。SeatGe

- jdk环境变量配置

byalias

javajdk

进行java开发,首先要安装jdk,安装了jdk后还要进行环境变量配置:

1、下载jdk(http://java.sun.com/javase/downloads/index.jsp),我下载的版本是:jdk-7u79-windows-x64.exe

2、安装jdk-7u79-windows-x64.exe

3、配置环境变量:右击"计算机"-->&quo

- 《代码大全》表驱动法-Table Driven Approach-2

bylijinnan

java

package com.ljn.base;

import java.io.BufferedReader;

import java.io.FileInputStream;

import java.io.InputStreamReader;

import java.util.ArrayList;

import java.util.Collections;

import java.uti

- SQL 数值四舍五入 小数点后保留2位

chicony

四舍五入

1.round() 函数是四舍五入用,第一个参数是我们要被操作的数据,第二个参数是设置我们四舍五入之后小数点后显示几位。

2.numeric 函数的2个参数,第一个表示数据长度,第二个参数表示小数点后位数。

例如:

select cast(round(12.5,2) as numeric(5,2))

- c++运算符重载

CrazyMizzz

C++

一、加+,减-,乘*,除/ 的运算符重载

Rational operator*(const Rational &x) const{

return Rational(x.a * this->a);

}

在这里只写乘法的,加减除的写法类似

二、<<输出,>>输入的运算符重载

&nb

- hive DDL语法汇总

daizj

hive修改列DDL修改表

hive DDL语法汇总

1、对表重命名

hive> ALTER TABLE table_name RENAME TO new_table_name;

2、修改表备注

hive> ALTER TABLE table_name SET TBLPROPERTIES ('comment' = new_comm

- jbox使用说明

dcj3sjt126com

Web

参考网址:http://www.kudystudio.com/jbox/jbox-demo.html jBox v2.3 beta [

点击下载]

技术交流QQGroup:172543951 100521167

[2011-11-11] jBox v2.3 正式版

- [调整&修复] IE6下有iframe或页面有active、applet控件

- UISegmentedControl 开发笔记

dcj3sjt126com

// typedef NS_ENUM(NSInteger, UISegmentedControlStyle) {

// UISegmentedControlStylePlain, // large plain

&

- Slick生成表映射文件

ekian

scala

Scala添加SLICK进行数据库操作,需在sbt文件上添加slick-codegen包

"com.typesafe.slick" %% "slick-codegen" % slickVersion

因为我是连接SQL Server数据库,还需添加slick-extensions,jtds包

"com.typesa

- ES-TEST

gengzg

test

package com.MarkNum;

import java.io.IOException;

import java.util.Date;

import java.util.HashMap;

import java.util.Map;

import javax.servlet.ServletException;

import javax.servlet.annotation

- 为何外键不再推荐使用

hugh.wang

mysqlDB

表的关联,是一种逻辑关系,并不需要进行物理上的“硬关联”,而且你所期望的关联,其实只是其数据上存在一定的联系而已,而这种联系实际上是在设计之初就定义好的固有逻辑。

在业务代码中实现的时候,只要按照设计之初的这种固有关联逻辑来处理数据即可,并不需要在数据库层面进行“硬关联”,因为在数据库层面通过使用外键的方式进行“硬关联”,会带来很多额外的资源消耗来进行一致性和完整性校验,即使很多时候我们并不

- 领域驱动设计

julyflame

VODAO设计模式DTOpo

概念:

VO(View Object):视图对象,用于展示层,它的作用是把某个指定页面(或组件)的所有数据封装起来。

DTO(Data Transfer Object):数据传输对象,这个概念来源于J2EE的设计模式,原来的目的是为了EJB的分布式应用提供粗粒度的数据实体,以减少分布式调用的次数,从而提高分布式调用的性能和降低网络负载,但在这里,我泛指用于展示层与服务层之间的数据传输对

- 单例设计模式

hm4123660

javaSingleton单例设计模式懒汉式饿汉式

单例模式是一种常用的软件设计模式。在它的核心结构中只包含一个被称为单例类的特殊类。通过单例模式可以保证系统中一个类只有一个实例而且该实例易于外界访问,从而方便对实例个数的控制并节约系统源。如果希望在系统中某个类的对象只能存在一个,单例模式是最好的解决方案。

&nb

- logback

zhb8015

loglogback

一、logback的介绍

Logback是由log4j创始人设计的又一个开源日志组件。logback当前分成三个模块:logback-core,logback- classic和logback-access。logback-core是其它两个模块的基础模块。logback-classic是log4j的一个 改良版本。此外logback-class

- 整合Kafka到Spark Streaming——代码示例和挑战

Stark_Summer

sparkstormzookeeperPARALLELISMprocessing

作者Michael G. Noll是瑞士的一位工程师和研究员,效力于Verisign,是Verisign实验室的大规模数据分析基础设施(基础Hadoop)的技术主管。本文,Michael详细的演示了如何将Kafka整合到Spark Streaming中。 期间, Michael还提到了将Kafka整合到 Spark Streaming中的一些现状,非常值得阅读,虽然有一些信息在Spark 1.2版

- spring-master-slave-commondao

王新春

DAOspringdataSourceslavemaster

互联网的web项目,都有个特点:请求的并发量高,其中请求最耗时的db操作,又是系统优化的重中之重。

为此,往往搭建 db的 一主多从库的 数据库架构。作为web的DAO层,要保证针对主库进行写操作,对多个从库进行读操作。当然在一些请求中,为了避免主从复制的延迟导致的数据不一致性,部分的读操作也要到主库上。(这种需求一般通过业务垂直分开,比如下单业务的代码所部署的机器,读去应该也要从主库读取数