FPGA学习笔记(六)------锁相环PLL

文章目录

-

- 前言

-

- 概要

- 应用领域

- 组成部分

- 分类

- 性能指标

- 实现原理

- 构建模块

-

- 鉴频鉴相器(PFD)

- 参考计数器

- 反馈计数器N

- 补充

-

- 模n计数器

- D触发器

前言

概要

锁相回路(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,锁相回路会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁相”(Phase-locked)。

应用领域

锁相回路在众多领域有应用,如无线通信、数字电视、广播等。具体的应用范围包括但不限于:

- 无线通信系统收发模块 (Transceiver)

- 数据及时钟恢复电路 (Clock and Data Recovery - CDR)

- 频率综合电路 (Frequency synthesizer)

- 跳频通信 (Frequency-hopping spread spectrum - FHSS)

- 数字电视接收机

组成部分

一个锁相回路电路通常由以下模块构成:

- 鉴频鉴相器(PFD)(或鉴相器:PD)

- 低通滤波器(LPF)

- 压控振荡器(VCO)

- 反馈回路(通常由一个分频器(Frequency divider)来实现)

分类

按照实现技术,可以分为模拟锁相回路(Analog PLL)和数字锁相回路(Digital PLL)。

按照反馈回路,可以分为整数倍分频锁相回路(Integer-N PLL)和分数倍分频锁相回路(Fractional-N PLL)。

按照鉴频鉴相器的实现方式,可以分为电荷泵锁相回路(Charge-Pump PLL)和非电荷泵锁相回路。

按照环路的带宽,它可以分为宽带锁相回路(Wide band loop PLL)和窄带锁相回路(Narrow band loop PLL)。

性能指标

对于锁相回路来说,最关键的性能是在于相位噪声(Phase noise)和动态性能(Dynamics)。

锁相回路的相位噪声对通信系统的整体性能影响甚大,因此设计中对相位噪声的要求有具体而严格的指标要求。

锁相回路的动态性能决定了它能够同步参考源的速度和精度,以及在多大范围内能够跟踪参考源。

锁相回路的动态性能包括:锁定时间(Lock time),捕获范围(Capture range),锁定范围(Hold range)等。

另外,锁相回路的稳定性指标包括:环路带宽(Loop bandwidth),相位裕度(Phase margin)等。

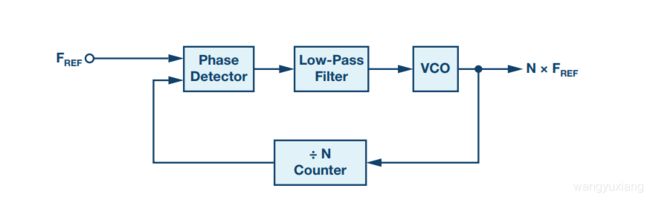

实现原理

鉴相器PD以用来比较两个输入频率,度量并输出他们之间的相位差异(若差异是在频率上,锁相环会在不同频率出进行周期性输出)。如果 f i n f_{in} fin不等于 f v c o f_{vco} fvco,由此产生的误差信号在通过滤波及放大后会使 f v c o f_{vco} fvco靠近 f i n f_{in} fin,在合适的条件下, f v c o f_{vco} fvco会很快“锁定” f i n f_{in} fin,并使相位关系保持一定。

鉴相器通过滤波后输出一个直流信号;VCO的输入信号是通过输入频率得到的;输出信号是在本地产生的,频率与 f i n f_{in} fin相等,是 f i n f_{in} fin“纯净”的副本( f i n f_{in} fin本身不够“纯净”,有噪声)。

以上:

f i n = f V C O ( N = 1 ) f_{in}=f_{VCO}\qquad\quad(N=1) fin=fVCO(N=1)

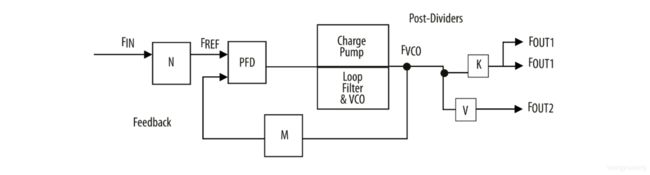

在反馈路径中插入M计数器会使VCO的震荡频率是FREF信号频率的M倍, FREF信号等于输入时钟( FIN) 除以预缩放计数器( N)。

参考频率用以下方程描述:

F R E F = F I N N F_{REF}=\frac{F_{IN}}{N} FREF=NFIN

VCO输出频率为:

f V C O = f R E F × M = F I N N × M f_{VCO}=f_{REF}\times{M}=\frac{F_{IN}}{N}\times{M} fVCO=fREF×M=NFIN×M

PLL的输出频率为:

F O U T = f V C O K = F I N × M N × K F_{OUT}=\frac{f_{VCO}}{K}=\frac{F_{IN}\times{M}}{N\times{K}} FOUT=KfVCO=N×KFIN×M

构建模块

每个模块的简单原理描述如下:

- 鉴频鉴相器: 对输入的参考信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。

- 低通滤波器: 将输入信号中的高频成分滤除,保留直流部分送至压控振荡器。

- 压控振荡器: 输出一个周期信号,其频率由输入电压所控制。

- 反馈回路 : 将压控振荡器输出的信号送回至鉴频鉴相器。通常压控振荡器的输出信号的频率大于参考信号的频率,因此需在此加入分频器以降低频率。

鉴频鉴相器(PFD)

鉴频鉴相器将+IN端的FREF输入与和-IN端的反馈信号进行比较。它使用两个D型触发器和一个延迟元件。一路Q输出使能正电流源,另一路Q输出使能负电流源。这些电流源就是所谓电荷泵。

- P1(负压开启 VGS < 0 ) , N1(正压开启 VGS > 0)构成CMOS反相器(非门)

如果+IN处的频率远高于–IN处的频率(低于则相反),因此输出多数时间处于高电平状态。 +IN上的第一个上升沿会发送输出高电平,并且这种情况会一直持续到–IN上出现第一个上升沿。在实际的系统中,这就意味着输出及VCO的输入会被进一步拉高,进而造成–IN处的频率增加。这恰恰是期望达到的效果。这样, -IN频率将随着VCO频率的提高而提高,两个PFD输入最终会收敛或锁定到相同频率。

| +IN(FREF) | -IN(FOUT/N) | OUT |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

参考计数器

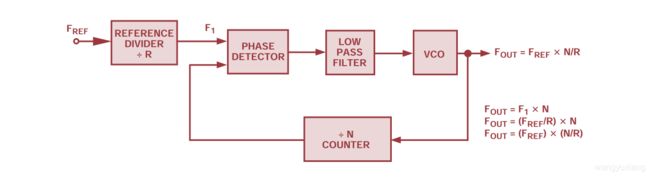

在传统的整数N分频频率合成器中,输出频率的分辨率由施加于鉴相器的参考频率决定。因此,举例来说,如果需要200 kHz间距(如GSM电话中),那么参考频率必须为200 kHz。但是,获取稳定的200 kHz频率源并不容易。一种合理的做法是采用基于晶振的良好高频源并对其进行分频。例如,从10 MHz频率基准开始并进行50分频,就可以得到所需的频率间隔。

反馈计数器N

N计数器也称为N分频器,是用于设置PLL中输入频率和输出频率之间关系的可编程元件。 N计数器的复杂性逐年增长。除简单的N计数器之外,经过发展,后来还包括“预分频器”,后者可具有“双模”。 这种结构已经发展成为下列情况下固有问题的一种解决方案:需要超高频输出时使用基本N分频结构来反馈至鉴相器。例如,我们假设需要一个间距为10 Hz的900 MHz输出。可以使用10 MHz参考频率并将R分频器设为1000。然后,反馈中的N值必须为90,000。这意味着,至少需要一个能够处理900 MHz输入频率的17位计数器。为处理此范围,需要考虑在可编程计数器之前加上一个固定计数器元件,以便将超高输入频率拉低至标准CMOS的工作频率范围内。该计数器称为预分频器,如图所示。

然而,使用标准的预分频器会导致其他并发症。现在,系统分辨率降低(F1 × P)。可通过使用双模预分频器来解决这个问题。这种方法可以享有标准预分频器种种优势,又不会牺牲系统分辨率。双模预分频器是一种可通过外部控制信号将分频比从一个值切换为另一个值的计数器,通过使用带有A和B计数器的双模预分频器,仍可以保持F1的输出分辨率。不过,必须满足下列条件

补充

模n计数器

通常的做法是将计数器加1,再将结果除以n(n为最大值),余数为结果。这种计数器用途很广,如循环队列。

counter = (counter + 1)%n;

相比来讲,使用比较的方法来实现的话效率会更高:

counter = counter + 1; //到n清零

if( counter >= n )

{

counter = 0;

}

D触发器

D 触发器是在控制信号 CLK 为 0 时,才会接收输入信号 D 的值,并将这个值锁存起来,当控制信号 CLK 变为 1 时,输出信号 Q 才会被改变。那么 D 触发器,其实就是在CLK 这个时钟信号由 0 变为 1 的这个边沿进行触发的,通常我们就将这种触发方式称为边沿触发,通过这种边沿触发方式的 D 触发器我们也将它称为边沿 D 触发器。

D 锁存器的触发方式是电平触发,和我们刚刚讲的边沿触发是有所不同的。这种不同是由于锁存器和触发器的电路结构不同造成的。这里需要注意的是,由于 D 锁存器的功能和 D 触发器的功能是一样的, 所以在编写代码时很容易把 D 锁存器当成 D 触发器来使用,这种情况我们是要避免的。