为什么超链接如此重要

为什么超链接对于HDL调试至关重要

在万维网上冲浪是工程师每天最容易做的事情之一;调试他们的设计和测试平台却是最难的事情之一。EDA多年来一直在努力构建使调试易于处理的工具。最近的进展借用了流行的计算机应用程序(如Web浏览器)的易用性,并将其应用于一些最复杂的设计和验证问题。超链接是这里的一项关键技术。

文本编辑器的局限性

自从上世纪90年代早期逻辑综合被广泛采用以来,设计人员就开始使用硬件描述语言(HDL),如Verilog和VHDL。HDL还包含用于验证的构造,这些特性随着时间的推移而增强。因此,设计和验证工程师可以以代码形式捕获完整的环境,并且经常使用传统的文本编辑器来输入和修改HDL描述。即使对于导航代码和跟踪信号这样的简单任务,这也带来了挑战。

在一个文件中,工程师可以使用他们首选的文本编辑器中的“搜索”或“查找”功能来查找给定信号名称的所有匹配项。它们将HDL代码中的名称复制到搜索字段中,然后文本编辑器逐步处理每个匹配项。工程师可以找出信号的定义位置,或者哪些输入和输出连接到信号上。但这种“简单”的解决方案很快就会失效。

设计和验证环境不再包含在单个HDL文本文件中,而是分布在成百上千个文件中。这样做有充分的理由,包括在多个工程师之间划分代码并实现重用。从内部和外部来源添加设计和验证库以及IP,甚至会为文件列表添加更多内容。试图检查或调试设计的工程师面临的挑战是找到哪些文件包含感兴趣的信号。

大多数EDA工具都运行在基于Unix的操作系统上,“grep”实用程序是在文件集合中查找文本字符串的最常见方法。工程师可以复制感兴趣信号的名称,将其粘贴到grep命令中,并查看哪些文件包含该名称。由于每个文件都是在文本编辑器中打开的,因此可以将名称复制到搜索字段中,并以与单个文件设计相同的方式进行定位。显然,这并不是一种有效的方法,但今天仍有工程师使用它来编写HDL代码,而这些工程师只依赖于简单的文本编辑器。

IDEs的情况

超越传统的编辑器到集成开发环境(IDE)为设计和验证工程师提供了大量的功能。IDE根据所使用的特定语言(或多个语言)进行调整,因此代码是在上下文中分析的,而不是纯文本。典型的IDE可以完成一系列非常有用的任务,包括:

- 对代码执行语法检查;

- 对代码执行静态分析检查;

- 突出显示和格式化代码;

- 编译或解释代码;

- 以及链接到模拟器以进行运行时调试。

虽然IDE最初是为软件编程语言开发的,但它们同样适用于HDL、专用验证语言(如e)和SystemVerilog的验证相关特性。上面列表中的功能对于输入和编辑设计和测试台、执行详细的代码检查、理解外部设计以及调试失败的测试用例具有明显的价值。用一个直观的图形用户界面(GUI)包装这些功能有助于构建一个解决方案,该解决方案可以节省数月的时间。

HDL IDE可以很好地解决的一个具体问题是通过跨多个文件的设计拆分来跟踪信号。工程师不再需要grep在文件列表中查找信号名,然后在返回的每个文件中搜索该名称。工程师不再需要担心部分名称匹配或在不同设计范围内使用相同的信号名称。IDE将分析整个设计,并“知道”每个信号的每个连接。信号可以通过任意数量的文件和多个设计层次结构自动跟踪。

这种洞察力需要强大的分析引擎来支持IDE的GUI。编译器必须始终在后台运行,每当工程师进行更改并更新设计和测试台的内部数据库时,都要快速处理源代码。该数据库必须连接所有的设计和验证元素,它们是用SystemVerilog、Verilog、VHDL、E甚至C/C++编写的,从而可以进行跨越源代码语言的分析和信号跟踪。

超链接将分析和跟踪的结果直接提供给设计和验证工程师。超链接的概念已经有50多年的历史了,但是随着上世纪90年代中期网络浏览器的出现,超链接的使用迅速增加,点击一个“做正确的事情”的链接已经成为每个人的第二天性。因此,将超链接的使用扩展到用于捕获、验证和调试HDL设计的IDE变得完全自然和合乎逻辑。

超链接的效率与价值

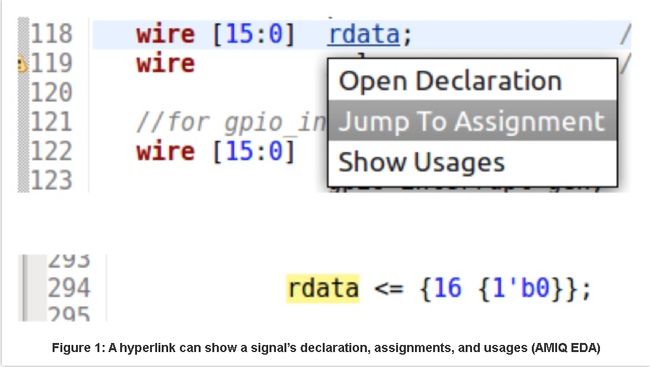

图1显示了一个使用超链接在SystemVerilog设计或测试台中跟踪信号的示例。将鼠标悬停在信号名称上,同时按住“Ctrl”键,该名称将成为超链接。用户可以选择打开信号的声明,跳到下一个信号分配,或显示信号的所有用法。这个屏幕截图和下面示例中的截图来自设计验证工具(DVT)eclipse IDE。

这种类型的超链接以多种方式加快设计探索和调试速度。避免了简单文本编辑器所需的grep搜索周期。信号的分配和使用由工具决定,因此工程师不必手动区分输入、输出或左手/右手位置。如果设计的一个不相关的部分在不同的范围内也有一个“rdata”信号,那么IDE不会感到困惑。单击超链接是即时的,跟踪信号的每一步都大大减少了,从烦人地滚动浏览不相关的grep匹配的数分钟到几秒钟的时间。

第一个例子为具有超链接的IDE提供了一个令人信服的例子,但几乎没有涉及任何可能的方面。如SystemVerilog之类的现代语言非常复杂。标识符可以是简单的信号或连线,但也可以是模块、接口、宏、结构、字段、类、任务、函数等。不是每个工程师都是面向对象编程的专家。一个复杂的IDE可以帮助理解和调试设计和测试台。

如果超链接标识符是一个类,那么IDE可以显示整个类继承树和类成员(图2)。这个例子是符合通用验证方法(UVM)标准的SystemVerilog测试台的一部分。一个IDE可以拥有UVM的内置知识,也许可以对标准组件进行特殊的分析和显示/高亮显示。

作为另一个例子,假设标识符是在它出现的类之外实现的任务。在这种情况下,超链接会在任务实现出现的任何位置打开它。图3显示了这是如何工作的。传统的greping和searching过程再次被IDE中单击超链接所取代。直接跳转到定义或用法的能力适用于许多SystemVerilog标识符类型中的任何一种,提供了一致且易于学习的界面。

图4显示了一个代码片段,其中标识符是用作case语句中表达式的参数。超链接跳转到将为该参数选择的case语句的分支。这种方法只适用于枚举常量和参数,因此这是一个很好的特定于构造的功能的例子。超链接选项专门针对所选语言中的特定结构进行了调整,在本例中为SystemVerilog。其他类型的构造可能会生成层次结构树、图表、示意图等。

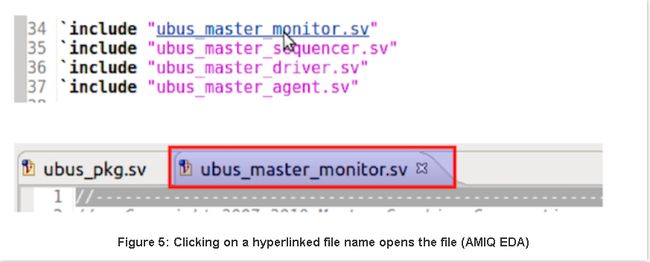

IDE分析模拟器将读取的整个文件列表,以及影响代码解释的所有模拟选项和参数。其中包括传统的预处理器指令,其中一些指令几乎被普遍使用。例如,“include”指令告诉预编译器在该点插入文件的内容。图5显示了包含文件的名称如何直接超链接到该文件的内容。此步骤将文件名的复制和粘贴保存到编辑器的“打开文件”命令中。

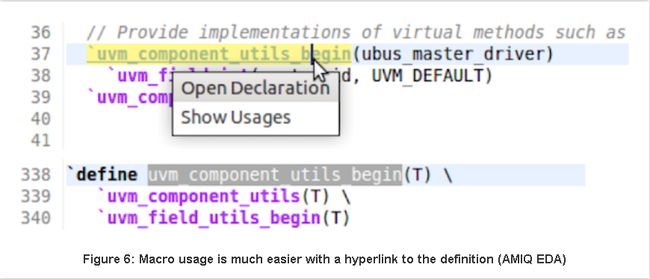

“define”预处理器结构也被广泛使用,尤其是用于定义文本宏。如图6所示,IDE可以跳转到宏的定义,甚至可以逐级扩展它。关于UVM最常见的抱怨之一是它严重依赖SystemVerilog宏。与前面的例子一样,IDE超链接有问题的构造和“只做正确的事情”的能力绕过了SystemVerilog的一些复杂性,并减少了UVM学习曲线。

结论

调试一个大型半导体设计及其复杂的测试台是一个很大的挑战;即使是仔细阅读代码并试图理解它的功能也很困难。处理打印输出或使用简单的文本编辑器不再是一种可接受的方法。设计和验证工程师需要一个现代化的IDE来执行复杂的分析,并使用智能超链接在灵活的GUI中导航代码。工程师和他们的经理必须评估EDA市场的选择,选择一个功能强大的、并且在许多以前的项目中证明过的解决方案。

原文链接:https://www.techdesignforums.com/practice/technique/why-hyperlinks-are-essential-for-hdl-debugging/