VARON设计流程及示例

本文介绍有关使用VARON的设计流程和基础示例的介绍。

设计流程

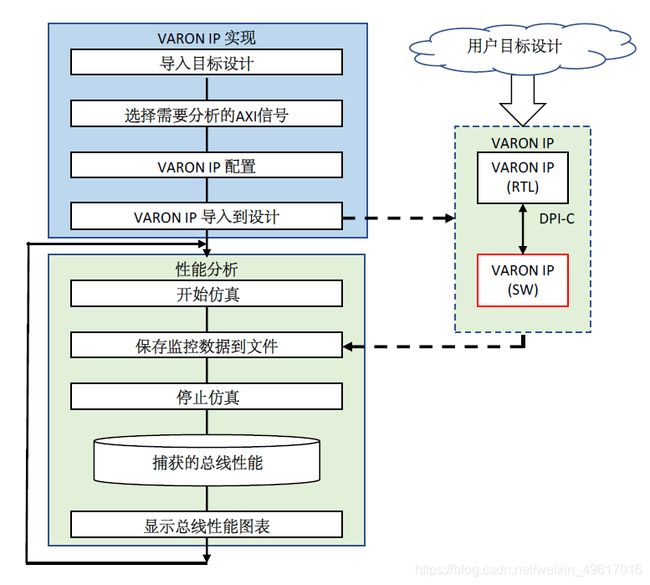

图1显示了VARON的设计流程。 第一步,将VARON IP导入用户的目标设计。 VARON IP用RTL(Verilog HDL)编写。 这允许用户将VARON IP导入到Verilog HDL或VHDL编写的用户设计和环境中。第二步是选择要观察的AXI信号,然后完成VARON IP配置并注入用户设计。

VARON IP实施完成后,运行仿真,将选择的信号数据提取到文件中并进行仿真。

最后,启动VARON监控器并加载总线性能数据,然后使用各种性能分析工具开始性能分析。

VARON IP配置

图2显示了VARON IP。 VARON IP由时钟计数器,读取侧/写入侧的延迟计数器和RTL编写的缓冲区组成,以及由C语言编写的文件输出软件组成。

1. 时钟计数器

- ACLK的计数(由ARESETn初始化)

- 单位时间的测量:周期间隔(单位时间)可以从仿真参数中设置。

2. 延迟计数器(事务)

- 一个延迟计数器可以捕获1个AXI总线端口。

- 捕获交易时间和突发长度。

3. 缓冲区(DPI-C)

- 收集时钟计数器和每个端口的事务处理信息,并通过DPI-C将其传递到文件输出软件以输出文件。

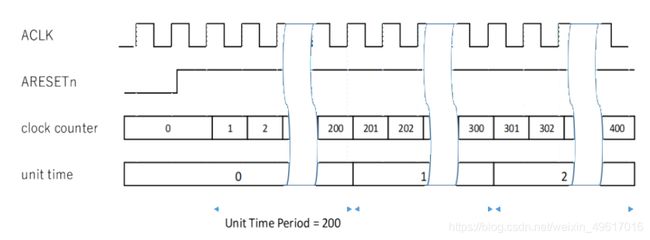

时钟计数器

时钟计数器对ACLK的数量进行计数,并将时间戳添加到VARON IP输出的输出数据中(由ARESETn初始化)。 收集每个计数器的捕获数据并将其一次存储到缓冲区中,以减少软件(DPI-C)对硬件仿真器性能的调用。 在捕获AXI事件和写入时间到文件里之间存在延迟。 每个捕获数据都包含时间戳信息,以补偿将捕获存储到缓冲区时的延迟。

有两种方法可以对单位时间的间隔时间进行编程,一种是从仿真参数开始,另一种是VARON RTL输入信号。

时钟计数器时序如图3所示。

单位时间计数器通过参数设置周期来输出时间,或者从用户电路输入表示单位时间周期的信号。

延迟计数器

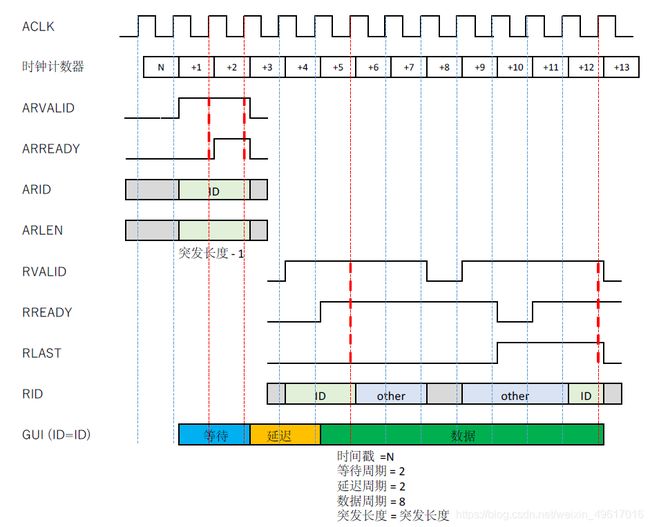

图4显示了延迟计数器的读取通道时间以及与GUI图表的关系。

图5显示了延迟计数器的写入通道时间以及与GUI图表的关系。

AXI总线时序观察

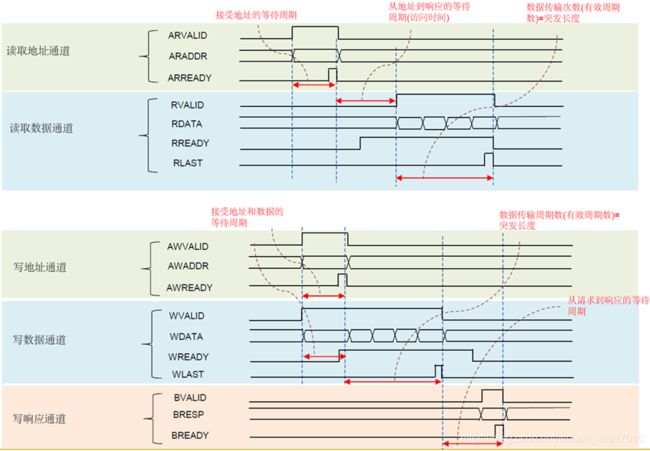

图6显示了在AXI总线标准上读取/写入事务的捕获时序。

例如,VARON测出读取事务需要3个等待周期。

- 地址等待周期是从ARVALID声明到ARREADY声明,它表示从主机到主机发送地址到从机的延迟。

- 访问时间是指从接受地址到开始数据传输的时间。

- 数据周期是从接收到的第一个突发数据到最后一个接收的突发数据的周期,取决于RVALID和RREADY握手,它可能与真实的传输突发长度不同。

示例设计

图7显示了一个简单的示例设计。 该示例设计包含8个读/写主通道,这些通道由主控器和2个从属端口连接到MEMC AXI总线互连,通过主控器的AXI ID和接收到的端口号产生从属(连接到MEMC)端口AXI ID。

在典型的性能分析中,用户希望捕获来自MEMC端口的数据传输量和突发长度,以及来自主端口的等待周期,等待时间周期和数据传输量。 此示例将连接主机和互连的AXI总线记录为“主侧”,将连接互连和MEMC的AXI总线记录为“从侧”。

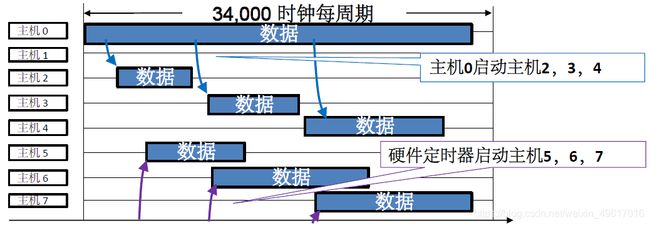

图8是运行此示例设计的34,000个周期时仿真结果的主机访问图像视图。 对于两个MEMC端口,VARON每200个时钟周期(单位时间)捕获一次数据传输量。

VARON IP 的生成和连接

此步骤将创建配置文件以生成VARON IP,并定义要探测的信号列表,然后生成VARON IP。 Verilog RTL编写的VARON IP允许用户使用用户电路进行仿真。 最后,运行仿真并通过VARON Monitor执行性能分析。

有关VARON IP的生成和连接,后续会有文章详细介绍。

分析结果

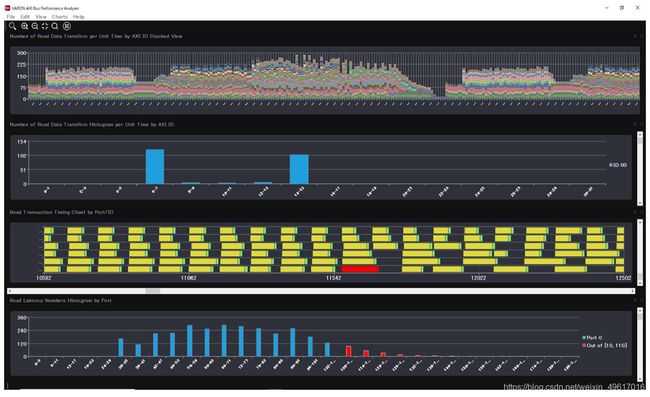

示例设计中的VARON监控器分析图示例如图9所示。VARON 仿真版本,允许用户通过一次仿真获得所有分析图。该仿真运行80,000个时钟周期,单位时间(用于测量数据量的间隔时间)为200个时钟周期。

以下是图9中分析结果图表的列表。

- 每个AXI ID和单位时间的从站侧读取数据传输量

- 每个AXI ID和单位时间的从站侧读取数据传输量分布

- 每个端口/ ID的主站侧读取事务时序图

- 每个端口的主端读取延迟分布

VARON监视器允许用户对分析图进行以下操作。

- 垂直度/水平滚动(通过滚动条和光标键。)

- 放大,缩小和缩放适合(通过按钮和按键+,-,f。)

- 工具提示:将鼠标移至捕获并显示值。

- 指定显示的时钟周期数(时间序列图)

- 搜索意外值(按钮和按键:Ctrl-F)

- 打开对话框->设定范围(最小和最大值)->以红色突出显示超出范围的捕获

以下是查找具有较大延迟值的事务的示例。

1. VARON通过“按端口读取延迟数字直方图”图表帮助用户查找延迟值超出目标范围的事务。

①单击“按端口读取延迟号直方图”图。

②单击“查找超出范围的值”按钮。

③为Port0设置等待时间0的最小值和等待时间100的最大值,然后单击确定。

④超出范围的事务将突出显示为红色。

2.此示例通过“按端口/ ID读取事务时序图”图表查找延迟值超出目标范围的事务。

①点击“按端口/ ID读取交易时序图”图。

②单击“查找超出范围的值”按钮。

③为Port0设置等待时间0的最小值和等待时间100的最大值,然后单击“确定”。

④超出范围的事务将突出显示为红色。

⑤单击工具栏的向右箭头按钮,然后搜索下一个错误。