时序分析之基本概念

Quartus II中的时序分析为静态时序分析,即STA(static timing analysis)。STA分析的对象是同步逻辑电路,通过路径计算延迟的总和,分析时序间的相对关系。

业界最流行的分析工具是Primetime,此系列以Altera 的Quartus 为基础的。

STA主要就是分析fmax、tsu、th、tco这几个参数。这些参数的定义如下:

fMAX : 在不违反内部建立(tSU) 和保持(tH) 时间要求时,可以达到的最大时钟频率。它是时序分析中最重要的指标,综合表现所设计时序的性能。

tSU : 触发器的时钟沿到来之前,输入数据或使能信号稳定不变的最小时间间隔,如果不满足,数据就无法打入触发器。

tH : 触发器的时钟沿到来之后,输入数据或使能信号稳定不变的最小时间间隔,如果不满足,数据也无法打入触发器。

tCO :时钟信号在触发(寄存)器的输入引脚上发生跳变之后,输入信号从寄存器D端到Q端的最短时间。

各参数的图形描述:

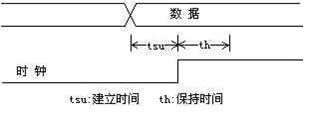

fig1. tsu 与 th 的关系:

如果不满足 建立/保持 时间,触发器可能会经历亚稳态。这两个时间是站在同步时序电路的整个路径上看的。 tsu 与 th是和slack有关的两个量。

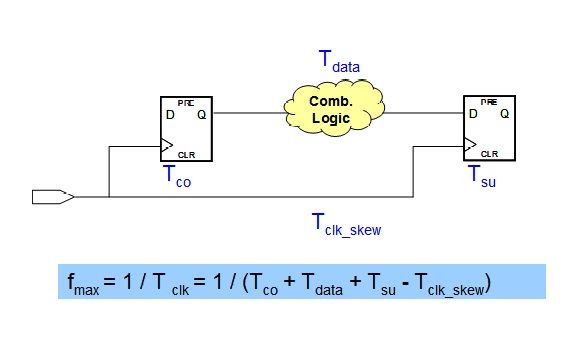

fig2. fMAX的计算公式:

fmax —电路能跑的最高频率; tclk—电路能跑的最小周期

Tco — 时钟跳变后,从D经过触发器到Q的延迟

Tdata — 组合逻辑本身造成的延迟

Tsu — 触发器本身的建立时间

Tcik_skew — 时钟偏斜

Tco 与Tsu 为触发器内部固有延迟,典型值为1~2ns,即Quartus Handbook中的 mTco 和 mTsu 。可知,只可能通过缩短触发器间的组合逻辑电路延迟来提高同步时序电路的工作频率。因而,就有必要把比较大的组合逻辑分解为较小的几块,并在中间插入触发器来提高电路的工作频率,这也就是“流水线”技术的基本原理。