华为的笔试题时遇到了很多同步和异步电路的问题,将学习过程记录如下。学习链接https://www.cnblogs.com/IClearner/p/6485389.html

一、概述

不同时钟域信号间通信需要同步处理,防止亚稳态的传播

-单比特信号:两级同步器(电平,边沿检测和脉冲)

-多比特信号:fifo,双口ram,握手信号

总体分为以下几种情况:

--跨同步/异步时钟域

--快(慢)时钟域到慢(快)时钟域

--控制/数据信号传输

一、控制信号传输(单比特信号)

1)时钟同源,时钟周期之间非整数倍(异步,单位宽,慢到快)

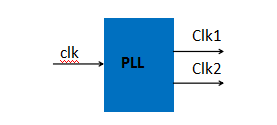

假如时钟源的时钟频率为clk,经过PLL后,产生一个时钟clk1和一个时钟clk2,一个时钟是另外一个时钟的非整数倍,相位是随时间变化的。可看作异步时钟。

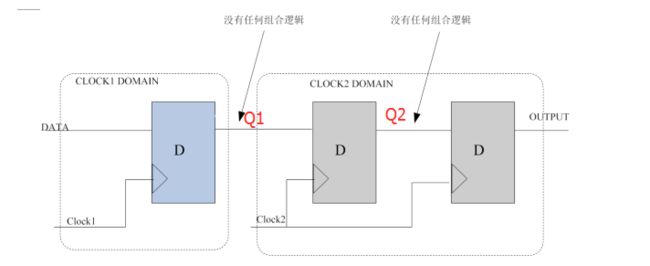

两级同步器——双D触发器

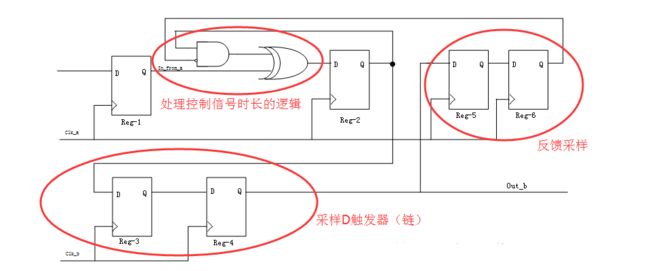

要注意,其中间不能有任何组合逻辑。双D触发器(触发器链)只能抑制亚稳态往下传输(或者减小其往下传输的概率),并不一定能够同步正确的控制信号的值,这与亚稳态稳定后的值有关。从慢到快,只有亚稳态的问题;而从快传输到慢,不仅有要抑制亚稳态往下传播的问题,还有控制信号丢失的问题,这里就需要延长控制信号的长度或者采取其他措施

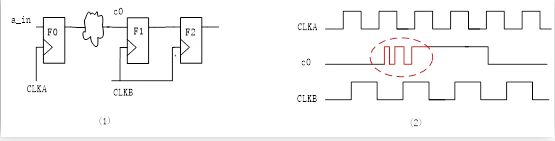

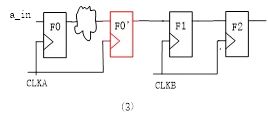

错误1 :时钟域A的组合逻辑信号直接敲两级DFF同步到时钟域B

如上图(1)所示虽然时钟域A的逻辑信号c0 传输到时钟域B的时候,也用了两级DFF 同步器,但我们知道组合逻辑电路各个输入信号的不一致性以及组合逻辑内部路径的延时时间不一样,运算后的信号存在毛刺如图(2),而我们又无法预先知道CLKB 的上升沿何时会到来,CLKB 采样到的信号就无法预知,这显然不是我们想要的结果。因此,要想CLKB 能采到稳定的信号,时钟域A的信号必须是经过CLKA 敲过,在一个时钟周期内是稳定的信号,如图(3)所示:

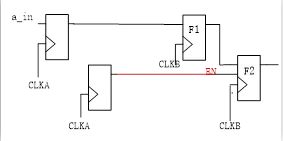

错误2 : Clock-gating enable 信号没有经过异步处理

在下图中a_in 信号经过CLKA的DFF敲过,再送到两级DFF 同步器处理,完全没毛病。但是F2的使能信号EN是从时钟域A来的,当EN信号变化的时候,由于时钟域不一样,无法保证使能之后的CLKB信号采样数据时满足setup/hold time 要求,这时F2输出信号也就变得无法预测了。

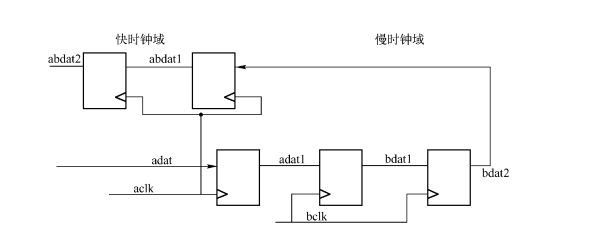

2)跨异步时钟域(异步、单位宽、快到慢)

可以采取跟前面类似的方法:首先触发器链抑制亚稳态的传输一定是要的,然后是快时钟到慢时钟的问题,也就是采样短脉冲的控制信号问题。

其实原理很简单,当控制信号变高时(adat与adat1),慢时钟域的触发器链(bdat1和bdat2)进行采样,采样得到的高电平(bdat2)后,也就是确认采样得到控制信号后,再通过触发器链反馈给快时钟域(abdat1和abdat2),让快时钟域把控制信号拉低(拉低的或者处理时长在后面有电路),就完成控制信号的正确跨时钟传输。

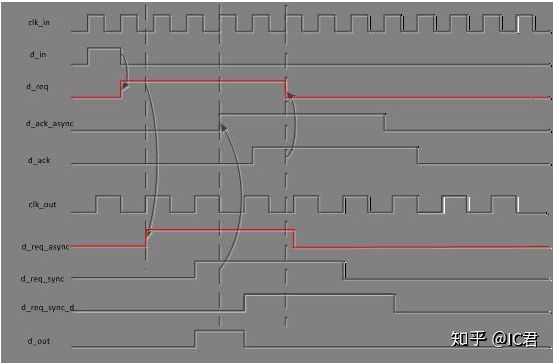

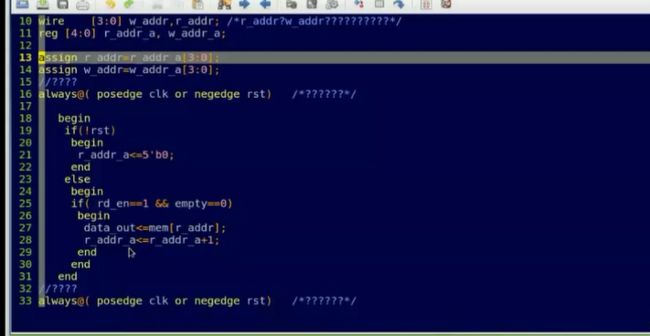

信号d_in 所处时钟域是clk_in,且d_in只有1T(1T指一个时钟脉冲宽度) 的宽度,想要传送到clk_out 时钟域(clk_out 跟clk_in不相关)。因为clk_out 和 clk_in相位关系不确定,时钟周期大小关系不确定,无法保证一定能采样到d_in。因此需要把d_in展宽,产生d_req 信号;d_req 信号一直拉高,经过clk_out时钟域两级DFF 同步器后,得到d_reg_sync;取d_req_sync 上升沿1T,即可得到传送到clk_out 时钟域的d_out。此时,d_in 从clk_in 传送到clk_out 的任务就算是结束了。

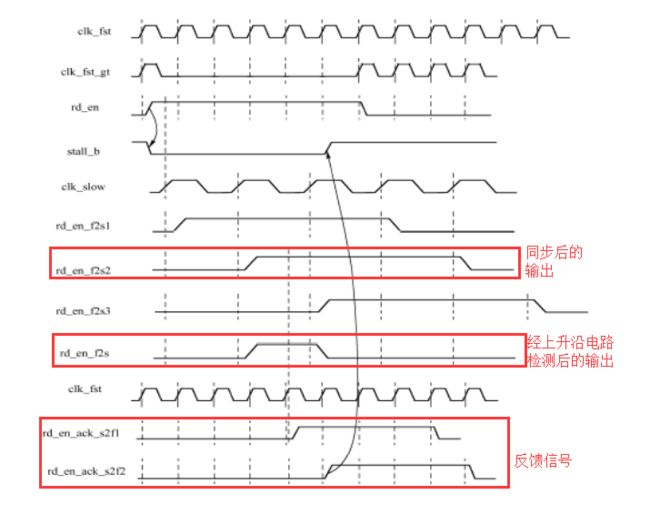

但对于handshake 电路来说,任务还没结束,因为d_req 还一直是高电平。因此,需要把d_req_sync 信号再用两级DFF同步器,传回clk_in 时钟域,得到d_ack信号;当clk_in 看到d_ack拉高后,就可以把d_req 信号拉低,到这里一个handshake电路行为才算是结束了。

根据上面的波形图,可以看到握手协议异步信号处理并不复杂,但是细心的朋友应该会注意到,这个处理方法信号传递的速度相对较慢。从图2 的波形来看,至少需要3个clk_in 和2个clk_out时钟周期。根据不同的应用需求,人们会对图2的波形做不同的改造。但万变不离其宗,原理都是一样的,电路也大同小异。

①d_reg的产生:

always@(posedge clk_in or negedge rst_n) begin

if(rst_n==1'b0) d_reg<=1'b0;

else if (d_in==1'b1) d_reg<=1'b1;

else if (d_ack==1'b1) d_reg<=1'b0;

end

②d_out的产生:

assign d_out=d_req_sync & (~d_req_sync_d);//取d_req_sync 上升沿1T

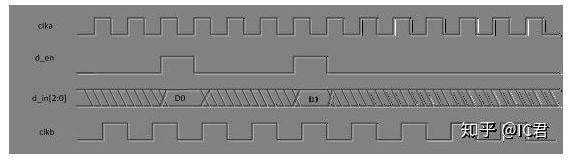

③假设时钟域clka比clkb 频率高,如果输入信号的两个相邻脉冲D0和D1非常较近,如下图所示,如果使用握手协议处理,会发生怎样的事情?

A:不能接收到数据D1。因为两者的展宽信号重叠了。可以用异步fifo。(如果应用可以接受,改变优先级,牺牲D0,传输D1 。)

当然,在慢时钟域阶段,我们也可以添加边沿检测(上升沿)电路,一方面让输出只有一个脉冲的控制信号,另一方面准确地进行控制,以防止亚稳态的干扰。

在上面的握手方案中,我们通过反馈信号进行控制信号的延时来让慢时钟域充分采样得到控制信号,本质上是也是对控制信号的延时。这个延时的具体实现,需要对控制信号的产生逻辑进行处理,来满足延时的要求,如下所示:(不认识那个是异或)

“下面太难没看懂”

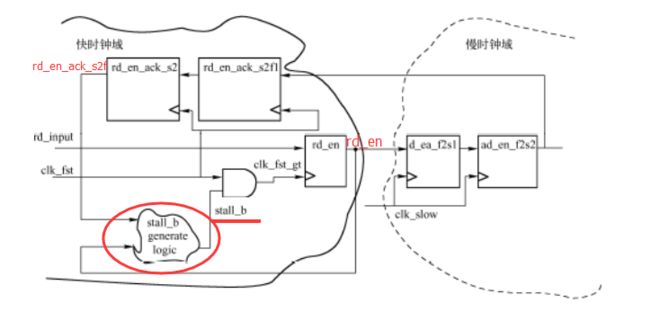

除了上面对控制信号处理之外,我们还可以对快时钟域的时钟动点手脚,具体电路如下所示:

这里通过让快时钟域触发器(特指rd_en触发器)的时钟停止工作的方式,让控制信号保持一定的时间。时钟停止之后,rd_en触发器的输出就会保持不变,等到反馈信号回来,告知慢时钟域采样得到高电平后,再恢复快时钟域的时钟,波形如下所示:

当然,这是一个组合电路。这样子会令后面的输出电路产生毛刺,类似于门控时钟那样,于是乎我们就可以使用门控时钟那样的技巧,防止输出产生毛刺。