沧小海基于xilinx srio核的学习笔记之第三章 xilinx srio核介绍(一)结构介绍

总的目录在这哦~

https://blog.csdn.net/z123canghai/article/details/114648658

目录

3.1 SRIO核概述

3.2 SRIO核的结构剖析

3.2.1 逻辑层接口(LOG)

3.2.2 Buffer接口(BUF)

3.2.4 寄存器空间

3.1 SRIO核概述

RapidIO互连架构,与目前大多数流行的集成通信处理器、主机处理器和网络数字信号处理器兼容,是一种高性能、包交换的互连技术。它能够满足高性能嵌入式工业在系统内部互连中对可靠性、增加带宽,和更快的总线速度的需求。SRIO即串行rapidio,srio核的设计标准来源于RapidIO Interconnect Specification rev2.2,它支持1x,2x和4x三种模式,每通道的速度支持1.25Gbaud,2.5Gbaud,3.125Gbaud,5.0Gbaud和6.25Gbaud五种。

Xilinx的srio核分为逻辑层(Logical Layer),缓冲(Buffer)和物理层(Physical Layer)三个部分。逻辑层定义了总体协议和包格式,它包括了RapidIO设备发起和完成事务的必要信息。传输层提供了RapidIO包传输过程中的路由信息。物理层描述设备级接口细节,例如包传输机制、流控、电气特性和低级错误管理。这种划分不需要对传输层或物理层规范进行修改,就可以灵活的给逻辑层规范添加新的事务类型。

逻辑层的功能有:

1、支持发起方(Initiator)和目标方(Target)同时操作;

2、支持门铃事务(DOORBELL)和消息事务(MESSAGE);

3、有维护事务(MAINTENANCE)设计了专用的端口;

4、使用标准AXI4-Lite和AXI4-Stream接口的简单握手机制来控制数据流

5、采用AXI4-Lite接口和AXI4-Stream接口,支持简单的握手机制去控制数据流,

6、支持可编程的Source ID,支持16-bit的device IDs(可选)。

缓冲层功能有:

1、支持8,16和32包的独立可配置的TX和RX 缓存深度;

2、支持独立的时钟

3、支持可选的发送数据流控制。

物理层功能有:

1、支持可配置的空闲序列1和空闲序列2;

2、支持关键请求流(Critical Request Flow);

3、支持多播事件。

3.2 SRIO核的结构剖析

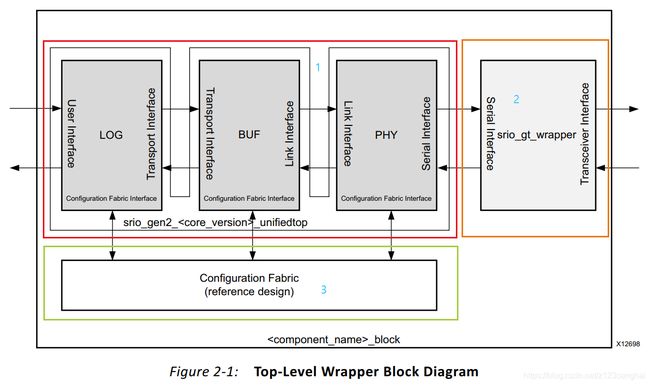

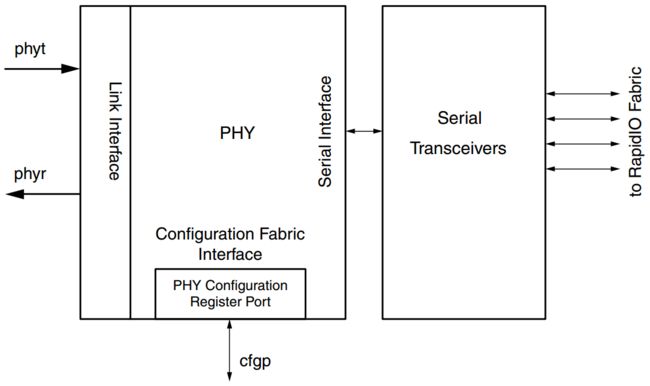

本节内容主要是《PG007》的第二张内容,如下图是SRIO核的结构框图。大致的分为三个部分一是依据srio协议结合xilinx设计思想对SRIO顶层封装,我们不需要关注srio物理层及控制符号等内容,只需要完成应用层设计,二是调用xilinx的高速串行通讯硬核模块,实现串并间的转换以及GTP/GTX的所实现功能,三是配置结构模块,实现对核些配置的更改,是对“1”中内容。下文对各个模块进行详细阐述。

如下图是打开核的主要内容,其结构也与上述一致。

3.2.1 逻辑层接口(LOG)

逻辑层(LOG)是核的顶层接口,实现与用户数据的交互。主要包括:用户接口(User Interface),传输接口(Transport Interface)和配置接口(Configuration Fabric Interface)三个接口,如下图所示。这些接口可从

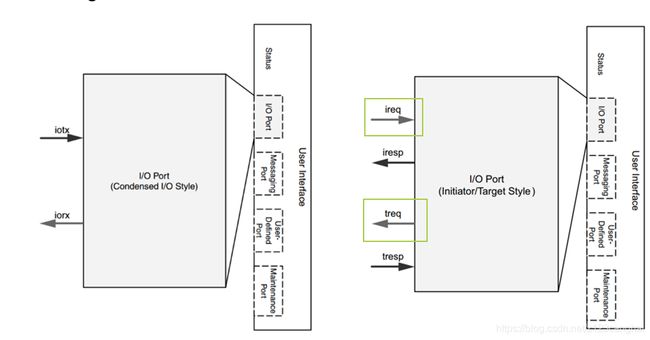

1、I/O端口(I/O Port)

I/O端口能被配置为两种类型:Condensed I/O(Condensed:简明)或Initiator/Target。这两种类型可以在IP核的配置中进行选择。I/O端口的数据流协议是AXI4-Stream协议,它支持两种类型的包格式,分别是HELLO格式与SRIO Stream格式。如下图所示,我们一般使用Initiator/Target这种模式。

其中Condensed I/O端口类型减少了用于发送和接收I/O包的端口数目。它只用一个AXI4-Stream通道来发送所有类型的包,同样,也只用一个AXI4-Stream通道去接收所有类型的包。AXI4-Stream去掉了地址项,允许无限制的数据突发传输规模,用ready/valid握手信号在主从设备之间传输信息,tlast信号指示传输的最后一个数据从而确定包的边界,用tkeep字节使能信号指示数据中的有效字节,它还包括有效数据tdata信号以及用户数据tuser信号用来传输实际的包数据。

Initiator/Target端口类型把请求事务与响应事务分别处理,所以一共有4个AXI4-Stream通道用于I/O事务的传输。如上图右是Initiator/Target端口的示意图,绿框(灰色箭头)表示请求事务,其它表示响应事务。

请求:本地设备(Local Device)生成的请求(Requests)通过ireq通道发送,远程设备(Remote Device)产生的响应包通过iresp通道接收来完成整个事务的交互过程。

响应:远程设备(Remote Device)生成的请求(Requests)通过treq通道接收,本地设备(Local Device)产生的响应包通过tresp通道发送来完成整个事务的交互过程。

在顶层模块中,变量名与通道的对应关系如下:

1、s_axis_ireq* 对应于ireq通道

2、m_axis_iresp* 对应于iresp通道

3、m_axis_treq* 对应于treq通道

4、s_axis_tresp* 对应于tresp通道

2、消息端口(Messaging Port)

消息端口是一个可选的接口,消息事务既能在I/O端口上发送,也能在独立的消息端口上发送。独立的消息端口类型为Initiator/Target类型。下图是消息端口的示意图

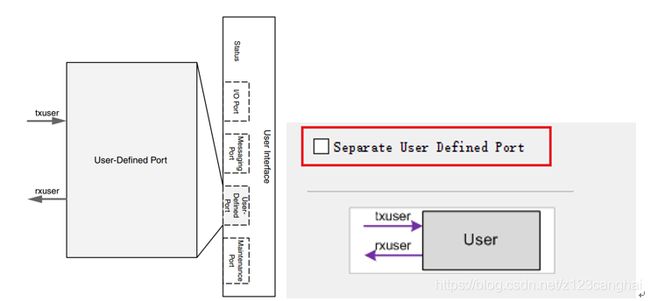

3、用户自定义端口(User-Defined Port)

用户自定义端口是一个可选的端口,它包括两个AXI4-Stream通道,一个用于发送另一个用来接收。用户自定义端口仅仅支持SRIO Stream格式的事务。下图是用户自定义端口的示意图和可选配置图。

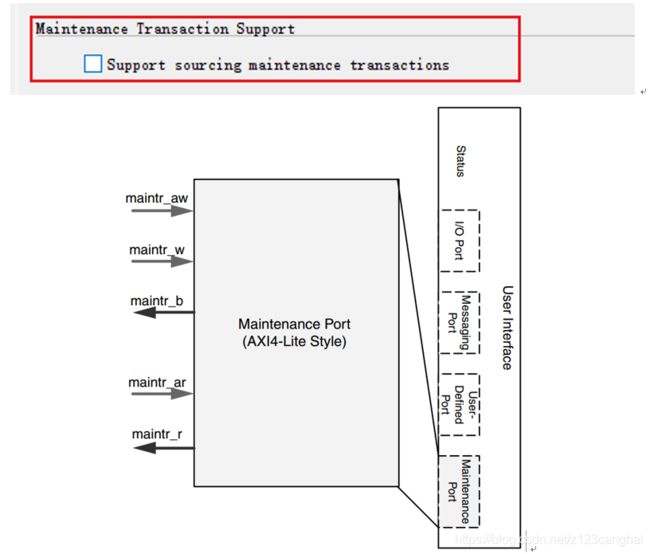

4、维护端口(Maintenance Port)

维护端口使用的是AXI4-Lite接口协议,AXI4-Lite接口允许用户访问本地或远程配置空间,也是可选端口。下图是AXI4-Lite维护端口示意图

5、状态(Status)

维用户接口的状态信号包括deviceid和port_decode_error,定义如下表所示

| 信号 |

方向 |

描述 |

| deviceid[15:0] |

输出 |

Base DeviceID CSR(偏移地址为0x60)寄存器的值 |

| port_decode_error |

输出 |

此信号为高说明用户自定义端口未使能,一个不支持的事务被接收并立即丢弃。当下一个支持的事务包在任意用户接口被接收以后此信号被拉低。这个信号同步于log_clk信号 |

6、配置接口

1、配置主端口,通过配置结构对本地配置空间(用于LOG,BUF和PHY)进行读写

2、LOG配置寄存器端口,它是用于读取和写入定义为逻辑层或传输层一部分的寄存器的从接口。

3.2.2 Buffer接口(BUF)

BUF对于保证包传递和流控制操作是必需的。Xilinx提供了一种可配置的缓冲区解决方案,可以在系统性能和资源需求之间进行权衡。发送缓冲区负责对传出事务进行排队,并管理这些数据包在链路接口上进入PHY的流程。通过Vivado IDE可以将TX和RX缓冲区的大小配置为深度为8、16或32个数据包的值。TX缓冲区是一种存储转发缓冲区,旨在降低数据包到数据包的延迟,以最大程度地提高流吞吐量。传输缓冲区必须保存每个数据包,直到链接伙伴设备已成功接收它为止,此时释放该数据包以为其他数据包腾出空间。 如果缓冲区中积累了多个未发送的数据包(通常在发生流控制时发生),则BUF会根据类型和优先级对数据包进行重新排序,首先发出响应数据包,然后发出请求。

接收缓冲区充当FIFO,用于将数据存储和转发到LOG接收路径。接收缓冲器还具有域交叉逻辑,该逻辑允许逻辑层/用户设计和PHY以不同的时钟速率运行。 与发送缓冲区设计一样,建议将此逻辑用于多通道内核,关于缓冲和流控的具体内容会在下面章节介绍。

物理层(PHY)用来处理链路训练(Link Training),初始化(Initialization)和协议(Protocol),同时还包括包循环冗余校验码(CRC)与应答标识符的插入。物理层接口与高速串行收发器相连。串行收发器在IP核中被设计为一个外部的例化模块以降低用户使用模型的难度。物理层接口的示意图如下图所示

物理层与Buffer层通过两个AXI4-Stream通道相连,同时物理层有一个通道的AXI4-Lite接口与配置结构相连,可以通过这个通道访问物理层的配置空间。物理层还通过一个串行接口(Serial Interface)与串行收发器(Serial Transceivers)相连。

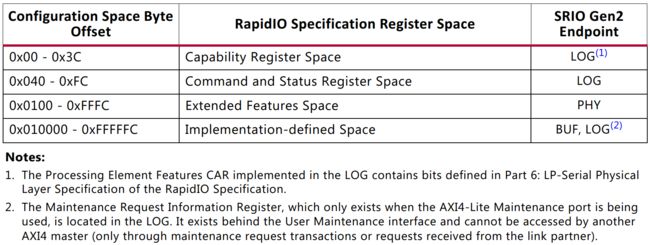

3.2.4 寄存器空间

寄存器空间定义分布在整个RapidIO规范中,RapidIO的寄存器空间如下表所示

有很多,具体参考《PG007》的“Register Space”内容。

就关于官方的实例分析,不仅实现了对核的配置、仿真,还对信号进行了整理,如下所示

开发软软件为vivado2016.4,打开工程点击“Flow”选择“open static simulation”打开静态仿真可直接查看信号波形

相关程序可关注“沧小海的FPGA”微信公众号回复“SRIO”即可获取,感谢关注~