SoC设计与验证——大型IP——PCIE控制器

注意:部分图片和表述来源于网络,引用处会说明。

一、PCIE简介

PCIE总线技术,也叫计算机内部总线技术”Peripheral Component Interconnect”,即外围组件互联。PCIe一般用在大型数据中心,可以接显卡,网卡等片外设备。

1.1 PCIe相关概念

PCIe的基本结构包括根组件(Root Complex),交换器(Switch)和各种终端设备(Endpoint)

- 设备类型

PCIe子系统有4种设备类型,分别是Root Complex(RC),PCIe switch,PCIe End Point和PCIe Bridge。如下图所示,switch设备和RC设备可以向上或向下连接PCIe总线,PCIe总线的最底层为EP设备。

- RC

在PCI规范中也被称为HOST主桥,RC模块需要接受操作系统相关的硬件信号(例如接口寄存器、状态寄存器、异常寄存器、数据缓存等,小型状态机等),主要完成的事务有:

1)PCI域与IO域地址映射机制

2)实现兼容PCI设备的中断映射以及PCIe中断写事务机制

3)实现核与PCIe接口间的报文与消息类型转换

4)存储PCIe设备的配置数据 - switch

- EP

RC和EP在PCIE树形结构中扮演的角色不一样,Rp是根,EP是叶结点。从PCIE角度来看,RP可以发起CFG Rd和Wr,但是EP是不可以的。

二者在物理层和部分链路层来说可以相互访问,但是传输层却不行 - bridge

PCIe bridge用于连接慢速设备,在PCI设备中起到呈上起下的作用。例如pcie转网卡bridge、pcie转USBbridge等

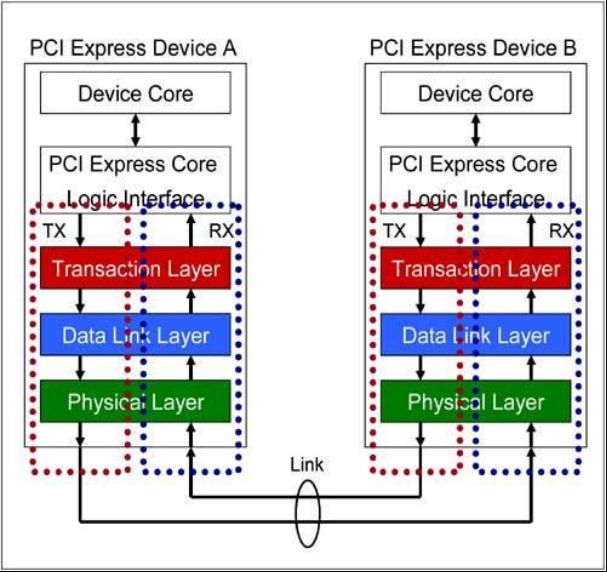

- PCIE的数据链路(lane)

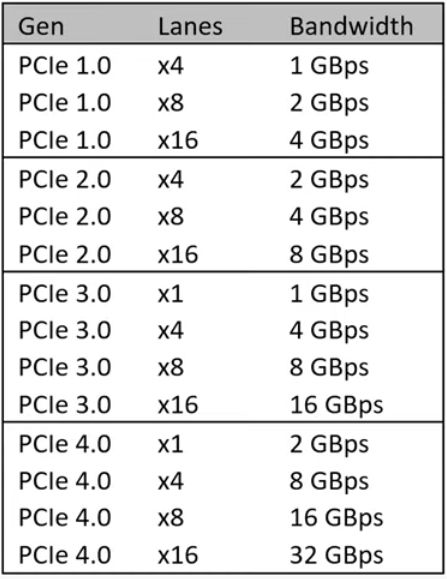

PCIe采用端到端的数据传送方式,数据的发送端和接收端都含有一个发送逻辑(TX)和接收逻辑(RX),如下图 1所示是PCIe链路的一个数据通路(lane),一个lane有两组差分信号,共四根信号线。其中接收端的RX和发送端的TX使用一组差分信号连接。一个PCIe链路可以由多个lane组成,最多有32条lane(由于物理尺寸太过庞大,一般情况下并不使用)。

如图所示,版本的PCIe的lane数不同,带宽也是不同的:

-

lane resersal和lane Inversion

通常情况下,upstream和downstream设备的连接如下图第一种连接方式连,但若使用第二种连接方式,则会对PCB的制作产生较大难度。 -

PCIE Serdes

SerDes(Serializer-Deserializer)是串行器和解串器的简称。串行器(Serializer)也称为SerDes发送端(Tx),(Deserializer)也称为接收端Rx。

SerDes的主要构成可以分为三部分,PLL模块,发送模块Tx,接收模块Rx。为了方便维护和测试,还会包括控制和状态寄存器,环回测试(loopback),PRBS(伪随机二进制码)测试等功能。

- 数据链路层被细分为包括媒体访问控制(MAC)子层。

- 物理层被细分为逻辑和电子子层。 物理逻辑子层包含物理编码子层(PCS)。

- PIPE规范还标识了物理介质连接(PMA)层,其中包括串行器/解串器(SerDes)和其他模拟电路;然而,由于SerDes实现在ASIC供应商之间差异很大,PIPE没有指定PCS和PMA之间的接口。

-

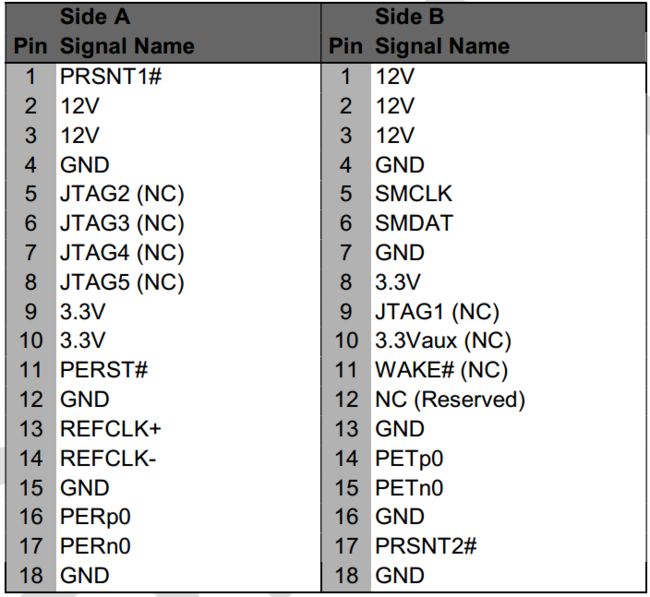

PCIe sideband信号

如下图所示是PCIe x1情况下的slot的正反面信号:

pcie控制器单

注意:在针对PCIe设备的PCB的板级设计时,PCIe Gen3的差分阻抗为300欧,而gen4是 85欧 -

Equalization Interface

因为PCIE 3.0信号的速率可以达到8Gb/s,而且链路通道走线也可能会很长,这可能会导致高速信号衰减过大,为了补偿channel的衰减需要增加传输信号的高频成分,让高频和低频能量差不多,这就是equalization。因此在PCIE 3.0的Tx和Rx端均使用了均衡设置,以补偿长链路时高速信号的衰减。

参考链接:PCIe3.0动态均衡

软件开发工程师通常不需要关心自适应均衡部分的配置,因为通常自适应均衡由硬件机制完成,详细参考链接:眼图和自适应均衡器 -

NTB

有些特殊场景下,比如传统存储系统中的多个控制器,它们之间需要同步很多数据和控制信息,希望使用PCI-E链路直接通信。但是在switch上有多个RC设备时并不可以直接通信,因为主机的BIOS或者OS在枚举同一堆PCIe总线内的设备,并为其分配访问地址,此时会出现冲突。为了满足这个需求,出现了NTB技术。

其基本原理是地址翻译,因为两个不同的系统(术语System Image,SI)各有各的地址空间,会产生重叠。那么只要 在PCI-E Switch内部将对应的数据包进行地址映射翻译,便可以实现双方通信。这种带有地址翻译的桥接技术叫做None Transparent Bridge,非透明桥。 -

PCIe总线的缺点

- 由于采用了基于总线的共享传输模式,在PCI总线上不可能同时传送两组以上的数据,当一个PCI设备占用总线时,其他设备只能等待;

- 随着总线频率从33MHz提高到66MHz,甚至133MHz(PCI-X),信号线之间的相互干扰变得越来越严重,在一块主板上布设多条总线的难度也就越来越大;

- 由于PCI设备采用了内存映射I/O地址的方式建立与内存的联系,热添加PCI设备变成了一件非常困难的工作。目前的做法是在内存中为每一个PCI设备划出一块50M到100M的区域,这段空间用户是不能使用的,因此如果一块主板上支持的热插拔PCI接口越多,用户损失的内存就越多;

- PCI的总线上虽然有buffer作为数据的缓冲区,但是它不具备纠错的功能,如果在传输的过程中发生了数据丢失或损坏的情况,控制器只能触发一个NMI中断通知操作系统在PCI总线上发生了错误

-

peer-to-peer传输

即分属于不同PCI总线域的PCI设备可以直接进行数据交换 -

ARI功能

参考链接:link

1.2 PCI和PCIe的关系

-

PCI是共享型总线,多个设备共享一条总线,这种情况下必然存在总线总裁。PCIe则是点对点连接,一个设备直接连接到另一个设备,不存在总线竞争和仲裁。

-

PCI总线上是单向传输,任意时刻只有一个方向的传输,PCIe则是任意时刻都可以双向传输。

-

PCI有很多的边带控制信号,如FRAME#, IRDY#, TRDY, STOP#等。PCIe总线上传输的都是基于包(packet),控制和其他处理都嵌入在包里。

1.3 PCIE 硬件主要模块

PCIe的设计可以分为控制器和PHY,整体设计较为复杂,一般可向IP厂商定制设计。其中控制器设计中可包含bifurcation设计。

1.2.1 PCIE控制器

- reset逻辑:通常会设置复位逻辑,通过总复位控制子复位;

- debug逻辑:监测IP状态,供设计人员debug用;

- msg处理逻辑:IP的某些信号由message处理,有CPU内核来处理;

- 子系统配置处理逻辑;

- 错误处理逻辑:查找寄存器,并记录,产生中断;

- MSI逻辑:对地址,数据通道进行监测;

- 中断逻辑:IP中某些中断可以合并;

- PHY控制逻辑:寄存器配置和控制;

- DFT:IP中会提供专门用于DFT的引脚。

- Bifurcation控制器

该控制器可以决定各个设备和PCIe插槽的通道宽度。它一般有三种方式:Hard Strap,Soft Strap或者Wait for BIOS。

- Hard Strap

通过硬件连接的方式决定PCIe通道的连接方式,一旦定义将不可修改。例如英特尔酷睿CPU通过CFG[6:5]的值决定bifurcation是一个x16还是2个x8等 - Soft Strap

通过软件的方式修改bifurcation的方式,这种配置一版储存在BIOS Image前面的discription中,可以通过工具修改,这种修改一般和BIOS无关,修改后直接烧录BIOS即可 - Wait for BIOS

纯BIOS设置,即在PCIe training之前,通过BIOS对PCIe RC的寄存器进行设置来确定通道宽度。

二、PCIe控制器的层次结构

PCI Express是一种分层协议,由设备核心层、传输事务层,数据链路层和物理层组成。

2.1 设备核心层

该层级术语PCIe的上层逻辑,负责报文生成、报文分发、控制序列

2.2 传输事务层

传输事务层定义了PCIe总线使用的总线事务,这些事务可以通过switch等设备传送到RC等其他PCIe设备,RC也可以使用这些事务访问其他PCIe设备。其主要工作包括:

- 传输层接收来自核心层的数据,将其封装为TLP(Transaction layer packet)后发向数据链路层

- 传输层也可以从数据链路层接收数据报文,发送给核心层。

- 链路训练

- 信元管理

- 处理PCIe总线的“序”

- 使用流量控制机制保护PCIe链路的使用效率

2.2.1 TLP相关

当PCIe设备相互访问时,传送的数据报文将被事务层打包为一个或多个TLP,这些TLP会向下层次继续传送,最终通过PCIe总线发送给被请求设备。

实际上一个完整的TLP包由多个字段组成,并且这些字段分别由三个层次各自构建,最后经过物理层形成最终的TLP。

- TLP格式

传输事务层完成TLP主要的部分header段和data段。

详情参考链接: PCIe控制器——数据报文TLP - 数据负载相关

当数据传输量较大时,需要根据负载的大小和限制调整为多个TLP进行传输。PCIe设备含有“Max_Payload_Size”和“Max_Payload_Size Supported”两个参数,这两个参数分别在Device Capability和Device Control寄存器定义,这两个寄存器在PCIe Capability结构中。

PCIe设备发送数据报文是,使用Max_Payload_Size参数决定TLP的最大有效负载,当PCIe设备所要传输的数据大小超过Max_payload_Size时,这段数据将被分割为多个TLP进行发送。

Max_Payload_Size supported参数固化在硬件中,指Max_Payload_Size的最大值。

2.2.2 总线事务类型

参考链接:PCIe控制器——总线传输事务

2.3 数据链路层

数据链路层保证来自于事务层的数据报文完整可靠的发送到下一层。其主要工作有:

- 来自事务层的报文将被添加sequence number前缀和CRC后缀,使用ACK/NCK协议保证报文的可靠性

- 链路训练

- 信元管理

- 流控制

- 定义多种DLLP(Data link layer packet)

2.3.1 链路训练

参考链接:PCIE控制器——链路训练

2.3.2 flow control

流控制,保证发送端的PCIe设备永远不会发送接收端PCIe设备不能接收的TLP(事务层包)。也就是说,发送端在发送前可以通过Flow Control机制知道接收端能否接收即将发送的TLP。

通过两个port间的链路层发送DLLP来实现。

2.4 物理层

电气信号转换、串并转换

三、PCIE运行机制

3.1 reset机制

PCIe设备可以根据当前的设备的运行状态选择合适的复位方式,PCIe总线提供多种复位方式的主要原因是减小PCIe设备的复位延时。其中传统复位方式的延时大于FLR方式。

3.1.1 传统复位方式(Conventional Reset)

- fundamental reset

有cold reset和hot reset两种方式,Cold Reset使用的时间最长,而Hot Reset使用的时间最短。

- cold reset

当一个PCIe设备的Vcc电源上电后,处理器系统将置该设备的PERST#信号为有效,此时将引发PCIe设备的复位方式。此时,所有使用Vcc进行供电的寄存器和PCIe端口逻辑将无条件进入初始状态。

但是使用这种方式依然无法复用使用Vaux(备用电源)供电的寄存器和逻辑,这些寄存器和逻辑只能在处理器完全掉电时彻底复位 - warm reset

在PCIe的设备完成上电后,也可能重新进行Fundamental Reset,这种复位方式也被称为Warm Reset。

- non-fundamental reset物理层的Link初始化

- hot reset

当PCIe设备出现某种异常时,可以使用软件手段对该设备进行复位。如系统软件将Bridge Control Register 的Secondary Bus Reset位置为1,该桥片将secondary总线上的PCI/PCIe设备进行Hot Reset。CPIe总线将通过TS1和TS2序列对下游设备进行Hot Reset。

在TS1和TS2序列中包含一个Hot Reset位。当下游设备收到一个TS1和TS2序列,而且Hot Reset位为1时,下游设备将使用HotReset方式进行复位操作。

HotReset方式并不属于FundamentalReset。PCIe设备进行Hot Reset方式时,也可以将PCIe设备的多数寄存器和状态恢复为初始值。

3.1.2 FLR reset

除了传统的复位方式之外,PCIe总线还提供了FLR方式。系统软件通过填写某些寄存器,如synopsys 的PCIe的IP是可以PCIeExpress Capability 的Device Control Register的第16bit完成FLR。支持FLR方式的PCIe设备需要在其BAR空间中提供一个寄存器,当系统软件对该寄存器的Function LevelReset位写1时,PCIe设备将使用FLR方式复位PCIe设备的内部逻辑。FLR方式对PCIe设备是可选的。

在多RC设备系统中,任务在指定的分区中运行,当这个任务执行完毕后,系统软件需要调整硬件资源的分区。此时受到影响的PCIe设备需要使用FLR方式复位内部的逻辑,以免造成对新的分区的资源污染,并保护之前任务的结果。

注意:FLR方式不会影响LTSSM状态机。

- 不会被FLR方式复位的寄存器

这些寄存器通常和PCIe链路相关

- Sticky寄存器。

与传统的复位方式相同,FLR方式不能复位这些寄存器,但是系统软件对部分Sticky寄存器进行修改。当Vaux(备用电源)被移除后,这些寄存器中的保存的数据才会丢失; - HwIint类型的寄存器

在PCIe设备中,有效配置寄存器的属性为HwIint,这些寄存器的值由芯片的配置引脚决定,后者上电复位后从EEPROM中获取。Cold和Warm Reset可以复位这些寄存器,然后从EEPROM中从新获取数据,但是使用FLR方式不能复位这些寄存器。 - 还有一些特殊的配置寄存器不能被FLR方式复位,如Max_Payload_Size、RCB和一些与电源管理、流量控制和链路控制直接相关的寄存器。

3.2 虚拟化技术(SR-IOV)

即virtual function技术。

参考链接:微软VF驱动描述

3.3 Bifurcation

pcie通道拆分技术,芯片厂商通过一种叫做bifurcation(分叉)的方式让主板厂商可以灵活配置,组合或者拆分PCIe通道

3.4 OS启动时与PCIe设备相关初始化过程

下面总结linux启动时PCIe设备初始化的一般性过程。

3.4.1 初始化过程

- 1)上电复位

该过程为冷复位,除了sticky寄存器,其他使用Vcc进行供电的寄存器和PCIe端口逻辑将进入初始状态 - 2)HOST寄存器配置

一般在处理器应用中,通常系统一上电CPU执行boot程序时会初始化PCIe HOST的寄存器;而在非处理器应用中,通常将PCI配置信息存放在板上的ROM中,系统上电时,ROM中的配置信息写到PCI设备的配置空间作为初始值,该过程由硬件完成 - 3)link初始化和Training

复位结束后,物理层将会启动link,一旦link的两端设备都进入初始化link Training状态,为了使数据链路层和事务层准备好连接,两端的设备将会依次进行物理层的Link初始化以及VC0的Flow Control初始化。 - 4)枚举PCI总线上的设备,建立PCIe设备树

- 5)SoC加载运行操作系统后,OS会重新枚举PCIe设备(也可以调用ROM程序枚举的结果),

3.4.2 注意点

注意:在上电复位后,一些设备在能对请求响应前需要一些额外的时间恢复,以下是一些时序准则

对应设备方面:

- 有些设备需要在reset结束后在20ms内进入LTSSM Detect阶段

- 连接的两个设备可能会在不同时间退出reset,此时每个设备都需满足在20ms进入 Link Training阶段

- 在Link Training快结束时,设备必须能够接收和处理TLPs和DLLPs

对于系统方面:

- 为了便于设备进入内部初始化,系统软件在被允许向设备提交配置请求前,需要在设备结束复位后等待指定的周期

摘自《PCI_Express_Baser3.0_10Nov10.pdf》

• With a Downstream Port that does not support Link speeds greater than 5.0 GT/s, software

20 must wait a minimum of 100 ms before sending a Configuration Request to the device

immediately below that Port.

• With a Downstream Port that supports Link speeds greater than 5.0 GT/s, software must

wait a minimum of 100 ms after Link training completes before sending a Configuration

Request to the device immediately below that Port. Software can determine when Link

25 training completes by polling the Data Link Layer Link Active bit or by setting up an

associated interrupt (see Section 6.7.3.3).

• A system must guarantee that all components intended to be software visible at boot time

are ready to receive Configuration Requests within the applicable minimum period based on

the end of Conventional Reset at the Root Complex – how this is done is beyond the scope

30 of this specification.

• Note: Software should use 100 ms wait periods only if software enables CRS Software

Visibility. Otherwise, Completion timeouts, platform timeouts, or lengthy processor

instruction stalls may result. See the Configuration Request Retry Status Implementation

Note in Section 2.3.1.

- RC设备或者系统软件在上电复位后需要等待至少 1.0 s才可以决定某个不能成功返回状态的设备是故障设备。具体时间取决于Link training完成的快慢

- 当请求配置接在PCIe Bridge后的是恶被是,时序参数Trhfa必须满足

当Link正在进行时,必须满足以下准则:

- 无论什么原因,当Link结束时,事务层和数据链接层必须进入DL_Inaction状态

- 对于Root或者switch Downstream端口,设置与Port相关的Bridge Control register的第二个Bus Reset将会引起hot reset

四、PCIE 软件驱动

4.1 PCI地址空间访问机制

参考链接:地址空间访问机制

4.2 总线枚举

总线枚举的目的是确定PCIe树形结构的拓扑,发现所有设备及其功能,通常在操作系统启动过程中进行,如下为枚举过程:

- 利用深度优先算法遍历整个PCI设备树,从Root Complex出发,寻找设备和桥,即首先读第0号总线的0号设备0号功能的配置空间

- Device ID为非全F表示有设备

- 通过HeaderType判断是桥还是EP

- 修改0号总线0号设备0号功能(P2P桥)的Primary、Secondary和Subordinate总线号

- 读1号总线的0号设备0号功能的配置空间

- 如果识别到该设备是EP设备,会根据device ID、vender ID和Class Code确定驱动;通过BAR寄存器探索设备实现的Memory或IO空间

- 通过capabilities寄存器组探索设备实现的其他功能

- 完成一个RC或者桥设备的节点上总线枚举后,会配置该HOST设备的BAR寄存器和memory limit

4.3 linux驱动

参考链接:Linux——驱动开发——PCIe驱动代码分析

五、PCIe相关验证

pcie的验证分为模块级验证和集成后的系统级验证

- BRINGUP TEST

- 寄存器读写

- IP配置检查

- 存储器集成检查

- 基本的转换种类

- SoC集成检查

- Integration TEST

- 生产者/消费者

- PCIe存储器空间

- MSIs

- 传统中断

- 系统接口错误

- PIPE/serial接口

- Advanced TEST

- ATS

- PCIe error generation

- PCIe ordering rules

- TPH

- PCIe IO virtualization

- power management

- performance analysis

- coverage analysis

六、问题整理

6.1 PCIe协议问题

- 遍历PCIe总线,简历PCIe树是否是CPU通过RC设备进行?

6.2 调试问题

6.2.1 Link training

- 没有link建立的原因

- reset issue导致

- receiver detection issue

- link quality issue

- link在不正确的link width下training,通常是lane(s) reliability issue所致

- reset后设备速率不够快的原因

原因:host设备在外部pcie设备ready之前就开始枚举,导致总线上的设备并没有按最快速度进行link

-

speed变成8.0 GT/s或者equalization失败

原因:link的速度自动返回到2.5 GT/s -

LTSSM进入recovery状态的原因

- link quality issue(Encoding error/ framing error)

- Flow control timeout

- Device / link partner malfunction

- Low-power entry / exit issue