数字电路与Verilog设计期末实验

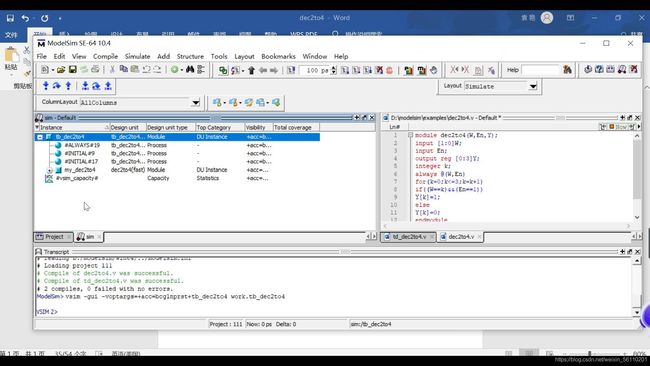

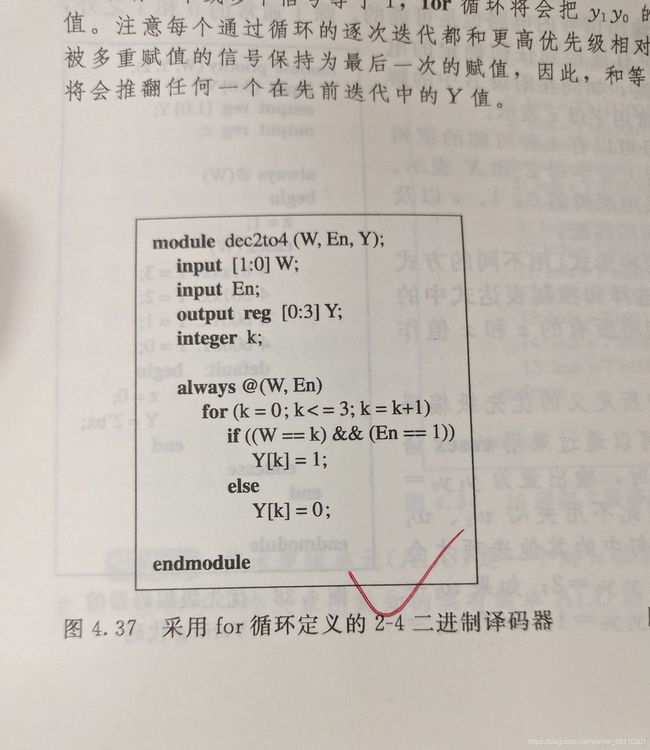

采用for循环定义的2-4二进制译码器

1、实验目的

例4.18图4.37展示了如何用for循环详细定义一个2-4的译码器电路。循环的作用就是对于k=0, …3重复执行if-else语句4次。如果W≈0及En=1,第一次循环迭代令y=1。类似地,其他3个迭代根据W和En的值确定y1、Y2及,Y3的值。

根据需要增加矢量W和Y的大小,并且令k的终值为n-1(即k=n-1),就可定义一个大型的n到2”的译码器。

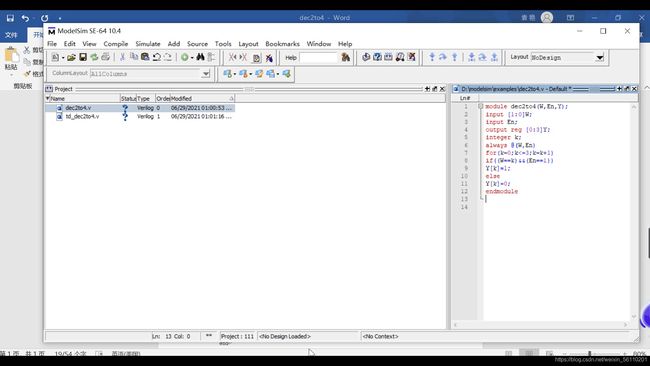

2、实验代码

3、实验代码

module dec2to4(W,En,Y);

input [1:0]W;

input En;

output reg [0:3]Y;

integer k;

always @(W,En)

for(k=0;k<=3;k=k+1)

if((Wk)&&(En1))

Y[k]=1;

else

Y[k]=0;

endmodule

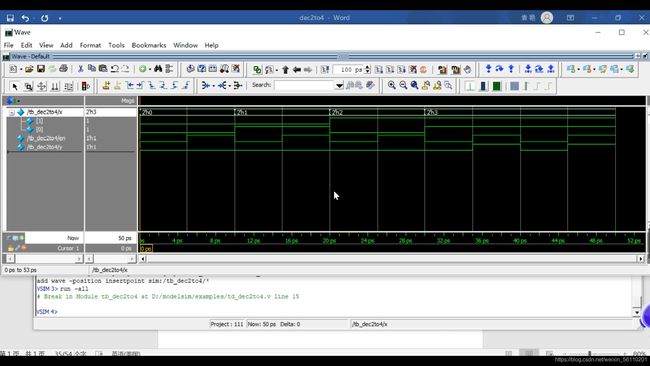

4、测试代码

`timescale 1 ps/ 1 ps

module tb_dec2to4();

reg [1:0]x;

reg en;

wire y;

dec2to4 my_dec2to4(.W(x),.En(en),.Y(y));

initial

begin

x=2’b00;

#10 x=2’b01;

#10 x=2’b10;

#10 x=2’b11;

#20 $stop;

end

initial

en=0;

always #5 en = ~en;

116

实验四第二次博客记录Verilog(第二版)数字系统设计与仿真十一章实验4任务与函数的设计

一,实验目的:

(1)掌握任务的设计和调用方法

(2)掌握函数的 设计和调用方法

(3)进一步熟悉和掌握行为级语法

二,实验涉及语法

(1)第五章中任务的定义方法和调用方法

(2)第五章中函数的定义方法和调用方法

(3)第四章中行为级语法中部分语句

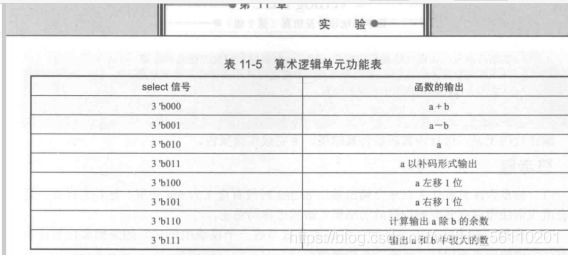

三,实验内容:参照书上的代码完成一个算术逻辑单元的建模和任务建模。

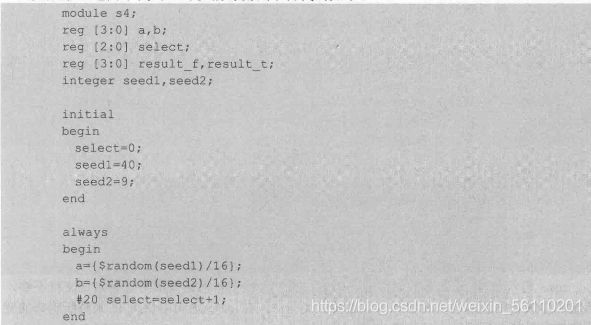

在编写测试模块时,为了使输出的结果更利于观察,把select信号设置为依次加1的操作这样连续的8个信号变化就会完成所有应该执行的功能,保证所有的case分支都能执行。而a和b的值采用两个不同的随机数产生,使数据具有一般性。输出端口中result_f表示函数的输出,result_t表示任务的输出

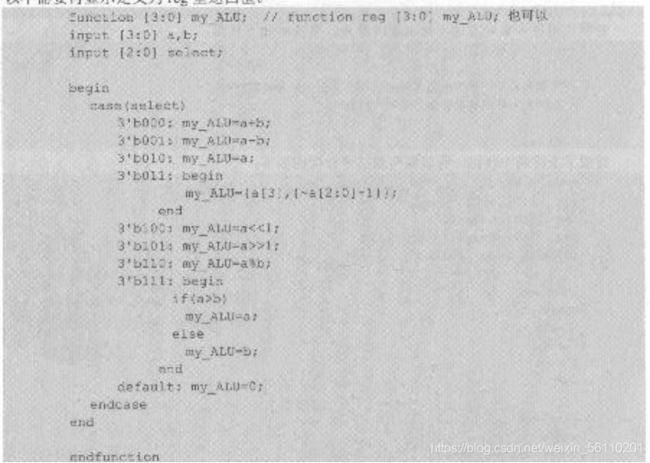

先采用函数的方式来完成设计,定义送入计算的a和b数据是4位值,计算的结果也保留4位值,按照如下的方式来声明此函数形式。

根据给出的功能表,结合函数的基本语法,可以得到如下参考代码,该函数的返回值

是4位的,所以在函数声明时一定要声明为[3:0]形式。由于默认的数据类型就是reg型,所以不需要再显示定义为reg型返回值。

case语句和if语句是可以嵌套使用的,虽然–些简单的仿真器对这种语法支持不够,但绝大多数正常版本的仿真器都可以支持此类语法,在case语句中使用if来判断状态的变化情况也是状态机写法中的标准形式。

该任务代码部分与函数的功能部分基本相同,只是在定义和输入/输出信号的声明上略有区别。完成了上述两个代码,补全测试平台,参考代码如下,注意函数在调用的时候一-定要有一个赋值等式,同时不需要输出信号部分:任务在调用时不能使用赋值等式,只是直接写出任务名并排列好任务所需的输入和输出信号即可,相关内容请复习第5章的知识。

四,实验工具:modelsim软件

五、实验代码

设计模块代码

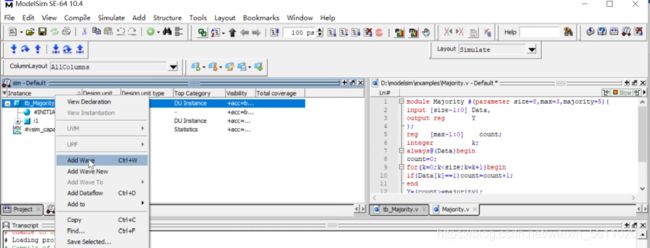

Majority

module Majority #(parameter size=8,max=3,majority=5)(

input [size-1:0] Data,

output reg Y

);

reg [max-1:0] count;

integer k;

always@(Data)begin

count=0;

for(k=0;k

end

Y=(count>=majority);

end

endmodule

测试模块代码

tb_Majority

`timescale 1 ps/ 1 ps

Majority module tb_Majority();

reg [7:0] data;

wire y;

i1 (.Data(data),.Y(y));

initial

begin

data[7:0]=8’b00000000;

#5 data[7:0]=8’b11010011;

#5 data[7:0]=8’b11010100;

#5 data[7:0]=8’b11010101;

#5 data[7:0]=8’b11010110;

#5 data[7:0]=8’b11010111;

#5 data[7:0]=8’b11011000;

#5 data[7:0]=8’b11011001;

#5 data[7:0]=8’b11011010;

#5 data[7:0]=8’b11011011;

#5 data[7:0]=8’b11011100;

#5 data[7:0]=8’b11011101;

#5 data[7:0]=8’b11011110;

#5 data[7:0]=8’b11011111;

#5 data[7:0]=8’b11100000;

#20 $stop;

end

endmodule

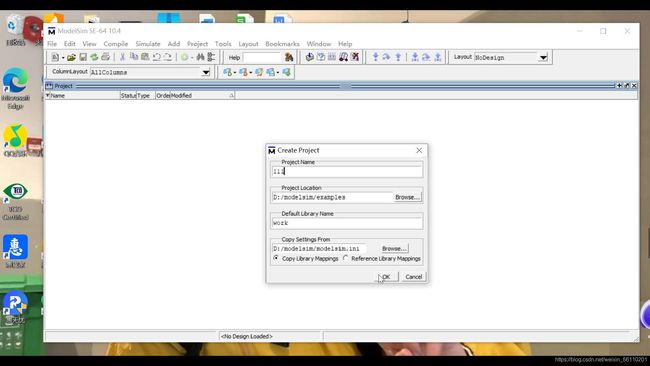

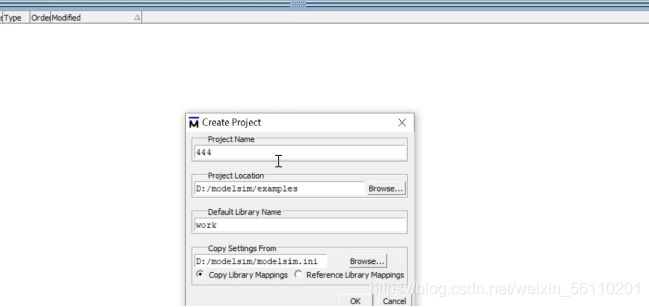

六、工程的建立: 打开Modelsim,并在project中创建一个工程,对其进行命名为444.

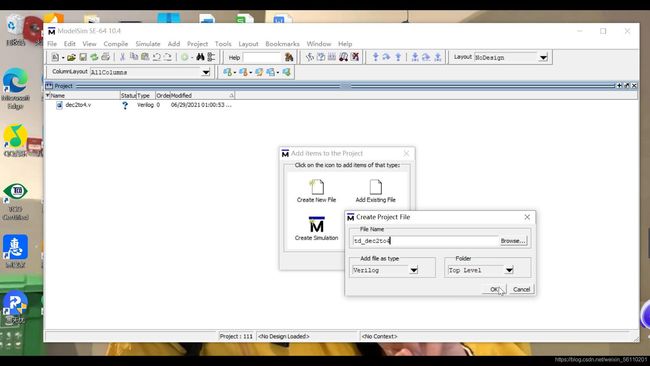

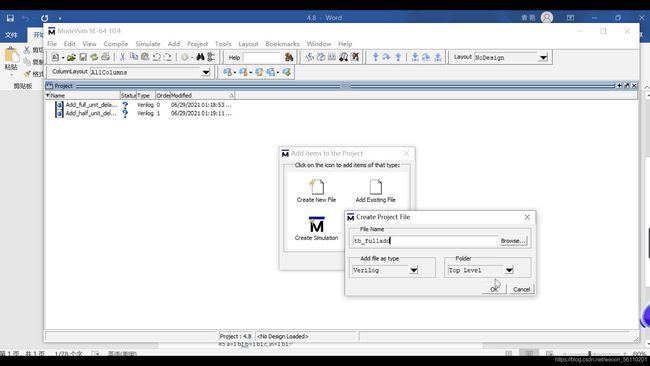

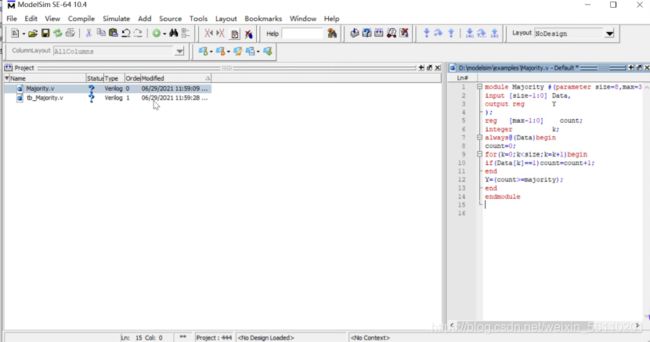

代码文件夹的创建:对于本实验我们设计了一个测试代码和实验代码,故而我们要创建两个create new file文件,并将Add file as type改为Verilog形式

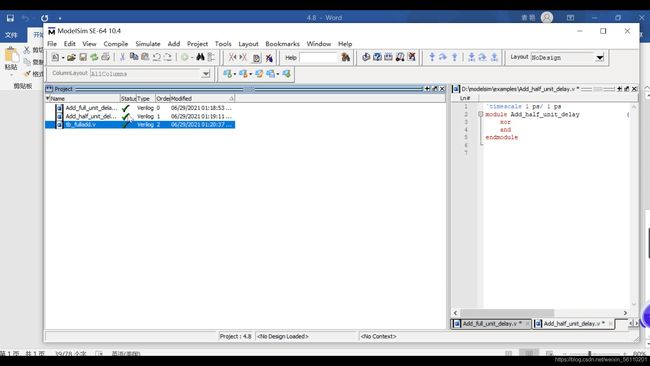

放入实验代码:实验的本体在于实验代码,实验的第三步是将我们的代码写入已经创建的文件之中

实验代码的检测:将实验代码保存后点击Compile all的图标,或者右击Compile.在其中选择Compile all对实验的代码进行检测是否有错误。

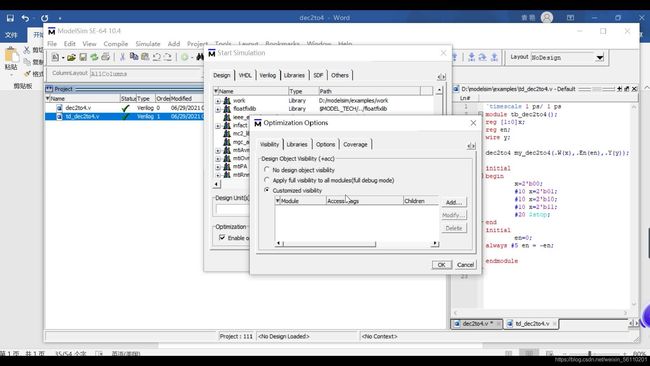

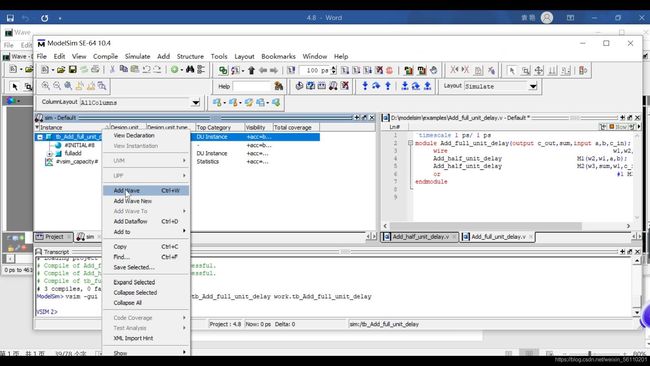

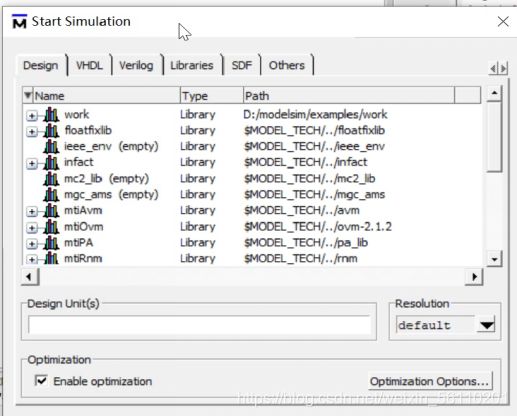

实验仿真过程:在实验代码检测成功无误以后,我们点击simulate进行仿真

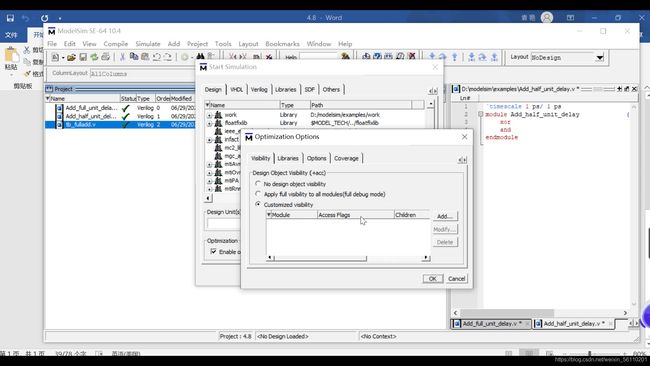

过程文件添加以及选择:

(1)点击Optimzation options…,再点击Customized visibility,add我们所要的work中的tb_Majority文件,对work工程在进行选择tb_Majority。

点击run all.得到实验的波形图

实验四

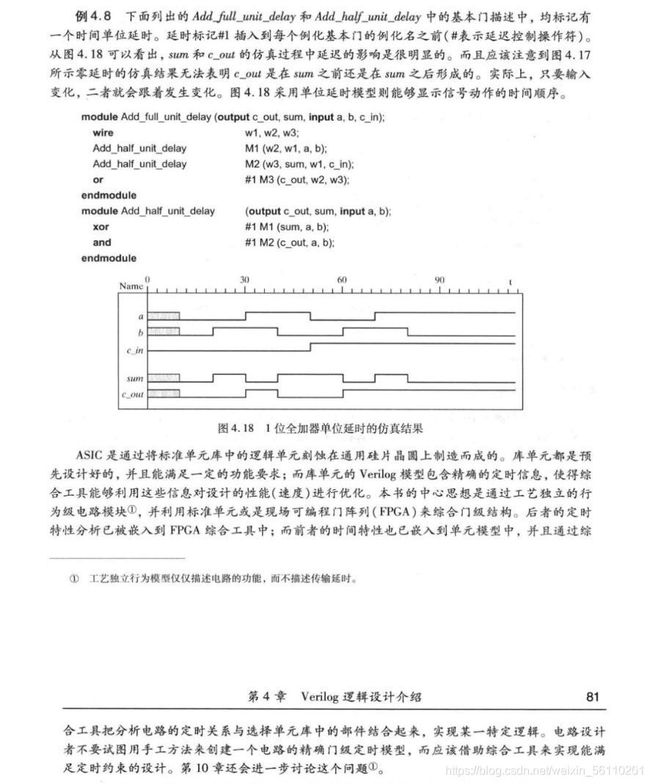

第三次博客记录Verilog HDL高级数字设计(第二版)p80页例题4.8

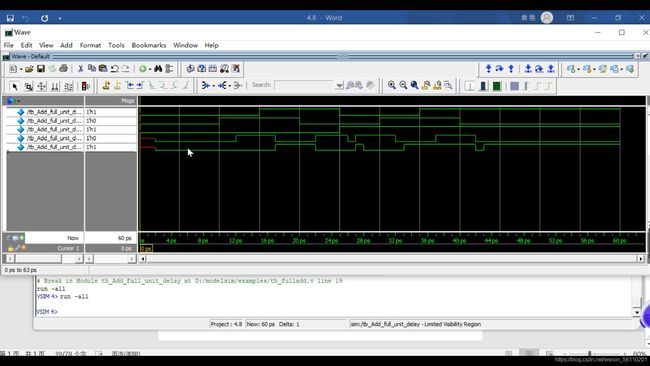

一,实验目的:采用单位延时模型显示信号动作的时间顺序

二,实验原理图:

三,实验工具:modelsim软件。

四、实验代码

Add_full_unit_delay

`timescale 1 ps/ 1 ps

module Add_full_unit_delay(output c_out,sum,input a,b,c_in);

wire w1,w2,w3;

Add_half_unit_delay M1(w2,w1,a,b);

Add_half_unit_delay M2(w3,sum,w1,c_in);

or #1 M3(c_out,w2,w3);

endmodule

Add_half_unit_delay

`timescale 1 ps/ 1 ps

module Add_half_unit_delay (output c_out,sum,input a,b);

xor #1 M1(sum,a,b);

and #1 M2(c_out,a,b);

endmodule

tb_fulladd

`timescale 1 ps/ 1 ps

module tb_Add_full_unit_delay();

reg a, b, c_in;

wire sum, c_out;

Add_full_unit_delay fulladd(.c_out(c_out),.sum(sum),.a(a),.b(b),.c_in(c_in));

initial

begin

a=1’b0;b=1’b0;c_in=1’b0;

#5 a=1’b0;b=1’b0;c_in=1’b0;

#5 a=1’b0;b=1’b1;c_in=1’b0;

#5 a=1’b1;b=1’b1;c_in=1’b0;

#5 a=1’b1;b=1’b0;c_in=1’b0;

#5 a=1’b0;b=1’b0;c_in=1’b1;

#5 a=1’b0;b=1’b1;c_in=1’b1;

#5 a=1’b1;b=1’b1;c_in=1’b1;

#5 a=1’b1;b=1’b0;c_in=1’b1;

#20 $stop;

end

endmodule

y4.8