数字逻辑---头歌实训作业---多路选择器设计与应用(Logisim)

第1关:2选1选择器设计

如有任何不解或者想要最终实验代码,可评论区喊话哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

- 本关任务:在Logisim中绘制2选1多路选择器,先在本地完成测试,体验数据选择的功能,然后在线完成测评。

相关知识

多路选择器又称数据选择器、多路开关或复用器(MUX,Multiplexer),在多路数据传送过程中,能够根据需要将其中任意一路数据选中送到输出端的电路。 2选1多路选择器电路原理图如下:

2路选择器简化真值表如下:

s |

f |

|---|---|

| 0 | w0 |

| 1 | w1 |

表达式:f=sw0+sw1 在此图基础上,利用门电路的封锁性特征构建使能信号,注意使能无效时输出的值。

引脚说明

| 信号 | I/O | 位宽 | 说明 |

|---|---|---|---|

| nEnable | 输入 | 1 位 | 使能端,低电平有效。nEnable=0时选择;nEnable=1禁止选择,此时输出恒为1。 |

| Select | 输入 | 1 位 | 地址选择(数据端口选择) |

| D1,D0 | 输入 | 1 位 | 2路数据输入 |

| F | 输出 | 1 位 | 数据输出端 |

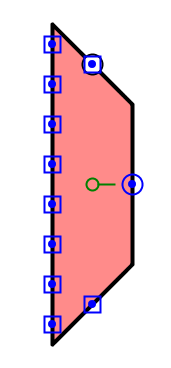

子电路外观

请勿移动引脚位置,否则无法完成测试!

实验内容

实验电路框架MUXlab.circ下载:鼠标右击右侧代码区,Download File

在Logisim中打开实验电路框架,在工程中的“2选1MUX”子电路中完成选择器的设计。

测试说明

本地实验完成后,请用记事本或者其他纯文本编辑器打开电路文件(MUXlab.circ),全选、复制,然后粘贴到Educoder代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

第2关:4选1选择器设计

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:在Logisim中利用上一关的2选1选择器级联设计一个4选1多路选择器。

相关知识

多路选择器又称数据选择器、多路开关或复用器(MUX,Multiplexer),在多路数据传送过程中,能够根据需要将其中任意一路数据选中送到输出端的电路。 4选1选择器级联扩展原理如下:

4路选择器简化真值表如下:

s1 |

s0 |

f |

|---|---|---|

| 0 | 0 | w0 |

| 0 | 1 | w1 |

| 1 | 0 | w2 |

| 1 | 1 | w3 |

表达式如下: f=s1s0w0+s1s0w1+s1s0w2+s1s0w3 =m0w0+m1w1+m2w2+m3w3=∑i=03miwi mi是选择变量s1,s0的最小项,wi是数据输入

引脚说明

| 信号 | I/O | 位宽 | 说明 |

|---|---|---|---|

| nEnable | 输入 | 1 位 | 使能端:nEnable=0时选择;nEnable=1禁止选择,此时输出恒为1。 |

| Select | 输入 | 2 位 | 地址选择 |

| D3~D0 | 输入 | 1 位 | 4路数据输入 |

| F | 输出 | 1 位 | 数据输出端 |

子电路外观

请勿移动引脚位置,否则无法完成测试!

实验内容

实验电路框架与第一关相同,在Logisim中打开实验电路框架,在“4选1MUX”子电路中完成选择器的设计。

测试说明

本地实验完成后,请用记事本或者其他纯文本编辑器打开电路文件(MUXlab.circ),全选、复制,然后粘贴到Educoder代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

第3关:8选1选择器设计

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:利用前面两关的选择器级联设计一个8选1多路选择器。

相关知识

多路选择器又称数据选择器、多路开关或复用器(MUX,Multiplexer),在多路数据传送过程中,能够根据需要将其中任意一路数据选中送到输出端的电路。 8路选择器简化真值表如下:

s2 |

s1 |

s0 |

f |

|---|---|---|---|

| 0 | 0 | 0 | w0 |

| 0 | 0 | 1 | w1 |

| 0 | 1 | 0 | w2 |

| 0 | 1 | 1 | w3 |

| 1 | 0 | 0 | w4 |

| 1 | 0 | 1 | w5 |

| 1 | 1 | 0 | w6 |

| 1 | 1 | 1 | w7 |

表达式如下: f=∑i=07miwi mi是选择变量s2,s1,s0的最小项,wi是数据输入

引脚说明

| 信号 | I/O | 位宽 | 说明 |

|---|---|---|---|

| nEnable | 输入 | 1 位 | 使能端:nEnable=0时选择;nEnable=1禁止选择,此时输出恒为1。 |

| Select | 输入 | 3 位 | 地址选择 |

| D7~D0 | 输入 | 1 位 | 8路数据输入 |

| F | 输出 | 1 位 | 数据输出端 |

子电路外观

请勿移动引脚位置,否则无法完成测试!

实验内容

实验电路框架与第一关相同,在Logisim中打开实验电路框架,在“8选1MUX”子电路中完成选择器的设计。

测试说明

本地实验完成后,请用记事本或者其他纯文本编辑器打开电路文件(MUXlab.circ),全选、复制,然后粘贴到Educoder代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

第4关:多路选择器的应用

如有任何不解或者想要答案代码,可在评论区喊话我哦,希望我的答案对你有帮助,点个关注再走吧,感谢!!!

本关卡最终答案:

任务描述

本关任务:在Logisim中选择在前面关卡中设计的多路选择器进行组合逻辑设计,设计全加器FA。

相关知识

对于2n路选择器,表达式如下: f=∑i=02n−1miwi mi是选择变量sn−1…s0的最小项,wi是数据输入

真值表变换

原理:将待实现函数的真值表变换成对应多路选择器的简化真值表形态即可! 例如:用4选1MUX实现3输入择多函数f(w1,w2,w3)=Σm(3,5,6,7)

用4选1MUX实现如下:

w1,w2作为选择变量s1,s0,将0、w3、w3和1分别接入0号、1号、2号和3号数据端口。注意函数变量与选择变量的对应顺序!! 若用8选1MUX实现3输入函数,则真值表无需做任何变换! 此时,w1,w2,⋯,w8作为选择变量s7,s6,⋯,s0,将8个函数值分别送入对应数据端口。

香农展开(1变量展开)

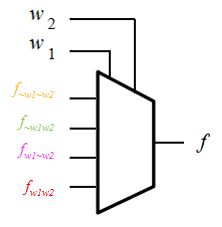

任何n变量函数f(w1,w2,⋯,wn)可以对w1展开表示为: f=w1⋅f(0,w2,⋯,wn)+w1⋅f(1,w2,⋯,wn) =w1⋅fw1+w1⋅fw1 对任意wi展开都有效! 此时可以用2选1MUX实现该函数,如图所示:

w1作为选择变量s,将fw1和fw1的逻辑实现分别接入0号和1号数据端口。

香农展开(2变量展开)

任何n变量函数f(w1,w2,w3,⋯,wn)可以对w1,w2展开表示为: f=w1w2⋅f(0,0,w3,⋯,wn)+w1w2⋅f(0,1,w3,⋯,wn) +w1w2⋅f(1,0,w3,⋯,wn)+w1w2⋅f(1,1,w3,⋯,wn) =w1w2⋅fw1w2+w1w2⋅fw1w2+w1w2⋅fw1w2+w1w2⋅fw1w2 对任意wi,wj(i=j)展开都有效! 此时可以用4选1MUX实现该函数,如图所示:

w1,w2作为选择变量s1,s0,将fw1w2、fw1w2、fw1w2和fw1w2的逻辑实现分别接入0号、1号、2号和3号数据端口。 依此类推,可以对任意的k个变量展开(k≤n),然后用2k选1MUX实现该函数!当k=n时,展开式为函数的正则SOP式(标准与或式)。

引脚说明

| 信号 | I/O | 位宽 | 说明 |

|---|---|---|---|

| nEnable | 输入 | 1位 | 使能端:nEnable=0时做加法;nEnable=1禁止相加,此时输出恒为1。 |

| A,B,Ci | 输入 | 1位 | 三个相加数 |

| Co,Sum | 输出 | 1位 | 进位输出、和输出 |

子电路外观

请勿移动引脚位置,否则无法完成测试!

实验内容

实验电路框架与第一关相同,在Logisim中打开实验电路框架,在“MUX应用”子电路中完成全加器的设计。

测试说明

本地实验完成后,请用记事本或者其他纯文本编辑器打开电路文件(MUXlab.circ),全选、复制,然后粘贴到Educoder代码窗口中,点击右下方的“评测”按钮,平台会对你的代码进行测试。

拓展设计建议

在本地利用MUX完成不同变量数的更多函数的电路设计实现。