学习日记——FPGA实验平台板级电路详解

一、板级电路整体架构

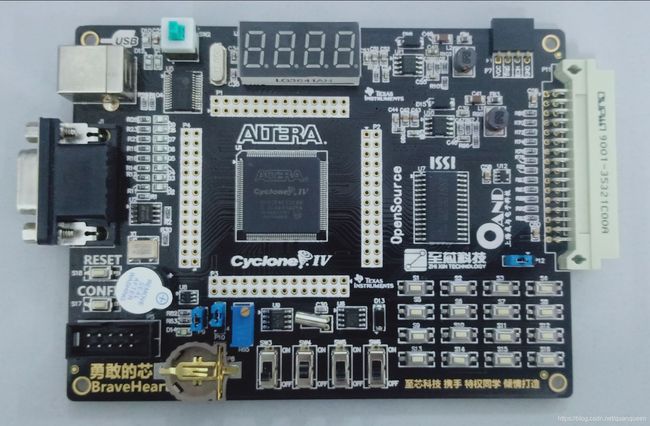

我接下来一段时间学习的就是“勇敢的芯”FPGA 实验平台,它是特权同学和至芯科技携手打造的一款基于Altera Cyclone IV FPGA 器件的入门级 FPGA 学习平台

FPGA 实验板实物图如图所示

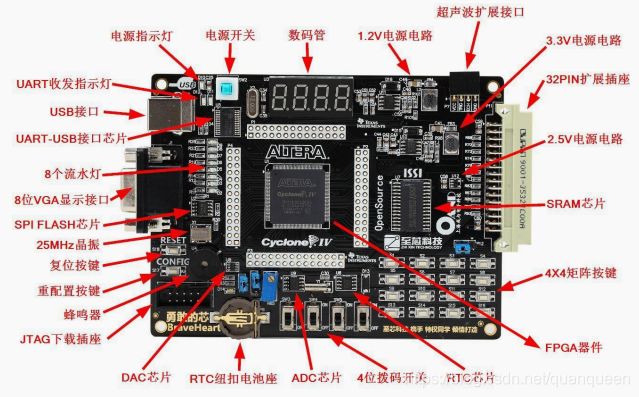

这是整板的外设器件的示意图。

FPGA 实验板接口芯片连接如图所示

FPGA 实验板接口芯片连接如图所示

二、电源电路

与任何电子元器件一样,FPGA 器件需要有电源电压的供应才能工作。尤其对于规模较

大的器件,其功耗也相对较高,其供电系统的好坏将直接影响到整个开发系统的稳定性。所以,设计出高效率、高性能的 FPGA 供电系统具有极其重要的意义。

不同的 FPGA 器件、不同的应用方式会有不同的电压电流的需求。

简单的归纳,可以将 FPGA 器件的电压需求分为三类:核心电压、I/O 电压和辅助电压。

(1)核心电压:是 FPGA 内部各种逻辑电路正常工作运行所需要的基本电压,该电压用于保证FPGA 器件本身的工作。通常选定某一款 FPGA 器件,其核心电压一般也都是一个固定值,不会因为电路的不同应用而改变。核心电压值可以从官方提供的器件手册中找到。

(2)I/O 电压:顾名思义便是 FPGA 的 I/O 引脚工作所需的参考电压。在引脚排布上,FPGA 与ASIC 最大的不同,便是 FPGA 所有的可用信号引脚基本都可以作为普通 I/O 使用,其电平值的高低完全由器件内部的逻辑决定。当然了,它的高低电平标准也受限于所供给的 I/O 电压。任何一片 FPGA 器件,它的 I/O 引脚通常会根据排布位置分为多个 bank。同一个 bank 内的所有 I/O 引脚所供给的 I/O 电压是共用的,可以给不同的 bank 提供不同的 I/O 电压,它们彼此是不连通的。因此,不同 bank 的不同 I/O 电压为 FPGA 器件的不同接口应用提供了灵活性。这里举一个例子,Cyclone IV 系列器件的某些 bank 支持 LVDS 差分电平标准,此时器件手册会要求设计者给用于 LVDS 差分应用的 bank 的 I/O 电压供 2.5V 电压,这就不同于一般的 LVTTL 或 LVCOMS 的 3.3V 供电需求。而一旦这些用于 LVDS 传输的 I/O bank 电压供给为2.5V,那么它就不能作为 3.3V 或其他电平值标准传输使用了。

(3)辅助电压:除了前面提到的核心电压和 I/O 电压,FPGA 器件工作所需的其它电压我们通常都称为辅助电压。例如 FPGA 器件下载配置所需的电压,当然了,这里的辅助电压值可能与核心电压值或 I/O 电压值是一致的。很多 FPGA 的 PLL 功能块的供电会有特殊要求,也可以认为是辅助电压。由于 PLL 本身是模拟电路,而 FPGA 其他部分的电路基本是数字电路,因此 PLL的输入电源电压也很有讲究,需要专门的电容电路做滤波处理,而它的电压值一般和I/O电压值不同。此外,例如 Cyclone V GX 系列 FPGA 器件带高速 Gbit 串行收发器,通常有额外的参考电压;MAX10 系列器件的 ADC 功能引脚电路也需要额外的参考电压;一些带 DDR3控制器功能的 FPGA 引脚上通常也有专门的参考电压……诸如此类的参考电压我们都可以归类为 FPGA 的辅助供电电压,在实际电源电路连接和设计过程中,都必须予以考虑。

在 LDO 稳压器、DC/DC 芯片或电源模块的选择上,一般遵循以下原则:

● 电流低于 100mA 的电压可以考虑使用 LDO 稳压器产生,因为电路简单、使用元器件少、PCB 面积占用小,且成本也相对低廉。

● 对电源电压的纹波极为敏感的供电考虑使用 LDO,如 CMOS Sensor 的模拟供电电压、ADC 芯片的参考电压等。

● 除了上述情况,一般电流较大、对电源电压纹波要求不高的情况,都尽量考虑使用DC/DC 电路,毕竟它能够提供大电流供电,且提供最好的电源转换效率。

● 对于电源模块,笔者见到最多的是军工等成本不敏感、板级 PCB 空间较大的应用中使用,它其实是 LDO 稳压器和 DC/DC 电路优势的整合。

通常而言,对于 FPGA 器件的电源方案的选择以及电源电路的设计,一定要事先做好前期的准备工作,如以下几点是必须考虑的:

● 器件需要供给几档电压,压值分别是多少?

● 不同电压档的最大电流要求是多少?

● 不同电压档是否有上电顺序要求?(大部分的 FPGA 器件是没有此项要求的)

● 电源去耦电容该如何分配和排布?

● 电源电压是否需要设计特殊的去耦电路?

-

说到电源,也不能不提一下地端(GND)电路的设计,FPGA 器件的地信号通常是和电压配对的。一般应用中,统一共地连接是没有问题的,但也需要注意特殊应用中是否有隔离要求。FPGA器件的引脚引出的地信号之间通常是导通的,当然也不能排除有例外的情况。如果漏接个别地信号,器件通常也能正常工作,但是笔者也遇到过一些特殊的状况,如Altera的 Cyclone III 器件底部的中央有个接地焊盘,如果设计中忽略了这个接地信号,那么FPGA很可能就不干活了,因为这个地信号是连接 FPGA 内部的很多中间信号的地端,它并不和FPGA的其它地信号直接导通。因此,在设计中也一定要留意地信号的连接,电源电路的任何小疏忽都有可能导致器件的罢工。

-

在我们所设计的这个实验平台上,如电源电路示意图所示,由 PC 的 USB 端口进行供电,通常可以提供 5V/0.5A 的电压和电流。5V电压输入到两个 DC/DC 电路分别产生 3.3V 和 1.2V 的电压,DC/DC 芯片支持的最大电流可以达到 3A,当然我们的FPGA 器件实际上根本不需要这么大的电流。之所以采用 DC/DC 电路产生 3.3V 和 1.2V 电压,是考虑到 3.3V 是FPGA 的 I/O电压,也是板上大多数外设的供电电压,它的电流相对较大;而 1.2V 是 FPGA器件的核电压,电流也较大;因此,它们使用 DC/DC 电路更合适,既可以保证较大电流需求,也能够实现更好的电源转换效率。而 2.5V电压使用 3.3V 转 2.5V 的 LDO 电路,是由于 2.5V 仅仅只是 FPGA的下载配置电路使用,电流相对较小,它对转换效率要求也不高,使用简单的 LDO 电路来得 更“经济实惠”一些。

三、复位与时钟电路

1、关于 FPGA 器件的时钟

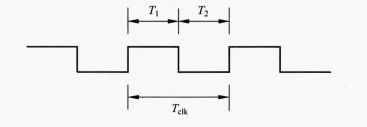

- 以上为理想的时钟波形,它是一个占空比为 50%且周期固定的方波。 Tclk为一个时 钟周期,T1为高脉冲宽度,T2为低脉冲宽度,Tclk = T1+T2。一般情况下,FPGA 器件内部的 逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个时钟周期完成,便可以切割成几个耗时较小的运算,然后在数个时钟上升沿后输出最终的运算结果。时钟信号的引入,不仅让所有的数字运算过程变成“可量化”的,而且也能够将各种不相关的操作过程同步到一个节拍上协同工作。

关于时钟电路的设计和选型,有如下几个基本事项需要考虑:

● 系统运行的时钟频率是多少?(可能有多个时钟)

● 是否有内部的时钟管理单元可用(通常是有)?它的输入频率范围(需要查看器件手册进行确认)?

● 尽可能选择专用的时钟输入引脚。

关于 FPGA 时钟电路的 PCB Layout 设计,通常需要遵循以下的原则。

● 时钟晶振源应该尽可能放在与其连接的 FPGA 时钟专用引脚的临近位置。 ● 时钟线尽可能走直线。如果无法避免转弯走线,使用 45 度线,尽量避免 T 型走线

和直角走线。

● 不用同时在多个信号层走时钟线。

● 时钟走线不要使用过孔,因为过孔会导致阻抗变化及反射。

● 靠近外层的地层能够最小化噪声。如果使用内层走时钟线,要有良好的参考平面,且走带状线。

● 时钟信号应该有终端匹配电路,以最小化反射。

● 尽可能使用点到点的时钟走线。

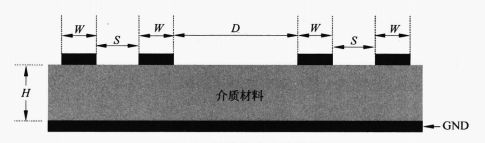

● 如时钟差分对的间隔图所示,对于时钟差分对的走线,必须严格按照 D>2S 规则,以最小化相邻差分对间的串扰。

● 确保整个差分对在整个走线过程中的线间距恒定。

● 确保差分对的走线等长,以最小化偏斜和相移。

● 同一网络走线过程中避免使用多个过孔,以确保阻抗匹配和更低的感抗。

● 高频的时钟和 USB 差分信号对走线尽可能短。

● 高频时钟或周期性信号尽可能远离高速差分对以及任何引出的连接器(例如 I/O 连接器、控制和数据连接器或电源连接器)。

● 应当保证所有走线有持续的地和电源参考平面。

● 为了最小化串扰,尽量缩短高频时钟或周期性信号与高速信号并行走线的长度。推荐的最小间距是 3 倍的时钟信号与最近参考面间距。

● 当一个时钟驱动多个负载时,使用低阻抗传输线以确保信号通过传输线。

● 信号换层时使用回路过孔。

● 同步时钟的延时应该与数据相匹配。确保时钟与同步数据总线在同一层走线,以最小化不同层之间的传输速率差异。

2、关于 FPGA 器件的复位

- FPGA 器件在上电后都需要有一个确定的初始状态,以保证器件内部逻辑快速进入正常 的工作状态。因此,FPGA器件外部通常会引入一个用于内部复位的输入信号,这个信号称 之为复位信号。对于低电平有效的复位信号,当它的电平为低电平时,系统处于复位状态;当它从低电平变为高电平时,则系统撤销复位,进入正常工作状态。由于在复位状态期间,各个寄存器都赋予输出信号一个固定的电平状态,因此在随后进入正常工作状态后,系统便拥有了所期望的初始状态。

- 复位电路的设计也很有讲究,一般的设计是期望系统的复位状态能够在上电进入稳定工

作状态后多保持一点时间。因此,阻容复位电路可以胜任一般的应用;而需要得到更稳定可靠的复位信号,则可以选择一些专用的复位芯片。复位信号和 FPGA 器件的连接也有讲究,通常也会有专用的复位输入引脚。至于上电复位延时的长短,也是很有讲究的。因为 FPGA 器件是基于 RAM 结构的,它通常需要一颗用于配置的外部 ROM 或 Flash 进行上电加载,在系统上电稳定后,FPGA 器件首先需要足够的时间用于配置加载操作,只有在这个过程结束之后,FPGA 器件才能够进入正常的用户运行模式。而上电复位延时过短,等同于 FPGA 器件根本就没有复位过程;当然了,如果上电复位延时过长,那么对系统性能甚至用户体验都会有不通程度的影响。

设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于 FPGA 器件的复位电路,我们也需要注意以下几个要点:

● 尽可能使用 FPGA 的专用时钟或复位引脚。

● 上电复位时间的长短需要做好考量。

● 确保系统正常运行过程中复位信号不会误动作。

四、实验平台电路解析

- FPGA 的时钟输入都有专用引脚,通过这些专用引脚输入的时钟信号,在 FPGA 内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是 FPGA 内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA 的时钟和复位通常 是需要走全局时钟网络的。

- 如图所示,25MHz 的有源晶振和阻容复位电路产生的时钟信号和复位信号分别连接到 FPGA 的专用时钟输入引脚 CLK_0 和 CLK_1上。

如下图所示,我们所使用的 FPGA 器件共有 8 个专用时钟输入引脚,在不做时钟输入引脚功能使用时,这些引脚也可以作为普通 I/O 引脚。如我们的电路中,只使用了 CLK_0 和 CLK_1 作为专用时钟引脚功能,其他 6 个引脚则作为普通的 I/O 引脚功能。

如下图所示,我们所使用的 FPGA 器件共有 8 个专用时钟输入引脚,在不做时钟输入引脚功能使用时,这些引脚也可以作为普通 I/O 引脚。如我们的电路中,只使用了 CLK_0 和 CLK_1 作为专用时钟引脚功能,其他 6 个引脚则作为普通的 I/O 引脚功能。

FPGA 上电复位时间需要大于 FPGA 器件启动后的配置加载时间,这样才能够确保 FPGA

运行后的复位初始化过程有效。

五、 FPGA 下载配置电路

- 板级设计需要注意的几个方面:

● 配置芯片尽量靠近 FPGA。

● 考虑配置信号的完整性问题,必要时增加阻抗匹配电阻。

● 部分配置引脚可以被复用,但是要谨慎使用,以免影响器件的上电配置过程。

FPGA 配置电路的设计是非常重要的,相关信号引脚通常都是固定并且专用的,需要参

考官方推荐电路进行连接。

- 如图上所示,这是 FPGA 下载和配置的示意图。在图的左侧,DC10 插座将 FPGA 器件的 JTAG 专用引脚TCK、TMS、TDI、TDO 引出,通过 USB-Blaster 下载器可以连接这个 DC10 插座和 PC 机,实现从 PC 机的Quartus II 软件到 FPGA 器件的在线烧录或配置芯片(SPI FLASH)的固化。而在图 2.12 的右侧,一颗 SPI FLASH 作为 FPGA 器件的配置芯片,FPGA 器 件的固化代码可以存储在这颗 SPI FLASH 中,当 FPGA器件每次上电时,都会直接从 SPI FLASH 中读取固化代码并运行。

- 为了实现上述图的配置电路正常工作,我们还需要如图下所示,将MSEL0/MSEL1/MSEL2 引脚分别连接到 GND/2.5V/GND,这是设定 FPGA 器件在上电后直接进入AS 配置模式,即从 SPI FLASH 的固化代码启动运行。需要额外说明的是,无论

MSEL0/MSEL1/MSEL2 引脚如何设置,当 JTAG 在线配置 FPGA 时,FPGA 器件都会优先运行 JTAG最新烧录的代码。CONF_DONE\nCONFIG\nSTATUS 三个信号则分别上拉到 3.3V,同时 nCONFIG连接按键 S17,可以通过这个按键使 FPGA 器件重新加载配置代码。

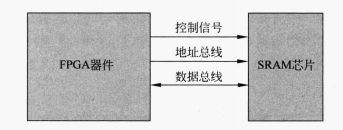

六、SRAM 接口电路

如图上图所示,FPGA 与 SRAM 芯片的连接主要是控制信号、地址总线和数据总线。

七、AD/DA 芯片电路

- 如图所示,FPGA 通过一组 IIC 总线连接到 DA 芯片,使其输出一个特定的模拟电压,该模拟电压既可以通过跳线帽选择输出到 LED上(可观察 LED 的亮暗,直观的感受到 AD 芯片),也可以通过跳线帽输出到 AD 芯片的模拟输入端口。AD 芯片模拟输入端口的跳线帽除了可以选择输入 DA 芯片的模拟输出电压,也可以选择输入可调电阻的分压信号。FPGA 通过一组类似 SPI 总线的接口实现 AD芯片的数据读取操作。

- 上图是FPGA 与 AD/DA 芯片连接示意图AD/DA 芯片的跳线帽和可调电阻器如图所示。DA 芯片的跳线帽若短路(即 P9的 PIN1 和 PIN2 短路),则 DA 芯片输出电压值将驱动 LED 指示灯状态。AD 芯片的跳线帽若短路 图示下面两个引脚(P10的 PIN1 和 PIN2),则滑动变阻器分压值将作为 AD 芯片的输入;AD 芯片的跳线帽若短路图示上面两个引脚(P10 的 PIN2和 PIN3),则 DA 芯片的输出电压值将 作为 AD 芯片的输入。滑动变阻器上金属小旋钮可以对 3.3V 的电压进行分压,产生的分压值可以输入到 AD 芯片进行实验。

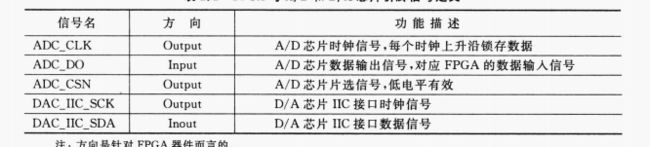

如表所示,这是 FPGA 与 AD/DA 芯片的引脚信号定义。

八、UART 接口电路

- FPGA 与 UART 外设连接如图所示。FPGA 器件通过 UART 转 USB 芯片 PL2303 将标准 的 UART 协议转换为USB 协议,在 PC 端安装驱动后,便是一个虚拟串口实现 UART 的传输。

如表所示,这是 FPGA 与 UART 转 USB 芯片的引脚信号定义。

九、RTC 接口电路

FPGA 与 RTC 外设连接如图所示。RTC 芯片 PCF8563T 外接纽扣电池,在板子本身不

供电时提供电源,而 FPGA 与 RTC 芯片之间通过 IIC 总线进行数据交互。

- RTC 芯片的电路如下图所示,我们重点关注 RTC 芯片的供电,即 U6-8PIN 的连接。 VCC_RTC 为纽扣电池的供电,VCC3.3 为板子外部电源产生的 3.3V 电压。在板子不外接电源 时,即 VCC3.3 不供电时,二极管 SS14截止,这样 VCC_RTC 只给 RTC 芯片供电,而连通 VCC3.3 对板子的其他外设供电;而板子供电时,二极管 SS14导通,VCC3.3 和 VCC_RTC 电源之间有 200K 电阻 R36 隔离,一般纽扣电池电压不会高于 3V,因此 RTC 芯片主要由VCC3.3 供电。这 里的 200K 电阻 R36 也对纽扣电池供电起到限流的作用,RTC 芯片不通信时的电流非常小。

十、 4X4 矩阵按键电路

FPGA 与 4X4 矩阵按键的连接如图所示。矩阵按键的横、纵方向各 4 个信号连接到

FPGA 引脚,FPGA 可以通过给横方向 4 个信号输出电平,采集纵方向 4 个信号的输入电平,从而得到具体触发按下的键位。

这个 P12 插座可以用于控制矩阵按键的 S1、S2、S3、S4 工作于矩阵按

键模式或者独立按键模式。如图示 PIN2-3 短接时,为矩阵按键模式;而 PIN1-2 短接时,为独立按键模式。

上表为 FPGA 与 4X4 矩阵按键的引脚信号定义

上表为 FPGA 与 4X4 矩阵按键的引脚信号定义

十一、VGA 显示接口电路

FPGA 与 VGA 外设连接如图所示。这个 VGA 驱动显示色彩通过 3 个信号,即 R、G、 B 信号进行设定,实现 8 色的显示效果。场同步 VSY 信号和行同步 HSY 信号也都由 FPGA 引脚输出产生。

如表所示,这是 FPGA 与 VGA 插座的引脚信号定义。

十二、蜂鸣器、数码管、流水灯、拨码开关电路

- FPGA 与蜂鸣器、流水灯、数码管、拨码开关连接如图所示。蜂鸣器单个引脚控制 高点电平驱动即可;8 个 FPGA 引脚分别连接8 个 LED 指示灯,用于流水灯实验;数码管由 4 个位选信号和 8 个段选信号驱动;4 个拨码开关则连接到 FPGA引脚作为输入信号。

如表所示,这是 FPGA 与蜂鸣器、流水灯、数码管、拨码开关的引脚信号定义。

十三、超声波接口、外扩 LCD 接口电路

- FPGA 与 LCD、超声波模块连接扩展如图所示。超声波模块只有 2 个信号,即驱动 脉冲信号 TRIG 和回响脉冲信号 ECHO。LCD接口则由数据信号 LCD_RGB[15:0]、场同步信号LCD_VSY、行同步信号 LCD_HSY、时钟同步信号 LCD_CLK 组成。