Verilog语言控制Xilinx FPGA引脚demo

鉴于精力有限,虽然博主本科专业涉及到了一些硬件方面知识,但时间已经久远,所以博客的内容仅限于扫盲用,记录一下过程吧:

博主这边从Xilinx着手了解,一些信息可以从官网获取。Xilinx在2020年被AMD收购。

这款开发板上的FPGA芯片的信息介绍可从官网获取到

https://www.xilinx.com/products/silicon-devices/fpga/artix-7.html#productTable

其主流几款系列的介绍可见如下博客

xilinx 产品系列 - 知乎

什么是SOC芯片? - 知乎

另个一大原厂品牌就是Altera,2015年被英特尔收购。

ARM和FPGA之间的通信(硬件原理图篇)_illusionistyy的博客-CSDN博客_arm fpga

FPGA与DSP/ARM通信方式详解_programmer-guan的博客-CSDN博客_arm fpga 通信

博主又抽时间大概翻了翻数电

不翻还好,翻下后,感概颇多,看到了熟悉的逻辑函数,真值表示法,逻辑表达式,逻辑图,波形图,卡诺图表示法,逻辑函数中的最小项,CMOS构成的非门,与非门、或非门、异或门等功能电路,CMOS漏极开路门,三态输出门电路,组合逻辑电路的分析(输出只与输入有关系),明确逻辑功能,写真值表,写出逻辑表达式,SR锁存器,D锁存器,D触发器、JK触发器、T触发器,SR触发器,了解各触发器的特性表,后面最为重要的时序逻辑电路(除了输入之外,还和上一次状态相关),相关的逻辑方程组,状态表,状态图,时序图的表达,逻辑方程组求解中的一些步骤(输出方程组、激励方程组、状态方程组),然后常用的74HC/HCT374寄存器的逻辑图,一些典型的集成电路,如74LVC161的功能表,包括后面的555电路,这边只能到这种程度了,知道下数字电路实现的方式,以及如何去了解分析它的逻辑功能。毕竟计算机世界是由0和1构成的,还是得知道下如何靠数字电路去实现0和1的功能的。这本书里其实也介绍了verilog语法和FPGA,当年在校时并没有深入去探究,读研和毕业工作后,路也越走越偏,渐渐往软件和算法方向去了,现在基本也接触不到了,还是很可惜的,虽然现在还是挺感兴趣的,无奈时间精力有限。但博主硬件方面大概的原理还是了解的,后续不会生计奔波了,也许会再当兴趣爱好整整!

1.下载安装VIVADO

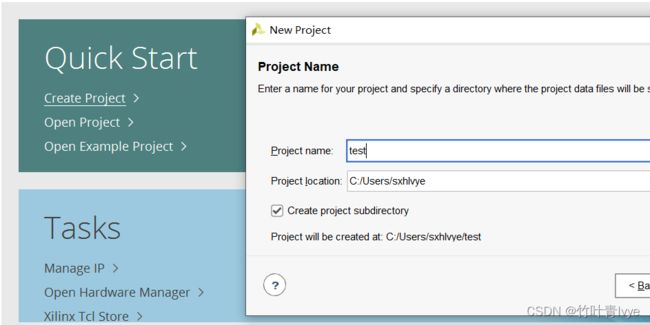

2.在Quick Start栏选择Create Project

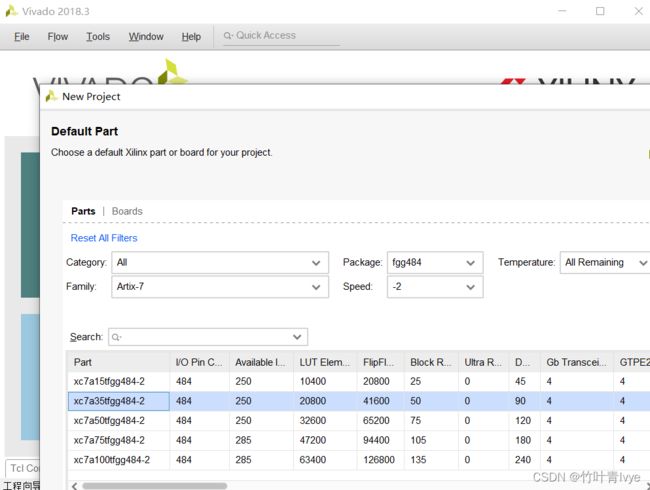

3. 如下界面参见自己所用开发板配置

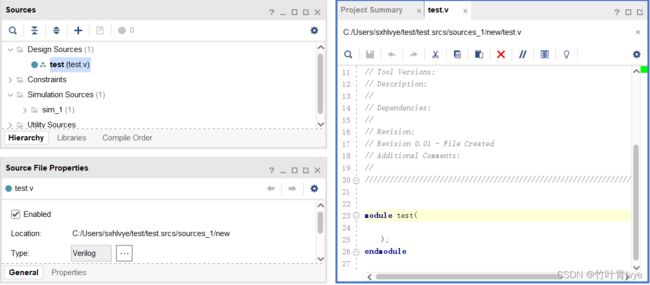

4.完毕后进入主界面

5.添加一个sources

6.创建一个文件

7.接下来开始编辑test.v

8.简单的实现一个与功能

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/04/01 21:52:08

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

//function: a&b

// 0 0 0 ;0 1 0 ;0 0 0; 1 1 1

module test(

a,

b,

out

);

input a;

input b;

output out;

assign out = a & b;

endmodule

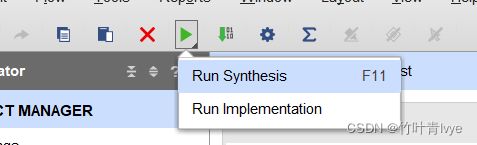

9.完毕后,点击Run Synthesis

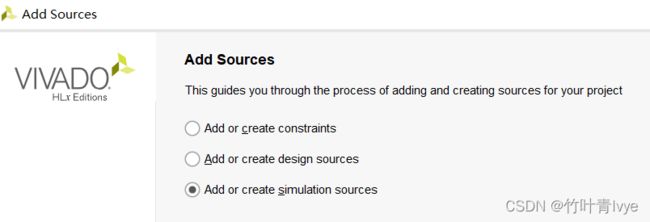

10.完毕后,再次Add sources(仿真文件)

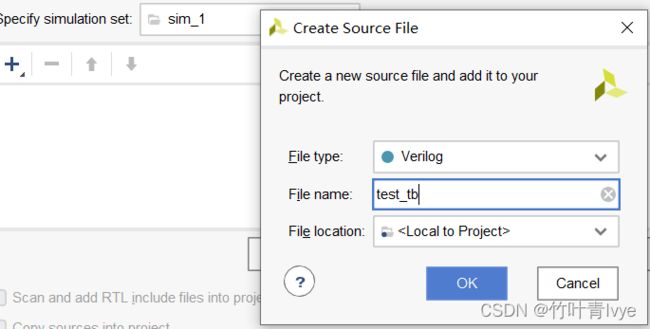

11.这边取名为test_tb

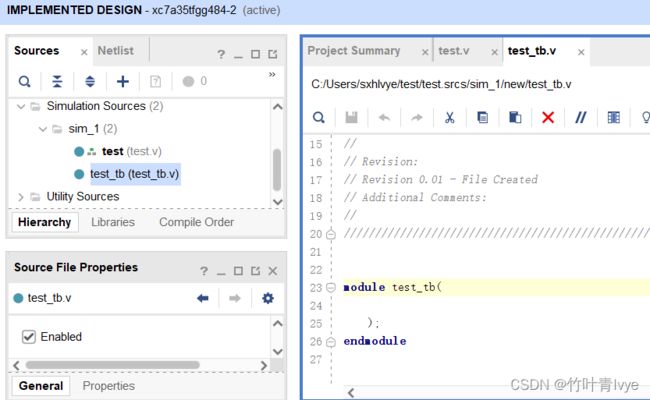

12.打开生成的text_tb文件

13.文件中内容如下:

`timescale 1ns / 1ns

//

// Company:

// Engineer:

//

// Create Date: 2022/04/01 22:18:49

// Design Name:

// Module Name: test_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test_tb();

reg s_a;

reg s_b;

wire out;

test test_inst0(

.a(s_a),

.b(s_b),

.out(out)

);

initial begin

s_a=0;s_b=0;

#200;

s_a=0;s_b=1;

#200;

s_a=1;s_b=0;

#200

s_a=1;s_b=1;

end

endmodule

14.完毕后点击如下按钮进行仿真

15.查看仿真生成的时序图,结果是对的

16.接下来点击Run Implementation,等待处理完毕

17. 再选择时序仿真,可以查看时序波形图

18.点击Open Implemented Design,可看到

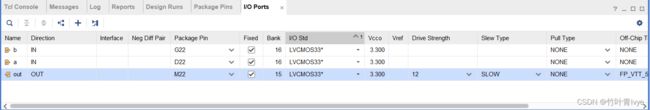

19.菜单栏选择I/O Planning

引脚分配如下:

完毕后保存下,可以查看一些相关信息

20.创建Bitstream

21.打开Open Hardware Manager, 连接上FPGA开发板

22.如下将程序下载到板子上去跑跑看

23.观察板子情况,可以看到两个开关朝上拨,即两个变量都为1时,led亮了

如上一个简单的通过verilog语言控制FPGA的demo就结束了,鉴于精力有限,博主后面不会再深入研究,只是扫扫盲。