Hexagon_V65_Programmers_Reference_Manual(16)

Hexagon_V65_Programmers_Reference_Manual(16)

- 11 指令集

-

- 11.1 概览

- 11.2 指令类别

-

- 11.1 ALU32

-

- 11.1.1 ALU32/ALU

-

- 添加

- 逻辑运算

- 取消

- Nop

- 减

- 标志延伸

- 立即转移

- 转移寄存器

- 矢量加半字

- 向量平均半字

- 矢量减法半字

- 零延伸

11 指令集

11.1 概览

本章介绍Hexagon处理器版本6的指令集。

指令在指令类别中按字母顺序列出。以下为每个指令提供信息:

-

指令名

-

说明的简要说明

-

高级功能描述(语法和行为),包括所有可能的操作数类型

-

用于分组指令的指令类和时隙信息

-

关于杂项问题的说明

-

提供对指令访问的任何C内部函数

-

指令编码

11.2 指令类别

■ ALU32 — 32 位 ALU 运算

- ❒ ALU — 算术和逻辑

- ❒ 烫发——置换

- ❒ PRED — 谓词

■ CR — 控制寄存器,循环

■ JR——从寄存器跳转

■ J — 跳跃

■ LD — 负载

■ MEMOP — 内存操作

■ NV——新价值操作

- ❒ J — 新值跳跃

- ❒ ST — 新价值商店

■ ST — 存储操作

■ 系统

❒ 用户说明

■ XTYPE — 32 位和 64 位操作

❒ ALU — 算术和逻辑

❒ BIT — 位

❒ 复杂 — 复杂

❒ FP — 浮点数

❒ MPY — 相乘

❒ 烫发——置换

❒ PRED — 谓词

❒ 移位 — 移位

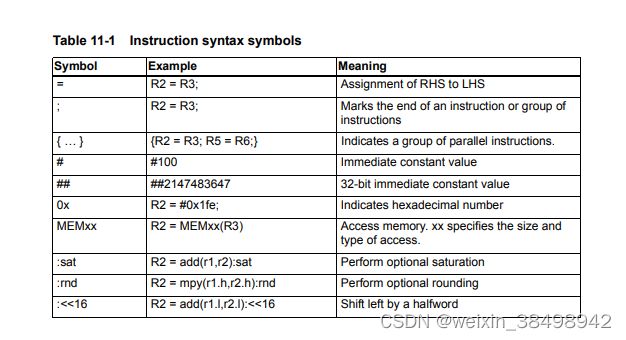

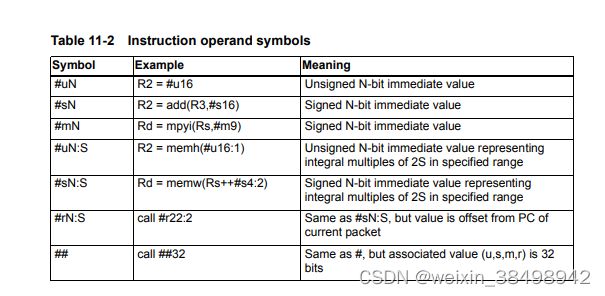

表11-2列出了用于指定指令操作数的符号。

当指令包含多个立即数操作数时,操作数符号为以大写和小写(例如#uN和35un)指定,以指示它们在指令编码。

使用C语言的超集指定指令行为。表11-3清单C语言中未定义的符号,用于指定指令行为

11.1 ALU32

ALU32指令类包括执行算术和逻辑运算的指令对32位数据的操作。

ALU32指令可在任何插槽上执行

11.1.1 ALU32/ALU

ALU32/ALU指令子类包括执行算术和算术运算的指令对单个32位项的逻辑操作.

添加

将源寄存器添加到另一个源寄存器或有符号16位立即数价值将结果存储在目标寄存器中。源寄存器和目标寄存器为32位。如果

结果溢出32位,它环绕。可选地将结果饱和为有符号值介于0x8000000和0x7FFFFF之间。

有关此操作的64位版本,请参阅XTYPE添加说明。

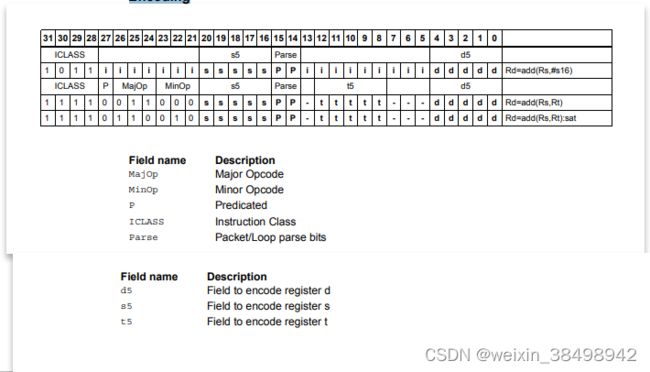

Syntax Behavior

Rd=add(Rs,#s16) apply_extension(#s);Rd=Rs+#s;

Rd=add(Rs,Rt) Rd=Rs+Rt;

Rd=add(Rs,Rt):sat Rd=sat_32(Rs+Rt);

类别:ALU32(插槽0,1,2,3)

注意:

■ 如果在执行该指令期间发生饱和(结果被箝位为最大值或最小值),设置状态寄存器中的OVF位。OVF保持设置,直到通过传输到SR显式清除为止

内部函数:

Rd=add(Rs,#s16) Word32 Q6_R_add_RI(Word32 Rs, Word32 Is16)

Rd=add(Rs,Rt) Word32 Q6_R_add_RR(Word32 Rs, Word32 Rt)

Rd=add(Rs,Rt):sat Word32 Q6_R_add_RR_sat(Word32 Rs, Word32 Rt)

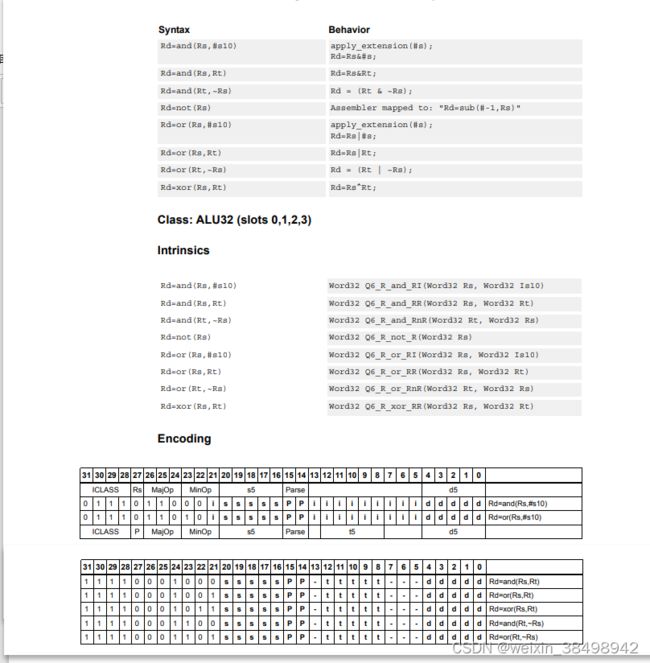

逻辑运算

在两个源寄存器上执行位逻辑运算(AND、OR、XOR、NOT)或在源寄存器和带符号的10位立即值上。将结果存储到目的地登记源寄存器和目标寄存器为32位。

字段名称说明

MajOp 主操作码

MinOp 次要操作码

Rs 无Rs读取

MajOp 主操作码

MinOp 次要操作码

P 断言

ICALSS 指导CLASS

parse 循环解析位

d5 用于编码寄存器d的d5字段

s5 字段编码寄存器s

t5 字段来编码寄存器t

取消

对源寄存器执行算术求反。将结果存储在目标寄存器中。源寄存器和目标寄存器为32位。

有关此指令的64位和饱和版本,请参阅XTYPE类逆向说明书

Syntax Behavior

Rd=neg(Rs) Assembler mapped to: "Rd=sub(#0,Rs)"

类别:不适用

内部函数

Rd=neg(Rs) Word32 Q6_R_neg_R(Word32 Rs)

Nop

不执行任何操作。本说明用于填充和对齐。

在分组内,它可以定位在任何时隙0-3中。

Syntax Behavior

nop

类别:ALU32(插槽0,1,2,3)

Field name Description

MajOp Major Opcode

Rs No Rs read

ICLASS Instruction Class

Parse Packet/Loop parse bits

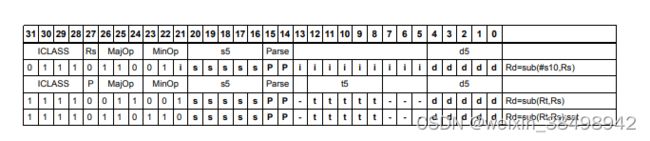

减

从另一个源寄存器或有符号的10位寄存器中减去源寄存器立即值。将结果存储在目标寄存器中。源和目标寄存器是32位。如果结果为32位下溢,则它将环绕。任选地将结果饱和至0000和0x7fff_ ffff之间的有符号值。

有关此操作的64位版本,请参阅XTYPE减法指令。

标识 行为

Rd=sub(#s10,Rs) apply_extension(#s);Rd=#s-Rs;

Rd=sub(Rt,Rs) Rd=Rt-Rs;

Rd=sub(Rt,Rs):sat Rd=sat_32(Rt - Rs)

内部函数

Rd=sub(#s10,Rs) Word32 Q6_R_sub_IR(Word32 Is10, Word32 Rs)

Rd=sub(Rt,Rs) Word32 Q6_R_sub_RR(Word32 Rt, Word32 Rs)

Rd=sub(Rt,Rs):sat Word32 Q6_R_sub_RR_sat(Word32 Rt, Word32 Rs)

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

MajOp Major Opcode

MinOp Minor Opcode

P Predicated

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s

t5 Field to encode register t

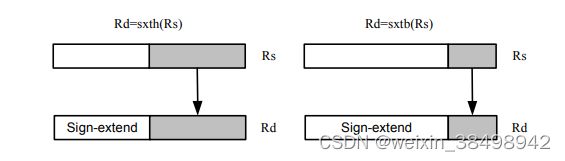

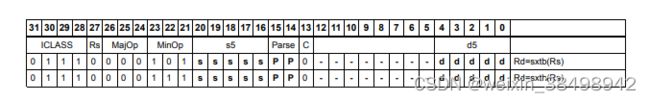

标志延伸

对源寄存器中最低有效字节或半字进行符号扩展,并将

Syntax Behavior

Rd=sxtb(Rs) Rd = sxt8->32(Rs);

Rd=sxth(Rs) Rd = sxt16->32(Rs);

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

C Conditional

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s

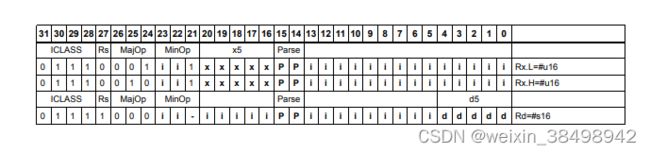

立即转移

为32位目标寄存器分配立即值。

支持两种类型的分配。第一个符号扩展了16位有符号立即数值设置为32位。第二种方法将一个16位无符号立即数值分配给上或目标寄存器的较低16位,保持其他16位不变。

Syntax Behavior

Rd=#s16 apply_extension(#s);Rd=#s;

Rdd=#s8 if ("#s8<0") {

Assembler mapped to: "Rdd=combine(#-1,#s8)";

} else {

Assembler mapped to: "Rdd=combine(#0,#s8)";

}

Rx.[HL]=#u16 Rx.h[01]=#u;

类别:ALU32(插槽0,1,2,3)

内部函数

Rd=#s16 Word32 Q6_R_equals_I(Word32 Is16)

Rdd=#s8 Word64 Q6_P_equals_I(Word32 Is8)

Rx.H=#u16 Word32 Q6_Rh_equals_I(Word32 Rx, Word32 Iu16)

Rx.L=#u16 Word32 Q6_Rl_equals_I(Word32 Rx, Word32 Iu16)

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s

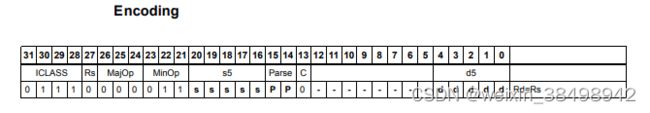

转移寄存器

将源寄存器传输到目标寄存器。源和目标寄存器是32位或64位。

Syntax Behavior

Rd=Rs Rd=Rs;

Rdd=Rss Assembler mapped to:

"Rdd=combine(Rss.H32,Rss.L32)"

类别:ALU32(插槽0,1,2,3)

内部函数

Rd=Rs Word32 Q6_R_equals_R(Word32 Rs)

Rdd=Rss Word64 Q6_P_equals_P(Word64 Rss)

解码

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

C Conditional

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s

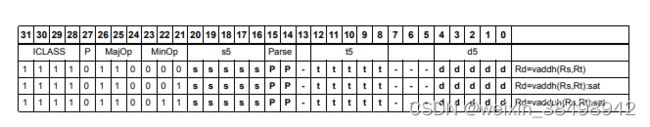

矢量加半字

将Rs的两个16位半字与Rt的两个16bit半字相加。结果如下:

可选地饱和为有符号或无符号16位值。

Syntax Behavior

Rd=vaddh(Rs,Rt)[:sat] for (i=0;i<2;i++) {

Rd.h[i]=[sat_16](Rs.h[i]+Rt.h[i]);

}

Rd=vadduh(Rs,Rt):sat for (i=0;i<2;i++) {

Rd.h[i]=usat_16(Rs.uh[i]+Rt.uh[i]);

}

类别:ALU32(插槽0,1,2,3)

注意

■ 如果在执行该指令期间发生饱和(结果被箝位为

最大值或最小值),设置状态寄存器中的OVF位。

OVF保持设置,直到通过传输到SR显式清除为止

内部函数

Rd=vaddh(Rs,Rt) Word32 Q6_R_vaddh_RR(Word32 Rs, Word32 Rt)

Rd=vaddh(Rs,Rt):sat Word32 Q6_R_vaddh_RR_sat(Word32 Rs, Word32 Rt)

Rd=vadduh(Rs,Rt):sat Word32 Q6_R_vadduh_RR_sat(Word32 Rs, Word32 Rt)

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

C Conditional

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s

向量平均半字

VAVGH将Rs的两个16位半字与Rd的两个16bit半字相加,然后移位结果正好是一位。(可选)在移位前添加舍入常数。

VNAVGH从Rs的两个16位半字中减去Rt的两个16bit半字,并将结果右移一位。有关带舍入的向量负平均值,请参见XTYPE VNAVGH指令。

Syntax Behavior

Rd=vaddh(Rs,Rt)[:sat] for (i=0;i<2;i++) {

Rd.h[i]=[sat_16](Rs.h[i]+Rt.h[i]);

}

Rd=vadduh(Rs,Rt):sat for (i=0;i<2;i++) {

Rd.h[i]=usat_16(Rs.uh[i]+Rt.uh[i]);

}

类别:ALU32(插槽0,1,2,3)

内部函数

Rd=vaddh(Rs,Rt) Word32 Q6_R_vaddh_RR(Word32 Rs, Word32 Rt)

Rd=vaddh(Rs,Rt):sat Word32 Q6_R_vaddh_RR_sat(Word32 Rs, Word32 Rt)

Rd=vadduh(Rs,Rt):sat Word32 Q6_R_vadduh_RR_sat(Word32 Rs, Word32 Rt)

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

C Conditional

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s

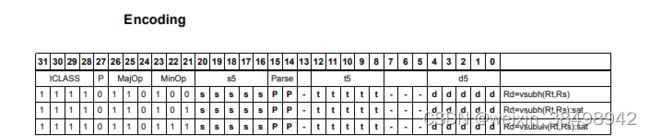

矢量减法半字

从中的相应半字中减去32位向量Rs中的两个半字矢量Rt。可选地对每个16位加法进行饱和,使之成为有符号或无符号的16位价值

对VSUBH指令应用饱和将结果钳制在有符号范围内0x8000到0x7fff,而对VSUBUH应用饱和可确保无符号结果在0到0xffff的范围内。当不需要饱和时,应使用VSUBH。

Syntax Behavior

Rd=vaddh(Rs,Rt)[:sat] for (i=0;i<2;i++) {

Rd.h[i]=[sat_16](Rs.h[i]+Rt.h[i]);

}

Rd=vadduh(Rs,Rt):sat for (i=0;i<2;i++) {

Rd.h[i]=usat_16(Rs.uh[i]+Rt.uh[i]);

}

类别:ALU32(插槽0,1,2,3)

注意

■ 如果在执行该指令期间发生饱和(结果被箝位为最大值或最小值),设置状态寄存器中的OVF位。OVF保持设置,直到通过传输到SR显式清除为止

内部函数

Rd=vaddh(Rs,Rt) Word32 Q6_R_vaddh_RR(Word32 Rs, Word32 Rt)

Rd=vaddh(Rs,Rt):sat Word32 Q6_R_vaddh_RR_sat(Word32 Rs, Word32 Rt)

Rd=vadduh(Rs,Rt):sat Word32 Q6_R_vadduh_RR_sat(Word32 Rs, Word32 Rt)

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

C Conditional

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s

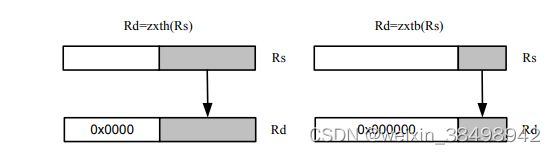

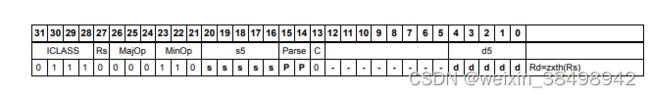

零延伸

Syntax Behavior

Rd=zxtb(Rs) Assembler mapped to: "Rd=and(Rs,#255)"

Rd=zxth(Rs) Rd = zxt16->32(Rs)

类别:ALU32(插槽0,1,2,3)

内部函数

Rd=zxtb(Rs) Word32 Q6_R_zxtb_R(Word32 Rs)

Rd=zxth(Rs) Word32 Q6_R_zxth_R(Word32 Rs)

Field name Description

MajOp Major Opcode

MinOp Minor Opcode

Rs No Rs read

C Conditional

ICLASS Instruction Class

Parse Packet/Loop parse bits

d5 Field to encode register d

s5 Field to encode register s