ICCV 2021 | LeViT: a Vision Transformer in ConvNet‘s Clothing for Faster Inference论文阅读笔记

论文:https://arxiv.org/abs/2104.01136

代码(刚刚开源):

https://github.com/facebookresearch/LeViT

ABSTRACT

我们设计了一系列的图像分类体系结构,在优化精度和效率之间权衡。我们的工作利用了基于最新发现注意力的架构,该架构在高度并行处理硬件上具有竞争力。我们回顾了许多文献中的卷积神经网络原理,将其应用于 transformers,特别是分辨率降低的激活图。我们还介绍了视觉 transformers中位置信息整合的新方法——注意偏差。为此,我们提出了一种用于图像快速推理分类的混合神经网络LeVIT。我们在不同的硬件平台上考虑不同的效率度量,最好地反映广泛的应用场景。我们的大量实验验证了我们的技术选择,并表明它们适用于大多数架构。总的来说,LeViT在速度/精度权衡方面显著优于现有的卷积网络和视觉 transformers。例如,在ImageNet top-1的80%精度下,LeViT在CPU上比EfficientNet快5倍。

Intruction

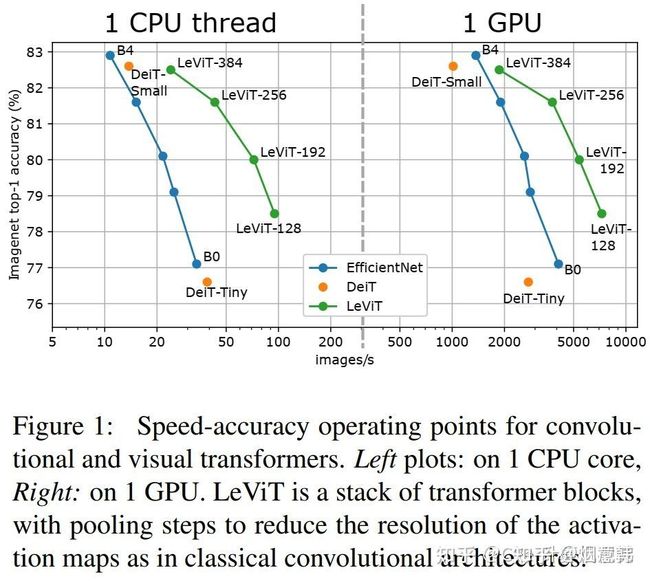

transformers神经网络最初是为自然语言处理应用[1]而引入的。他们现在在这一领域的大多数应用中占主导地位。它们操纵提供给残差结构的可变大小的嵌入序列。该模型包括两种残块:多层感知器(multilayer Perceptron, MLP)和一种原始类型的层:自我注意,它允许输入中的所有符号通过双线性函数组合.这与一维卷积方法相反,后者被限制在一个固定大小的邻域。近年来,视觉transformers(ViT)架构[2]在大规模数据集的预训练与速度精度的权衡中获得了最先进的图像分类结果。当仅在ImageNet[4]上训练ViT模型时,数据效率高的图像转换器[3]获得了最有竞争力的性能。它还引入了适合于高吞吐量推理的更小的模型。在本文中,我们探索了在中小型架构中提供比ViT/DeiT模型更好的权衡的设计空间。我们对优化性能精度的折衷特别感兴趣,比如图1中Imagenet-1k-val[5]所描述的吞吐量(图像/秒)性能。

虽然许多研究的目标是减少分类器和特征提取器的内存占用,但推理速度同样重要,高吞吐量对应更好的能量效率。在这项工作中,我们的目标是开发一个基于Vision transformer的模型家族,在GPU、常规Intel cpu和移动设备中常见的ARM硬件等高度并行架构上具有更好的推理速度。我们的解决方案重新引入了卷积组件,以取代学习卷积类特性的transformers组件。特别是,我们将Transformer的统一结构替换为带池的金字塔,类似于LeNet[11]架构。因此我们称之为LeViT。在给定的计算复杂度下,transformers比卷积架构更快,这是有令人信服的原因的。大多数硬件加速器(gpu、TPUs)都经过优化以执行大型矩阵乘法。在transformers中,注意和MLP块主要依赖于这些操作。相反,卷积需要复杂的数据访问模式,因此它们的操作通常是io绑定的。这些考虑对于我们探索速度/准确性的权衡是很重要的。

本文的贡献是允许ViT模型在宽度和空间分辨率方面缩小的技术:使用注意力作为降采样机制的多级变压器体系结构;一个计算效率高的 patch descriptor,可以在第一层中减少特征的数量;一个习得的,不变的注意偏差,取代了ViT的位置嵌入;一个重新设计的Attention-MLP块,在给定的计算时间内提高网络容量。

Related Work

从LeNet演化而来的卷积网络随着时间的推移已经有了很大的发展。最近的体系结构家族关注于在效率和性能之间找到一个好的平衡点。例如,通过在FLOPs约束下仔细设计单个组件,然后进行超参数搜索,发现了EfficientNet[17]系列。

transformer架构最初是由Vaswani等人[1]为机器翻译引入的。 transformer编码器主要依靠与前馈层结合的自注意操作,为学习长期依赖关系提供了一种强大而显式的方法。变压器随后被用于NLP任务,在各种基准上提供最先进的性能[20,21]。已经有许多尝试将 transformer架构应用于图像[22,23],首先是将它们应用于像素上。由于二次计算复杂性和注意机制涉及的参数数量,大多数作者[23,24]最初考虑的是小尺寸的图像,如CIFAR或Imagenet64[25]。混合文本和图像嵌入已经使用带有检测边界框的变压器作为输入[26],即大部分图像处理是在卷积域完成的。

视觉 transformer(ViT)[2]有趣的是,这种转换器架构非常接近最初的NLP版本,没有显式卷积(只是将固定大小的图像patch线性化成向量),但它与图像分类的最新技术相竞争。当ViT在大型标记数据集(如JFT300M)上进行预先训练时(非公开的,尽管在Imagenet-21k上训练也能产生有竞争力的结果),它可以获得较好的性能。这种预训练的需要,除了强大的数据增强,可以归因于这样一个事实,即与卷积相比,变压器的内置结构更少,特别是它们没有集中在附近的图像元素的归纳偏差。作者假设,需要一个大而多样的数据集来规范训练。在DeiT[3]中,对大的训练前数据集的需求被学生-教师设置和更强的数据增强和正则化所取代,如随机深度[27]或重复增强[28,29]。教师是一个卷积神经网络,它帮助学生网络获得卷积的归纳偏差。此后,视觉变压器已成功地应用于更广泛的计算机视觉任务,包括目标检测[30],语义分割[31]和图像检索[32]。

位置编码转换器接受一个集合作为输入,因此对输入的顺序是不变的。然而,在语言和图像中,输入来自于一个顺序很重要的结构。变压器[1]在输入中包含绝对非参数位置编码。其他的作品用参数编码[33]或采用基于傅里叶的内核版本[22]代替了它们。绝对位置编码强制输入集的大小固定,但有些工作使用相对位置编码[34]来编码令牌之间的相对位置。在我们的研究中,我们用隐性编码空间信息的位置偏差取代了这些显性位置编码。

其他注意机制一些研究包括视觉神经网络结构中的注意机制[35,36,37,38]。该机制用于信道获取交叉特征信息,以补充卷积层[39,40,41],在网络[42]的不同分支中选择路径,或将两者结合起来。例如,Hu等人[44]的挤压和复杂网络有一个类似注意力的模块,用来建模层的特征之间的通道关系。Li et al.[37]利用网络分支间的注意机制来适应神经元的感受场。最近,变压器的出现导致了受益于其他模块的混合架构。Bello[45]提出了一个带有位置注意成分的近似内容注意。Child等人[23]观察到,网络中的许多早期层学习了类似于卷积的局部连接模式。这表明,受到变压器和convnets启发的混合架构是一个引人注目的设计选择。最近的一些研究为不同的任务探索了这一途径[46,47]。在图像分类方面,最近与我们并行的作品是金字塔视觉变换器(PVT)[48],其设计深受ResNet的启发。它主要用于处理对象和实例分割任务。与我们的工作同时,Yuan et al.[49]提出token -to- token ViT (T2T-ViT)模型。类似于PVT,它的设计依赖于每一层之后通过聚合相邻的令牌对输出进行重令牌化,令牌的数量逐渐减少。此外,Yuan等人的[49]研究了集成cnn的架构设计选择[44,50,51],可以提高视觉变压器的性能和效率。

Motivation

在本节中,我们将讨论变压器patch投影层表面上的卷积行为。然后在标准卷积结构(ResNet-50)上进行了变压器(DeiTS)的移植实验。通过分析得出的结论将激励我们在第4节中的后续设计选择。

ViT的patch extractors是一个16x16的卷积,stride为16。此外,patch提取器的输出乘以学习的权值,形成第一自注意层s q, k和v嵌入,因此我们可以认为它们也是输入的卷积函数。这也是DeiT[3]和PVT[48]等变体的情况。在图2中,我们可视化了DeiT的第一层注意力权重,按注意力头进行分解。这比Dosovitskiy等人所描述的[2]的主成分更直接。我们可以观察到卷积架构固有的典型模式:注意力集中于特定的模式(低频颜色/高频灰度),这些模式类似于Gabor过滤器

在卷积蒙版重叠显著的卷积中,蒙版的空间平滑来自于重叠:附近的像素接收到近似相同的梯度。对于ViT卷积没有重叠。平滑蒙版可能是由数据增强引起的:当一个图像出现两次,稍微平移,相同的梯度通过每个过滤器,所以它学习这种空间平滑。因此,尽管在变压器架构中没有偏差,训练确实产生了类似于传统卷积层的滤波器。

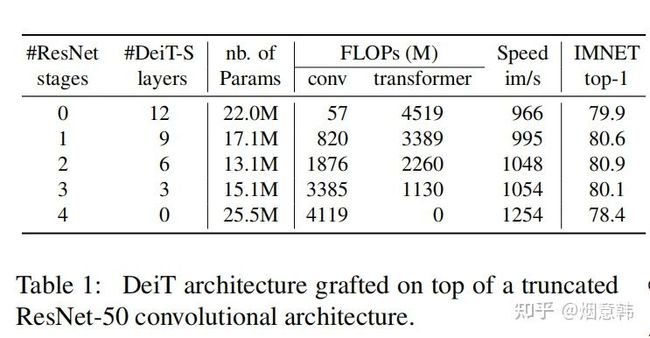

ViT图像分类器[2]的作者尝试将变压器层堆叠在传统的ResNet-50之上。在这种情况下,ResNet作为变压器层的特征提取器,梯度可以通过两个网络传播回去。然而,在他们的实验中,变压器的层数是固定的(例如维特基12层)。在这一小节中,我们研究了在类似的计算预算下混合变压器与卷积网络的潜力:我们探索了当改变卷积阶段和变压器层的数量时所获得的权衡。我们的目标是评估卷积和变压器混合的变化,同时控制运行时间。

嫁接这种嫁接结合了ResNet-50和DeiT-Small。这两个网络具有相似的运行时。我们裁剪了ResNet-50的上部阶段,同样减少了DeiT层的数量(同时保持相同数量的变压器和MLP块)。由于经过裁减的ResNet产生的激活图比DeiT消耗的14 x14激活图更大,所以我们在它们之间引入了一个池化层。在初步实验中,我们发现平均池的性能最好。在卷积层栈与变压器层栈的接口处引入位置嵌入和分类令牌。对于ResNet-50阶段,我们使用ReLU激活单元[52]和批处理正常化[53]。

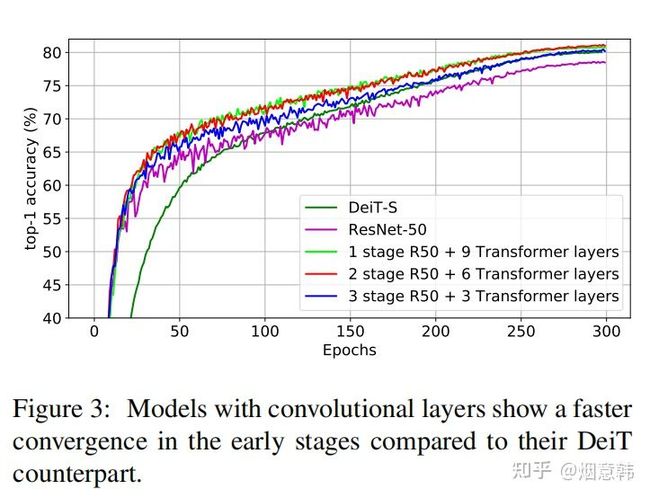

结果表1总结了结果。与DeiT和ResNet-50单用相比,该结构具有更好的效果。参数数最少、精度最好的是ResNet-50的两个阶段,因为这排除了convnet的大的第三阶段。需要注意的是,在这个实验中,训练过程类似于DeiT: 300 epoch,我们测量了ImageNet上的top-1验证精度,速度为一个GPU每秒可以处理的图像数量。我们在图3中展示的一个有趣的观察是,移植模型在训练期间的收敛速度似乎类似于早期时期的convnet,然后切换到类似于DeiT-S的收敛速度。一种假设是,卷积层有能力更有效地学习早期层中低层次信息的表示,这是由于它们强烈的归纳偏差,特别是它们的平移不变性。它们快速地依赖于有意义的补丁嵌入,这可以解释第一个时代更快的收敛。

讨论在运行时受控的情况下,在变压器下面插入卷积阶段是有益的。对于移植的体系结构的最精确变体,大多数处理仍然在转换器堆栈中完成。因此,下一节的重点将是减少变压器的计算成本。为此,不只是移植,转换器架构需要与卷积阶段更紧密地合并。

Model

在本节中,我们将描述LeViT体系结构的设计过程以及采取了哪些折衷措施。图4总结了该体系结构。LeViT建立在ViT[2]架构和DeiT[3]培训方法的基础上。我们合并了被证明对卷积架构有用的组件。第一步是获得一个兼容的表示。不考虑分类嵌入的作用,ViT是一个处理激活映射的层堆栈。实际上,中间令牌嵌入可以被视为FCN架构(BCHW格式)中传统的C - H - W激活映射。因此,应用于激活映射(池化、卷积)的操作可以应用于DeiT的中间表示。在这项工作中,我们优化了计算的架构,而不是最小化参数的数量。使ResNet[14]系列比VGG网络[13]更高效的设计决策之一是在前两个阶段以相对较小的计算预算实现高分辨率降低。当激活图达到ResNet的第三大阶段时,其分辨率已经缩小到足够小的激活图应用卷积,从而降低了计算成本。

第3节的初步分析表明,在变压器堆栈的输入上应用一个小的convnet可以提高精度

Patch embedding

在LeViT中,我们选择对输入应用4层3 X3卷积(步幅2)来执行分辨率降低。通道数C = 3,32 64 128 256。这减少了对变压器较低层次的激活映射输入,而不丢失显著信息。LeViT-256的patch提取器用184 MFLOPs将图像形状(3,224,224)转换为(256,14,14)。作为比较,ResNet-18的前10层使用1042 MFLOPs执行相同的降维操作。

No classifification token.

为了使用BCHW张量格式,我们去掉了分类令牌。类似于卷积网络,我们用最后一个激活映射上的平均池代替它,这产生一个用于分类器的嵌入。在训练蒸馏时,我们训练分头进行分类和蒸馏任务。在测试时间,我们平均两个头的输出。在实践中,LeViT可以使用BNC或BCHW张量格式,哪个更有效。

Normalization layers and activations.

ViT架构中的FC层相当于11个卷积。ViT在每个注意点和MLP单元之前使用层归一化。对于LeViT,每次卷积之后都要进行批处理归一化。在[54]之后,与剩余连接连接的每个批处理规范化权重参数都被初始化为零。批正常化可以合并前卷积的推断,这是一个运行时优势层正常化(例如,在EfficientNet B0,这种融合对GPU加速推理因素2)。而DeiT使用GELU函数,所有LeViT s非线性激活Hardswish[19]。

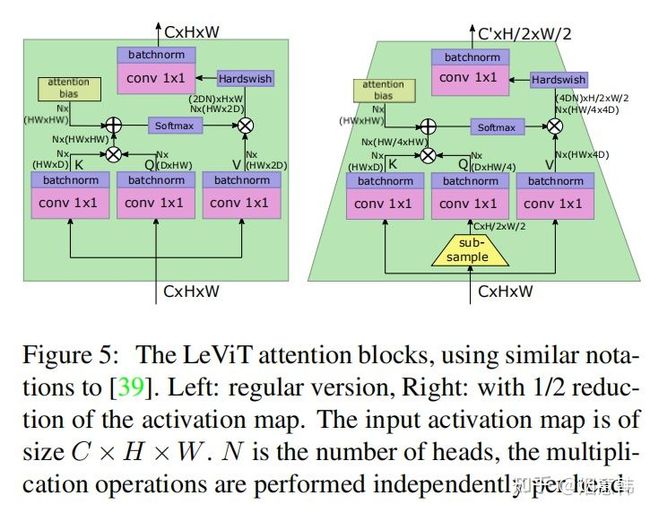

Multi-resolution pyramid

卷积架构被构建成金字塔,在处理过程中,激活图的分辨率随着通道数量的增加而降低。在第3节中,我们使用ResNet-50阶段对变压器堆栈进行预处理。LeViT在转换器体系结构中集成了ResNet阶段。在这些阶段内部,体系结构类似于一个视觉转换器:一个带有交替MLP和激活块的残余结构。在下面的文章中,我们将对比经典设置[1]对注意块的修改(图5)。

Downsampling

在LeViT阶段之间,收缩的注意块减少了激活图的大小:在Q变换之前应用了子采样,然后传播到软激活的输出。它将一个大小为(C, H, W)的输入张量映射为一个大小为(C0, H/2, W/2)的输出张量,具有C0 >C.由于规模的变化,这个注意块使用时没有残余连接。为了防止信息的丢失,我们将注意力头的数量记为C/D。

Attention bias instead of a positional embedding

变压器架构中的位置嵌入是一个与位置相关的可训练参数向量,在将其输入到变压器块之前,将其添加到令牌嵌入中。如果它不存在,变压器输出将独立于输入标记的排列。位置嵌入的烧蚀导致分类精度[55]急剧下降。然而,位置嵌入只包含在对注意块序列的输入上。因此,由于位置编码对较高层也很重要,它很可能仍然停留在中间表示中,并不必要地使用表示容量。因此,我们的目标是在每个注意块中提供位置信息,并明确地在注意机制中注入相对位置信息:我们只是简单地在注意地图中添加一个注意偏差。计算一个头部H [N]的两个像素(x, y) [H] [W]和(x0, y0) [H] [W]之间的标量注意值为

第一项是经典注意力。第二种是翻译不变注意偏差。每个头都有对应不同像素偏移量的hw参数。对称差异会鼓励模型使用翻转不变性进行训练。

smaller keys

偏置项减少了键编码位置信息的压力,因此我们减少了相对于V矩阵的键矩阵的大小。如果键的大小为D{16,32},则V将具有2D通道。限制密钥的大小可以减少计算密钥产品QK>所需的时间。对于下采样层,在没有残留连接的情况下,我们将V的维数设为4D,以防止信息丢失。

Attention activation

在使用正则线性投影组合不同头部的输出之前,我们对产品AhV应用Hardswish激活。这类似于ResNet瓶颈残留块,在某种意义上,V是一个11卷积的输出,AhV对应一个空间卷积,而投影是另一个11卷积。

Reducing the MLP blocks.

ViT中的MLP残块是一个线性层,它将嵌入维数增加4倍,应用一个非线性,然后用另一个非线性将其降回原来的嵌入维数。对于视觉架构,MLP在运行时间和参数方面通常比注意力块更昂贵。对于LeViT, MLP是一个11卷积,然后是通常的批处理归一化。为了减少该相位的计算代价,我们将卷积的展开因子从4减小到2。一个设计目标是注意和MLP块消耗大约相同数量的flop。

The LeViT family of models

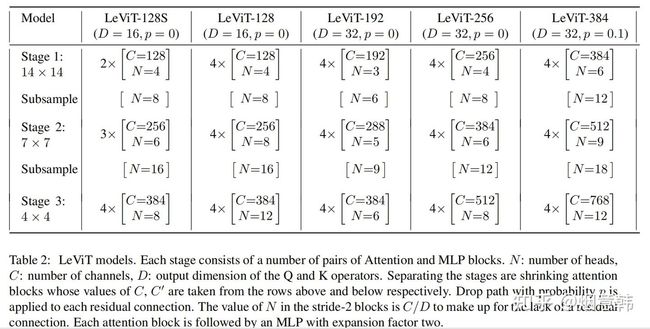

LeViT模型可以通过改变计算阶段的大小来产生一系列速度-精度折衷。我们通过输入到第一个变压器的通道数来识别它们,例如LeViT-256在变压器级的输入上有256个通道。表2显示了我们在本文中评估的模型的阶段是如何设计的。

Experiments

Datasets and evaluation.

我们以DeiT工作为模型进行实验,这与我们的方法最接近。它构建在PyTorch[56]和Timm库[57]之上。我们在ImageNet-2012数据集上进行训练,并在其验证集上进行评估。我们不打算在这项工作中使用更多的训练数据。

Resource consumption.

一般公认的推理速度的度量单位是乘法-加运算(又名FLOPs),因为浮点矩阵乘法和卷积可以表示为这些运算。然而,一些操作,最明显的非线性激活,不执行乘加操作。它们通常在FLOP计数中被忽略(或作为一个单独的FLOP计数),因为我们假设它们的代价与高阶矩阵乘法和卷积的代价相比可以忽略不计。然而,对于少数信道,像GELU这样复杂的激活的运行时间可以与卷积的运行时间相媲美。此外,使用相同数量的flop的操作的效率可能更高或更低,这取决于所使用的硬件和API。因此,我们还报道了参考硬件的原始计时,就像最近的论文[2,58]。变压器的效率几乎完全依赖于矩阵乘法的大降维。

Hardware.

在这项工作中,我们在PyTorch中运行所有的实验,因此我们依赖于该API中可用的优化。为了获得更客观的计时,我们在三个不同的硬件平台上对推断进行计时,每个硬件平台对应一个用例:一个16GB的NVIDIA Volta GPU(峰值性能为12 TFLOP/s)。这是一个典型的训练加速器。Intel Xeon 6138 2.0GHz CPU。这是数据中心中典型的服务器,对传入的图像流执行特征提取。PyTorch使用MKL和AVX2指令(16个每个256位的向量寄存器),对这种配置进行了很好的优化。一个ARM的gravon2 CPU (Amazon C6g实例)。对于移动电话和其他边缘设备运行的处理器类型来说,这是一个很好的模型。gravon2有32个核心,支持带有32个128位向量寄存器(NEON)的NEON向量指令集。

在GPU上,我们在大图像批量上运行计时,因为这符合典型的用例;在DeiT之后,我们使用适合内存的最大2次幂批处理大小。在CPU平台上,我们测量单个线程的推断时间,模拟几个线程处理独立的输入图像流的设置。很难区分硬件和软件的影响,因此我们尝试了几种方法来使用标准PyTorch工具(justin-time编译器、不同的优化配置文件)来优化网络。

Training LeViT

我们使用32个gpu,在3到5天内完成1000个训练周期。这比卷积网络通常的时间表要多,但是视觉变压器需要长时间的训练,例如训练DeiT 1000个epoch,比300个epoch提高了2个top-1精度。为了使培训规范化,我们使用蒸馏驱动培训,类似于DeiT。这意味着LeViT是用两个具有交叉熵损失的分类头训练的。第一个头部接受地面真相类的监督,第二个头部接受RegNetY-16GF[18]模型在ImageNet上训练的监督。事实上,LeViT培训时间主要由教师的推理时间支配。

Speed accuracy tradeoffs

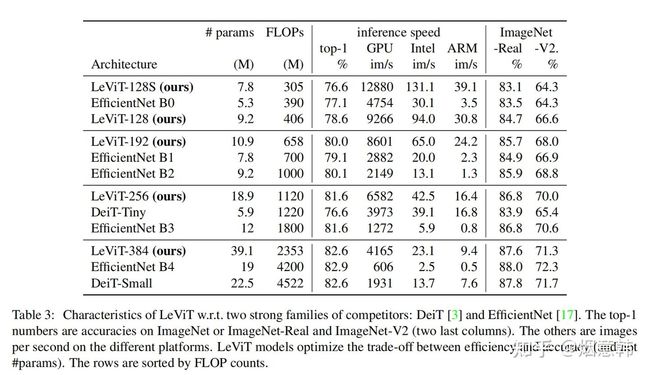

表3显示了我们用LeViT获得的速度-精度权衡,一些显著的数字绘制在图1中。我们将其与当前两种具有竞争力的架构进行比较:作为强大卷积基线的EfficientNet[17],以及类似的DeiT[3],一个强大的仅使用变压器的架构。这两个基线都经过训练,以最大限度地提高其准确性。例如,我们将其与1000年代训练的DeiT进行比较。在我们考虑的操作点范围内,LeViT体系结构在很大程度上优于转换器和卷积变体。LeViT-384在精度上与DeiTSmall不相上下,但使用了一半的flop数量。在更快的操作点上,差距扩大了:LeViT-128S与DeiT-Tiny不相上下,使用4个更少的FLOPs。运行时度量紧跟这些趋势。例如LeViT-192和LeViT-256的精度与EfficientNet B2和B3差不多,但在CPU上分别快了5倍和7倍

Comparison with the state of the art

表4报告了与LeViT比较的其他基于变压器的架构的结果(表3)。由于我们的方法专门研究高吞吐量,我们不包括非常大和慢的模型[61,62]。我们比较了flops的精度权衡,因为其他的工作都是最近的,并没有必要提供参考模型,我们可以对推断进行计时。所有令牌到令牌ViT[49]变体比LeViT多使用5个FLOPs,并比LeViT多使用更多参数以获得可比较的精度。瓶颈变压器[46]和视觉变压器[47](不要与ViT混淆)都是通用架构,也可以用于检测和目标分割。在相当的精度下,两者都比LeViT-192慢5。金字塔视觉变压器[48](表中没有报告)也是如此,但它的设计目标是不同的。与这些架构相比,LeViT的优势在于它受益于类似deit的蒸馏,这使得它在单独使用ImageNet进行训练时更加准确

Conclusion

本文介绍了LeViT,一种基于卷积方法的变压器架构。LeViT的准确性主要来源于DeiT中的训练技术。它的速度来自于一系列精心控制的设计选择。与其他用于数据中心或手机特征提取的高效神经网络相比,LeViT在同等精度下的速度要快1.5到5倍。因此,据我们所知,它在高速领域的精度和精度之间建立了一个新的艺术状态。

本篇文章对大家学习计算机视觉有帮助的话关注一下点点赞哦