Verilog中浅谈for与generate for

标题

简介

在C语言或者其他编程语言中for语句往往用作循环语句,但是在硬件电路Verilog 中一般不在可综合代码中使用,因为for循环会被综合器展开为所有变量情况的执行语句 ,每个变量独立占用寄存器资源,每条执行语并不能有效地复用硬件逻辑资源,造成巨大的资源浪费。 简单的说就是:for语句循环几次,就是将相同的电路复制几次,因此循环次数越多,占用面积越大, 综合就越慢。for语句的一般 使用 情况: 在testbench中 使用 ,往往用于激励信号的生成。

在for循环中需要用到Integer,Integer在电路里面生成的是buffer。但是在测试激励里面读取不了Integer循环时的每一个值。一般不推荐使用

在generate-for中需要用到参数定义genvar。generate语句有generate-for,generate-if,generate-case三种语句。这里重点介绍generate for语句。主要有以下几个需要注意的点

(1) 必须有genvar关键字定义for语句的变量。

(2)for语句的内容必须加begin和end(即使就一句)。

(3)for语句必须有个名字。

下面举几个例子说明一下:

例1、genvar…generate…endgenerate 使用方法

module top_module(

input [7:0] in,

output [7:0] out

);

genvar i;

generate

for(i = 0; i < 8; i = i + 1) begin : bit_reverse

assign out[i] = in[7 - i];

end

endgenerate

endmodule

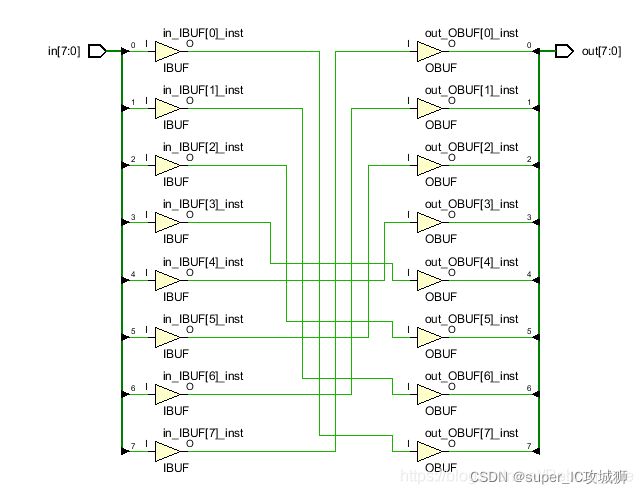

生成的schematic图:

例2、for 使用方法:组合逻辑

注意for不能单独使用,要放到always块内使用,且always块要有名字:

module top_module(

input [7:0] in,

output [7:0] out

);

reg [7:0] out;

always@(*) begin: bit_reverse

integer i;

for(i = 0;i <8; i = i + 1) begin

out[i] = in[7-i];

end

end

endmodule

生成的schematic图:

通过对例1和例2对比,发现二者综合出来的电路没有任何区别,都能使用,只是写法不同,需要注意的要点也不同。

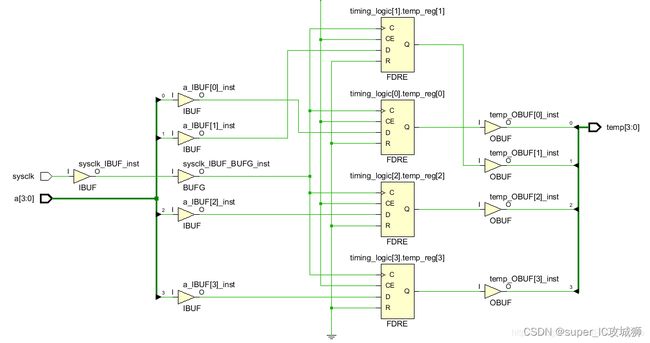

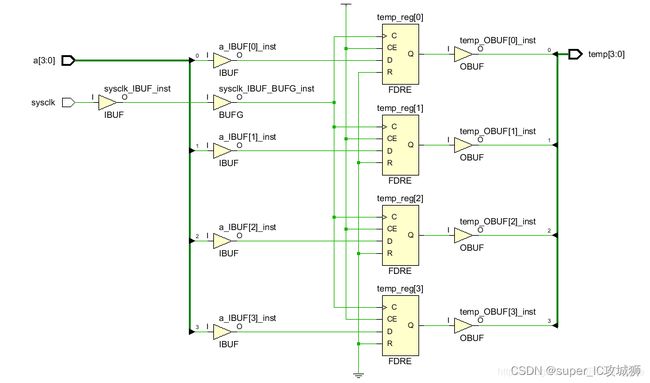

3、generate里面加上时序逻辑

module top_module(

input sysclk,

input [3:0] a,

output [3:0] temp

);

reg [3:0] temp = 0;

genvar i;

generate

for (i = 0; i < 4 ; i = i + 1) begin: timing_logic

always @(posedge sysclk) begin

temp[i] <= a[i];

end

end

endgenerate

endmodule

module top_module(

input sysclk,

input [3:0] a,

output [3:0] temp

);

reg [3:0] temp = 0;

always @(posedge sysclk) begin: timing_logic

integer i;

for (i = 0; i < 4 ; i = i + 1) begin

temp[i] <= a[i];

end

end

endmodule

例5、将一个位宽八位的数据依次反转

方式一:

module top_module(

input [7:0] in,

output [7:0] out

);

genvar i;

generate

for(i = 0; i < 8; i = i + 1) begin : bit_reverse

assign out[i] = in[7 - i];

end

endgenerate

endmodule

方式二:

module top_module(

input [7:0] in,

output [7:0] out

);

reg out;

genvar i;

generate

for(i = 0; i < 8; i = i + 1) begin : bit_reverse

always@(*) begin

out[i] = in[7 - i];

end

end

endgenerate

endmodule