【分享干货】AD9653调试笔记

标题AD9653调试笔记

一、简介

AD9653是ADI公司于2012年推出的一款四通道、16位、125MSPS模数转换器,内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性设计。该产品转换速率最高可达125MSPS,具有接触的动态性能与低功耗特性,对小封装尺寸的应用很有意义。

二、研究目的

目前在导航领域,小型化、低功耗、国产化一直是国内的研究方向。

1、占板面积小

一片AD9653拥有四个通道。由于是采用串行输出的方式,AD9653的封装为LFCSP-48。相较于主流使用的并行AD(AD9269、AD9650)的LFCSP-64封装面积减少了约40%。且由于AD9653为四通道串行,仅需两片芯片,16根数据线,即可实现八通道。而是用并行AD则需四片芯片,64根数据线。

2、功耗低

表2-1给出了几种AD的功耗参数。

表2-1 不同AD的详细功耗参数

AD9269 AD9650 YA16D80S BLAD16D80S AD9653 BLAD16Q125

工作模式 并行 并行 并行 并行 串行 串行

直流输入功耗 200mW 656mW 520mW 477mW 607mW 610mW

正弦输入功耗 230mW 663mW 540mW 530mW 650mW 630mW

待机功耗 37mW 50mW 80mW 356mW 48.6mW

掉电功耗 1mW 0.25mW 5mW 10mW 2mW 10.8mW

由上表的统计数据可以看出,两片AD9653的功耗略大于四片AD9269,但是不到四片AD9650功耗的一半。因此在八通道的应用中,相较于使用并行方案,仅从AD看可以减少1W的功耗。

3、采样速率高

AD9653采样速率为125MSPS,在中频采样中可以提供足够的带宽。

4、国产化

AD9653有国产化替代器件BLAD16Q125,是上海贝岭生产的PIN TO PIN芯片。封装、引脚定义与AD9653相同,能够直接替换AD9653。在国产化项目上可直接替换AD9653,无需二次开发。

三、硬件设计

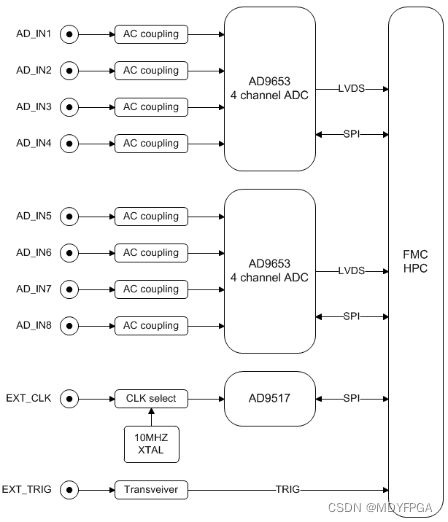

本文硬件设计部分主要针对明德扬mdyAD9653FMC板卡来介绍。其主要功能如下:

➢ 搭载两片 ADC 芯片,支持 ADI、上海贝岭、北京时代民芯科技、中电 24 所

等生产的芯片,完全 PIN 对 PIN 兼容;

➢ 共支持 8 通道同步输入;

➢ 支持 16 位采样分辨率;

➢ 支持最高 125MSPS 的采样率;

➢ 支持内外部时钟自动切换;

➢ 板载一片 10MHz/0.5ppm 的温补晶振;

➢ 集成了时钟分部芯片 AD9517-1,配合相应的 FMC 载板能完成多通道宽带

信号采集;

➢ 适用于医疗超声和 MRI、高速成像、正交无线电接收机、分集无线电接收机、

测试设备、雷达、卫星导航等多种应用场合。

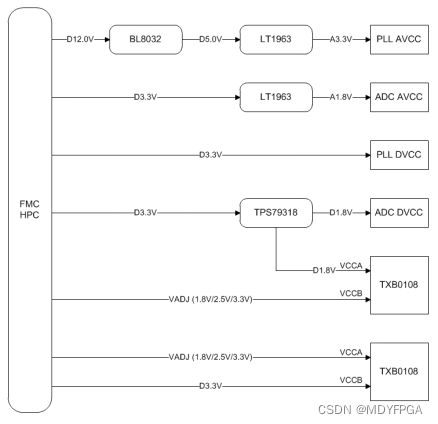

图3-1和3-2为硬件方案框图。具体分为以下几个部分。

图3-1 mdyAD9653FMC板卡硬件方案框图

图3-2 mdyAD9653FMC板卡电源方案框图

1、AD采样电路

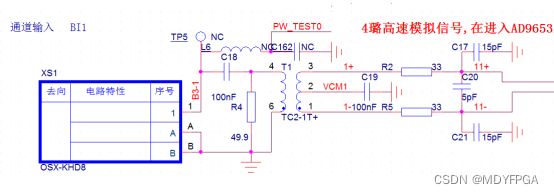

AD信号输入端电路如图3-2所示:

图3-2 AD信号输入端电路

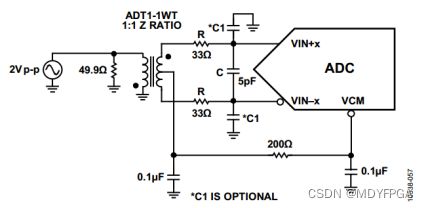

中频信号通过巴伦将单端转为差分送入AD9653。手册中使用的巴伦匝数比为1:1,而经过实际的测试及理论分析,发现1:2的巴伦能够有效地降低级联噪声系数。巴伦后级的阻容器件要根据手册提供的电路进行配置。如图3-2所示:

图3-2 AD9653单巴伦单端转差分电路

参考电压使用用外部1.25V,使用的是ADR127,可以和ADR130(1V参考)互换。这样可以确保在使用1:2巴伦时,AD的满幅为10dBm。表3-1为AD满幅测试数据:

表3-1 AD满幅测试数据

通道 CH1 CH2 CH3 CH4 CH5 CH6 CH7 CH8

信号源功率 9.9dBm 9.9dBm 9.9dBm 9.9dBm 9.9dBm 9.9dBm 9.9dBm 9.9dBm

2、时钟电路

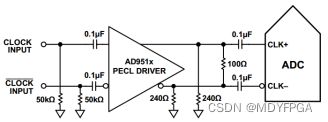

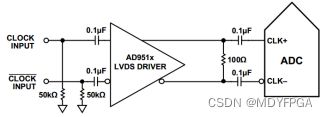

采用AD9517-1作为抗干扰板的主时钟源。FMC板输入参考时钟为62MHz,之后由9517分别为两片AD以及FPGA提供62MHz时钟。其中,两片AD输出的FCO和DCO信号均连接至FPGA,作为数据时钟和帧同步时钟。图3-3和3-4分别为LVEPCL和LVDS接口的时钟匹配电路。

图3-3 LVPECL接口时钟驱动电路

图3-4 LVDS接口时钟驱动电路

四、驱动程序设计

这里主要介绍ADC的驱动。

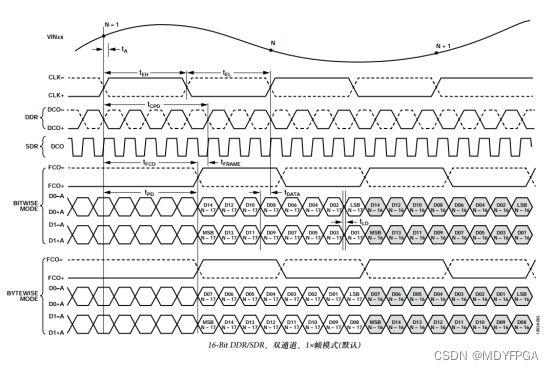

AD9653是4通道、16位、125 MSPS高速串行LVDS模数转换器。该ADC会自动倍乘采样速率时钟,以便产生合适的LVDS串行数据速率。它提供一个数据时钟输出(DCO)用于在输出端捕获数据,以及一个帧时钟输出(FCO)用于发送新输出字节信号。每一个通道都拥有两组LVDS差分数据线,在默认模式下分别串行传输偶数位和奇数位数据。图4-1是AD9653在默认工作模式下的时序图:

图4-1 默认模式下的时序图

Fs为62MHZ,在DDR模式下,DCO为248MHz,FCO为62MHz。因此时序调整在设计中格外重要。

AD9653共有两种驱动方式:一种是利用测试码来进行同步操作,然后切换到正常工作模式继续运行;另一种是利用帧同步信号直接锁定每一帧数据。下面对使用测试码对齐的方式简称Bitslip模式,对使用帧同步信号对齐的方式简称FCO模式。

1、Bitslip模式

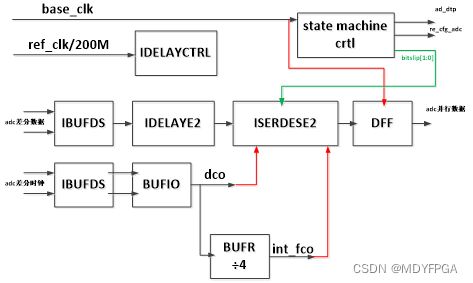

Bitslip模式的工作原理是通过SPI配置先让AD工作在测试模式,在这个模式下,AD的每一个通道会重复输出测试码(A19C)。FPGA读取每一通道的数据并进行移位调整和串并转换。当所有通道都对齐后,再次通过SPI配置AD使其退出测试模式,这样移位信息将得到保留,因此输出的AD数据就是正确的。该工作方式的架构如图4-2所示:

图4-2 Bitslip模式程序架构

然而这种工作方式有一个缺点。不难发现,对齐工作仅发生在系统上电之后,一旦对齐,就没办法在让AD回到测试模式。这样就会造成一个问题:系统刚上电时,板子温度低,工作一段时间后板子温度上升。时钟以及已配置好的ISERDESE模块随着温度的升高会发生飘移,但是这时已经不能再次进入测试模式进行对齐。因此就会出现上电时间越长,噪声系数越大的现象。所以没办法满足高低温工作的需求。

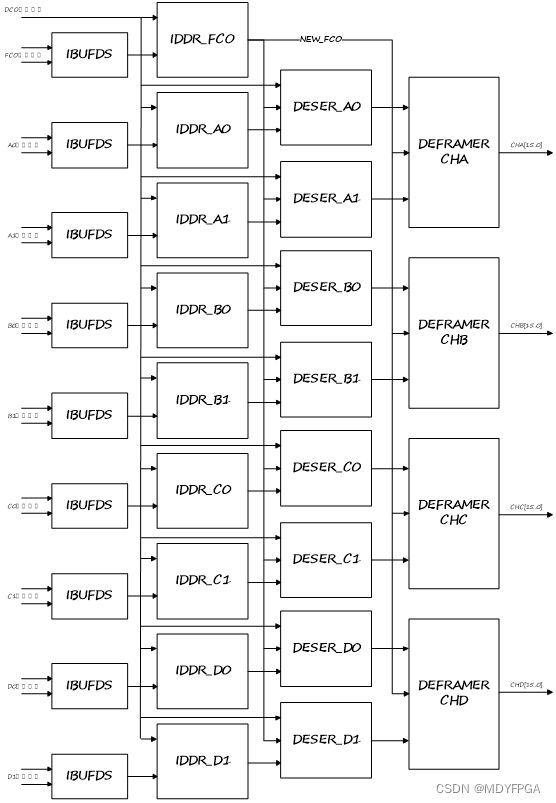

2、FCO模式

FCO模式的工作原理为将DCO和FCO同时输入到模块内,通过DCO来捕获数据,然后通过FCO来对齐数据,之后再进行串并转换。该工作模式的架构如图4-3所示:

首先,DCO与FCO信号通过IDDR_FCO模块,以DCO为参照进行对齐。同时,对四个通道共八组差分数据信号以DCO为参照对齐。之后在DESER模块中根据FCO上升沿的位置将数据分组,输出8位并行数据,共八组。最后通过DEFRAMER模块将每个通道的数据合并,输出16位的AD数据。

此工作模式避免了Bitslip模式不能依照温度修正的问题,由于使用的是AD芯片的FCO信号作为帧同步的参考,每通过一组数据,就能实现一次对齐,这样就不会受温度的影响。实际测试中也发现温度升高后,级联噪声系数很稳定。

另一个优点就是该工作模式可以兼容上海贝岭的BLAD16Q125芯片。由于贝岭AD的测试码为0x8000,而AD9653的测试码为0XA19C,因此Bitslip模式需要更改程序才能在贝岭的AD上使用。

图4-3 FCO模式程序架构

3、时钟网络设置

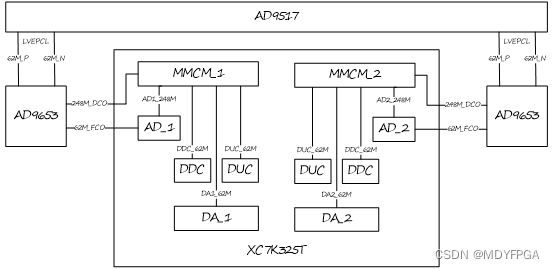

以FCO模式为例,该模式的时钟树如图4-4所示:

图4-4 FCO模式时钟树

在FCO模式下,两片AD不在同一个时钟网络下,而是各自使用一个MMCM模块。AD的DCO输出作为MMCM模块的输入,生成一个62MHz信号作为AD数据采集、上下变频和DA输出的时钟,以及一个248MHz信号作为AD的新DCO时钟,以其作为参照,对齐FCO和数据。

4、时序调整

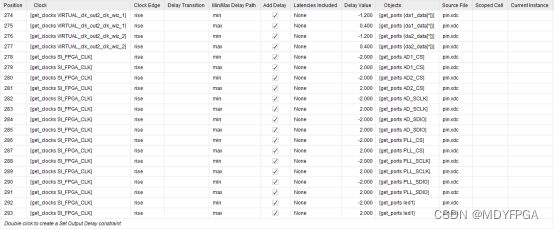

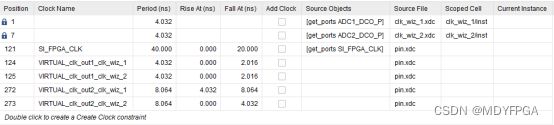

同样以FCO模式为例,时钟约束如图4-5所示:

图4-5 FCO模式下时钟约束

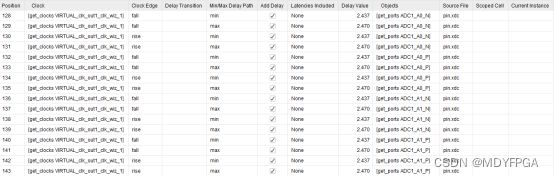

由于令MMCM输出的248MHz时钟的相位为90°,AD数据的延时时间设定为:min=2.437ns,max=2.470ns。部分AD时序约束如图4-6所示:

图4-7 输出时序约束

五、单板测试

本测试实例是在明德扬MP5620开发板与mdyAD9653FMC板卡上实现。

1、满幅测试

测试条件为:

巴伦匝数比:1:2;参考电压:外部1.25V;AD位数:16bits

测试结果如表5-1所示:

表5-1 满幅测试结果

通道 CH1 CH2 CH3 CH4

信号源功率 9.8dBm 9.8dBm 9.8dBm 9.8dBm

信号源峰峰值 1.954V 1.954V 1.954V 1.954V

AD量化值 32768 32768 32768 32768

测试结果与理论值10dBm/2V Vpp差0.2dBm/0.046V Vpp,考虑到线损等因素误差在允许范围内。

2、AD信噪比测试

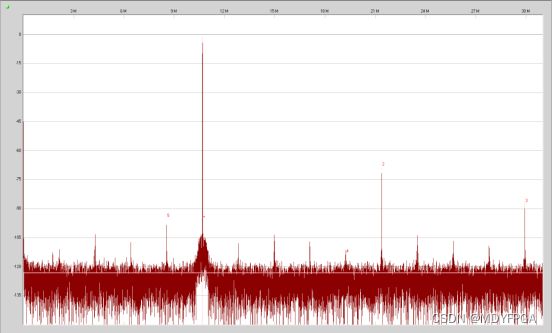

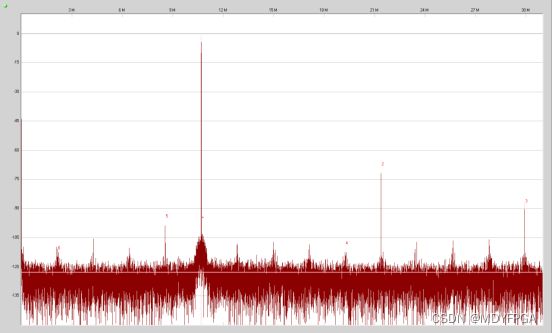

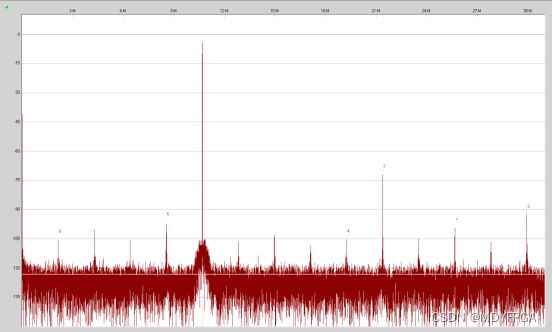

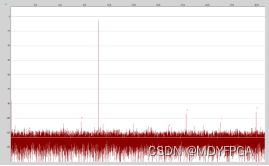

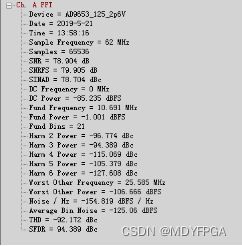

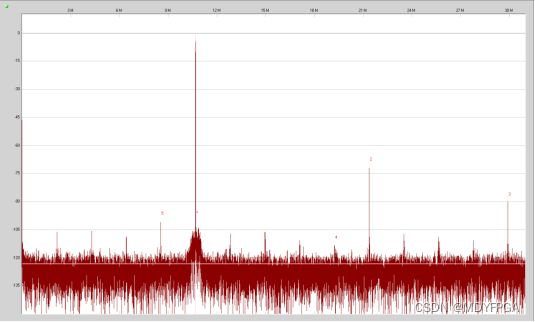

四通道的频谱分别如图5-2、5-3、5-4、5-5所示:

图5-3 CH2频谱

图5-5 CH4频谱

四通道测试结果如表5-2所示:

通道 CH1 CH2 CH3 CH4

采样频率

MHz 62MHz 62MHz 62MHz 62MHz

采样点数 65536 65536 65536 65536

SNR

dB 76.893 76.953 76.607 77.047

SNRFS

dB 78.157 78.044 77.738 78.172

主瓣功率

dB -1.263 -1.091 -1.130 -1.125

主瓣频率

MHz 10.69 10.69 10.69 10.69

每Hz噪声

dBFS/Hz -153.07 -152.958 -152.651 -153.086

图5-7 AD9653仿真数据

实测SNR比仿真小了约1.9dB,实测每赫兹噪声比仿真小了约1.8dB。由此可见本设计已基本发挥出AD9653的性能。

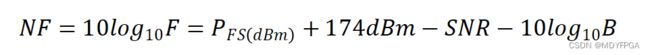

3、AD噪声系数计算

根据AD噪声系数计算公式:

每通道噪声系数如表5-3所示:

表5-3 每通道AD噪声系数

通道 CH1 CH2 CH3 CH4

NF 30.743dB 30.856dB 31.162dB 30.728dB

图5-8 级联噪声系数计算方法

六、总结

本文详细介绍了AD9653的硬件、软件设计方法,以及ADC的增益、噪声系数测量手段。配合明德扬的MP5620+mdyAD9653FMC平台,可以大大缩短设计周期,直接进行软件开发。也能在该平台对国产器件进行性能上的对比验证。