电流模架构Bandgap设计与仿真

电流模架构Bandgap设计与仿真

0. Bandgap电压基准源

带隙基准作为集成电路中一个重要模块,被广泛应用在低压差线性稳压(LDO)、充电电池保护芯片和通信电路、射频收发器、flash存储器等多种模拟及数模混合集成电路中,并且是片上集成系统(SOC)芯片中不可或缺的部分,为整个芯片提供精确的电压参考点。

1. Bandgap的温度系数补偿原理

带隙基准源的基本原理是将两个拥有相反温度系数的电压以合适的权重相加,最终获得具有零温度系数的基准电压。因为传统带隙基准的输出值为1.2V,与硅带隙电压Eg/q值基本相等,所以这种基准电压源形象地称为带隙基准源。

1.1 负温度系数电压

双极晶体管的基极-发射极电压,或者更一般的说,一个正向导通的二极管具有负温度系数,可以写出其正向偏置电流:Ic=Isexp(VBE/VT),其中VBE为基极-发射极电压,VT=kT/q,Is为饱和电流,有Is=bT4+mexp(-Eg/kT),b为比例系数,m≈-3/2,Eg为Si的带隙能量,常温下Eg=1.12ev。VBE=VTln(IC/IS),VBE对温度求导有:

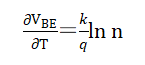

式1.1

式1.1

当VBE≈800mV时,∂VBE/∂T≈-1.5mV/K。

1.2 正温度系数电压

当两个晶体管工作在不相等的电流密度下,那么它们的基极-发射极电压的差值与温度成正比:

ΔVBE=VBE1-VBE2=VTln(nIC/IS)-VTln(IC/IS)=VTln n

式1.2.1

VBE对温度求导有: 式1.2.2

式1.2.2

其中k/q≈0.087mV/K。

2. 电流模架构Bandgap分析与设计

2.1 Bandgap结构分析

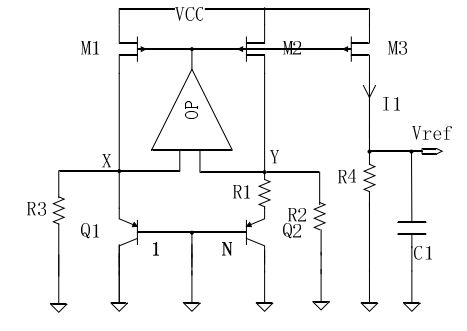

Bandgap有电流模和电压模两种常见结构,如下所示:

图2-1 电压模架构Bandgap

此结构存在正反馈和负反馈两个环路,为了使负反馈强于正反馈,运放的正端需接在R1端。运算放大器将VN和VP两端电压嵌位,将在R1两端产生一个ΔVBE的压降,产生PTAT(proportional to absolute temperature,正比于绝对温度)电流,电流值为VTln n/R1,其中Q2由N个pnp并联而成。M1、M2给Q1、Q2提供大小相等的电流,M3则将该PTAT电流镜像到Q3,R2乘以该电流并和负温度系数电压VBE3叠加产生VREF。VREF的计算关系如下:

式2.1

式2.1

为了得到零温度系数电压,电压模架构Bandgap只能固定输出1.2V左右的带隙基准电压。

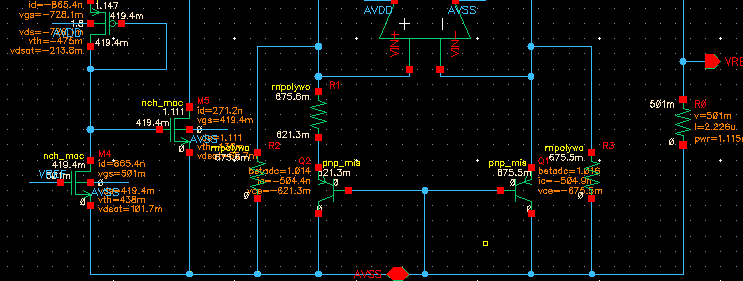

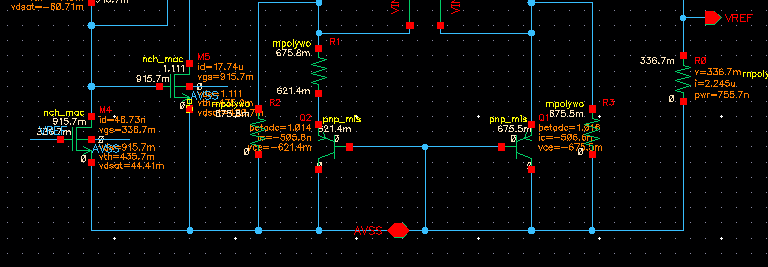

图2-2 电流模架构Bandgap

通过运放嵌位作用,R1将产生PTAT电流,R2、R3是两个大小相等的电阻,将产生大小为VBE/R2的CTAT(反比于绝对温度)电流,通过调整R1、R2将产生零温度系数电流,最后通过M3将电流镜像到输出端,VREF的值可以通过R4调节。本Bandgap设计采用电流模架构。

2.2 Bandgap性能参数

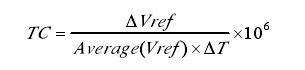

2.2.1 温度系数

温度系数(Temperature Coefficient,TC)有时也称温漂系数,单位为ppm/℃,指带隙基准电路的输出电压随温度变化的参数,它是设计带隙电压基准的重要参数之一。

式2.2

式2.2

中的ΔVref 表示在ΔT 温度变化范围内最大值与最小值的差,Average(Vref)表示ΔT 内的平均基准电压值。

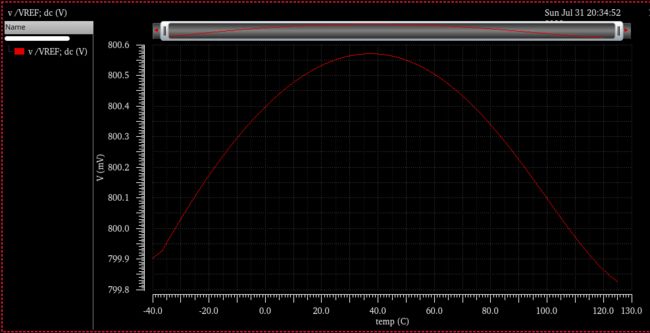

2.2.2 电源抑制PSR

电源抑制反映了当电源有波动声时,基准输出所受的影响程度。PSR 的表达式为: 式2.3

式2.3

带隙基准电路的电源抑制与其核心电路中的运放有密切的关系,在一定程度上,运放增益越大,电源抑制性能越好。

2.3 Bandgap设计

2.3.1 Bandgap核心电路

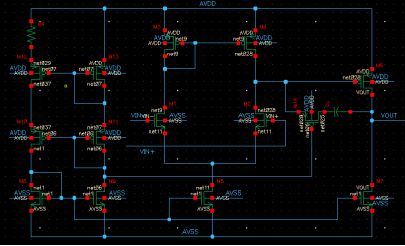

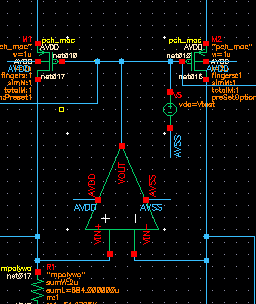

图2.3上图为BandGap电路图,下图为运放电路图

本次Bandgap设计采用最基本的电流模结构,采用上篇文章设计的运算放大器计对电压进行嵌位,运放增益约为66dB,GBW约为54MHz,相位裕度约为62°。

设计步骤如下:

- 选择n等于8,于是正温度系数电压约为54mV。

- Q1、Q2晶体管支路电流设定为1uA,R1=54mV/1uA=54kΩ,于是PTAT电流的温度系数约为3.35nA/K。

- 当T等于300K时,VBE的温度系数约为-1.5mV/K,为使常温下M1、M2电流达到零温度系数,(∂VBE/∂T)*1/R3≈-3.35nA/K,得R3≈447.7kΩ。

- 调整R4的大小可以得到不同的基准电压,为了匹配M1,2和M3,VREF最优取值为VBE,本次设计VREF取800mV。

2.3.2 自启动电路

带隙基准电路可能存在“简并”状态,换句话说就是电路中存在两个稳定点:一个是系统需要的工作模式,另一个就是零电流状态。当M1栅极处于高电平时,M1~M3均被关断,此时VREF处于低电平,为了让电路正常工作,我们需要添加启动电路,如图2.3所示:

当VREF处于低电平时,M4漏极处于高电平,M5将导通,将有电流从M1,2栅极流向M5,M1,2电位将拉低,经过正负反馈的共同调节,电路将稳定在正常工作点;当电路正常工作时,VREF处于高点平,通过调节M6、M7的宽长比进而控制其导通电压,使得M4漏极电压为低电平,M5关断,启动电路将不会影响带隙基准电路正常工作。

3. Bandgap仿真

3.1 电路参数设定

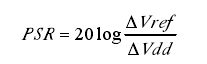

正温度系数电压

正温度系数电压理论值为87uV/K×ln8≈181uV/K,仿真值约为182.5uV/K

负温度系数电压

正度系数电压理论值为-1.5mV/K,仿真值约为-1.8mV/K与预想有一定偏差

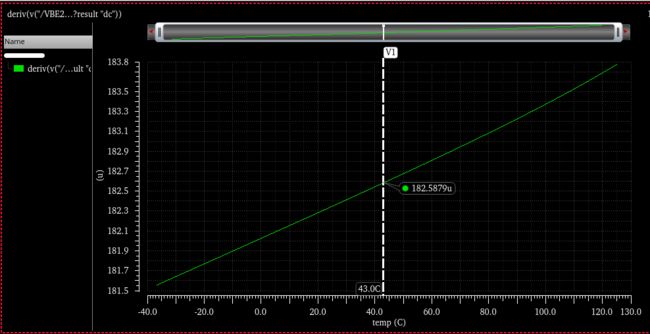

对R2、R3阻值进行参数扫描,得出其最优阻值约为558.5kΩ,R2、R3采用TSMC 65nm工艺库中的rnpolywo电阻,non-salicide电阻具有更大的电阻率,尺寸如下:

为了输出800mV电压,经仿真R4约364kΩ,尺寸如下:

M1-M3尺寸均为W=1um,L=2um,M4-M7尺寸在后续简并点仿真确定。

3.2 DC仿真

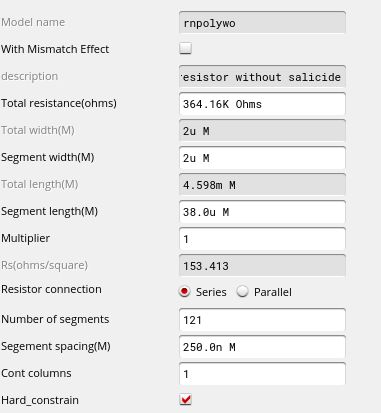

温度系数TC

VREF温度曲线如下图所示

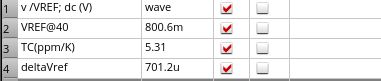

温度系数表达式为:(((ymax(v(“/VREF” ?result “dc”)) - ymin(v(“/VREF” ?result “dc”))) / average(v(“/VREF” ?result “dc”)) / 165) * 1000000),将该表达式输入到calculator,得出温度系数为5.31ppm/K

VREF@40为40℃的VREF,表达式为value(v(“/VREF” ?result “dc”) 40 ?period nil ?xName “time” ?scale '(roundDown))

deltaVref为max(VREF)-min(VREF),表达式为(ymax(v(“/VREF” ?result “dc”)) - ymin(v(“/VREF” ?result “dc”)))

简并点仿真

给带隙基准电路环路施加一个test电压,通过DC分析从0到1.8V扫描该test电压,输出test电源的电流曲线,电流为零时对应的电压值即为电路的一个工作状态,曲线与X轴的交点数即为电路的简并点数。

可见电路只有一个简并点,但为了保险起见,仍需给电路添加启动电路。

自启动仿真

设定VREF电压在500mV以上不会触发启动电路,并且在300mV以下时可以成功触发,仿真结果如下:

M4、M5尺寸设为W=1um,L=2um,M6、M7尺寸设为W=1um,L=4um。

3.3 stb仿真

在运放的输出端添加iprobe,选择stb分析并选中该iprobe

环路增益为62dB、GBW为21.02MHz,相位裕度为62°

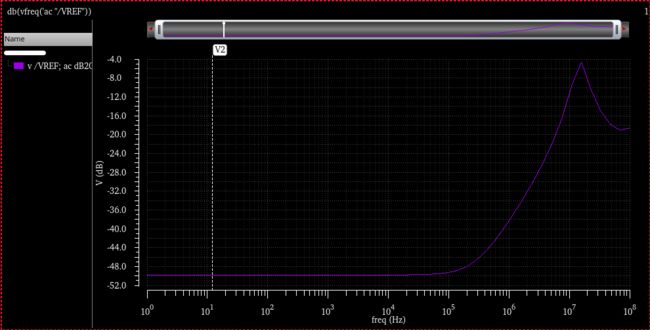

3.4 ac仿真

PSR

选择ac 分析,给AVDD的AC magnitude输入1,输出VREF

得出电源抑制PSR为49.6dB

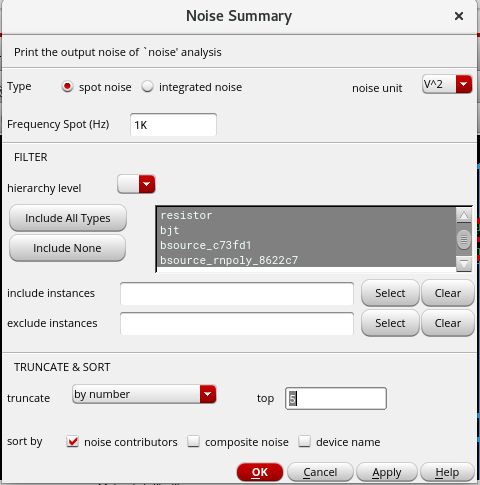

3.5 noise仿真

选择noise分析,设置Noise Parameters为1KHz

点击Noise Summary选择include all types,输出噪声前5的器件

噪声仿真结果如下:

Bandgap噪声主要集中在M1、M3的闪烁噪声,可通过增大M1、M3管减小输出噪声。

3.6 MC仿真

在ADE L仿真器中打开ADE XL,ADE L中的仿真数据将导入到ADE XL中,点击新建corner,对PVT仿真参数进行设置:

其中ss、tt、ff工艺角分别对应驱动电流(IDS)为最小值(第一个s指NMOS、第二个s指PMOS)、驱动电流为平均値、驱动电流为最大值。

工艺角设置完成后,我们选择Monte Carlo Sampling,按照下图打开Monte Carlo设置

在Numbe of Points输入50表示每个corner仿真50次,勾选好需要仿真的参数就可以开始仿真了

Monte Carlo仿真结果如下:

选择Yield,然后选择一个工艺角右击并点击Histogram,可查看该工艺脚参数仿真结果的统计分布:

1.8V 40℃ tt工艺角下,VREF@40的统计分布如下,统计数据符合高斯分布。