AI_算力入门

- 《计算机体系结构量化研究方法》

- 《硬件架构的艺术 – 数字电路设计的方法与技术》

- 《大话计算机 – 计算机系统底层架构原理极限剖析》

- 《智能计算系统》

– 本篇博客为读书笔记,源自《AI芯片技术发展》-- 唐杉 2020年

仅仅用于学习的目的~

0. 算力入门学习路线

1. AI芯片产生的背景

我们说AI芯片,一般是泛指所有用来加速AI应用,特别是基于神经网络的深度学习应用的硬件,它可以是一颗独立的芯片,也可以是芯片中的模块,其基本技术都是相关的。

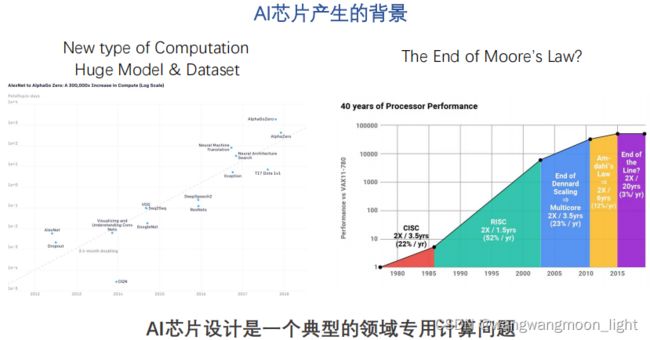

当我们讨论AI芯片出现的背景的时候,经常会看到这两张图。左边这张是openai在2018年发布的报告,简单来说,它的结论就是从2012年到2018年,我们训练神经网络模型需要的计算量呈指数型增长。这背后一方面是因为我们使用的神经网络模型的规模越来越大,另一方是要训练这样的模型需要更大的数据集。这个规律我们也称为AI的摩尔定律。

1.1 领域专用计算是需要软硬件的全栈支持

右边这张图是通用处理器的性能在40年间增长的趋势,可以看到,在近10年,处理器性能的增长已经非常缓慢了,很难达到实际的摩尔定律最初的预测。

综合来说,AI计算的需求爆炸性增长,而通用处理的处理能力很难提升,这中间就出现一个很明显的gap。

所以,一个很直接的想法就是,如果通用处理器不能满足AI计算的需求,我们是否可以设计针对AI计算的专用处理器呢?答案当然是肯定的。这也就是领域专用计算的概念。一般来说,一个领域是不是适合开发专用的处理器有两个条件,第一是这个领域的应用需求足够大,有很强的动力驱动相应的研发投入;第二是这个领域的计算模式限定在一个较小的集合,这样我们才有可能用专用硬件来对这些特定的运算进行加速。AI领域正好满足这两个条件。因此,我们说AI芯片设计是一个典型的领域专用计算问题,也就是domain specific computing。

领域计算并不是一个新的概念,这里这张图是我在2013年基于之前的一篇论文总结的,主要是描述领域专用处理器的设计方法学,这里也可以看出我们在解决一个领域专用计算问题的时候要做哪些事情。首先需要对特定领域进行建模,把需求模型化和量化,作为后续工作的评价标准。建模可能会使用特殊的语言扩展或者数据流图的形式。Domain Model是后续开发的基础,据此可以得到两个重要的中间描述,分离出指导硬件设计和生成应用软件代码的两部分信息。

硬件架构设计的主要工作是设计专用的计算引擎(Customized Computing Engine)和互连机制(Customized Interconnection)。计算引擎分为三种:专用处理器(ASP),硬件加速器(HW Accelerators)和可编程阵列(Programing fabric)。图的右半部分就是软件开发的工作和相应的工具。细节内容我就不展开讲了,感兴趣的朋友可以看看我的公众号上关于专用处理器的文章。这里我只想强调一点,就是我们设计一个专用处理器,往往需要设计新的指令集架构,编程模型,甚至是新的编程语言。这也意味着我们可能没有现成的软件工具可以使用,我们在设计和优化新的硬件的同时,必须打造新的软件工具链。只有提供全栈的软硬件,才能让用户特别是开发者利用好新硬件的能力。这个也是专用处理器设计的一个巨大挑战。

如果我们按照设计领域专用处理器的思路来考虑AI芯片,那么我们首先需要分析AI领域的计算模式特征。这里展示的是我们非常熟悉的Resnet-50神经网络模型。Resnet在图像处理任务里使用非常广泛,它需要的计算量还是比较大的。做一次正向处理大约需要3.9G的MAC。但如果我们进一步分析它需要的运算,其中绝大部分是卷积操作。这在各类CNN网络里是非常常见的。如果我们观察其它常用的神经网络模型,不难发现使用最多的操作的类型是很有限的,而需要运算量最大的基本是卷积和矩阵乘这类的操作。考虑到卷积实际上也可以转换为矩阵乘,神经网络的核心处理可以归结为GEMM类型运算。因此,加速神经网络的核心问题就是加速GEMM类运算的问题,这个也是一般AI芯片设计需要首先考虑的问题。

1.2 神经网络处理的计算需求

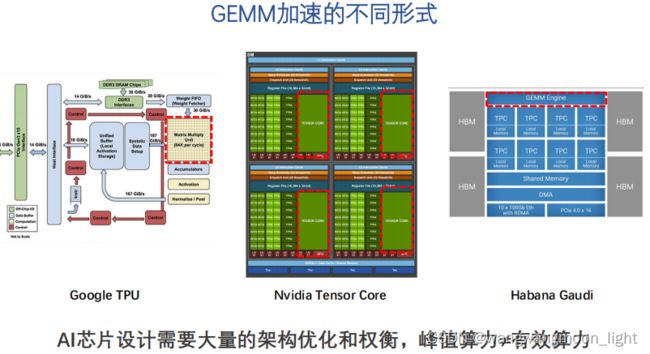

GEMM类的运算模式并不复杂,一直以来也是比较常用的运算,对它进行加速方法也有很多的研究,只是现在的需求和使用场景发生了很大变化。在实际系统中,我们需要根据不同目标来进行设计和优化,并很好的融合到整体架构当中。下面我们就看几个不同类型的GEMM加速的实现案例。

首先是Google在2017年公开的第一代TPU芯片,这可以说是一个专门加速矩阵运算的芯片。它的核心是一个256x256的矩阵乘阵列,可以同时完成6w多次的MAC操作,这种规模的MAC阵列在一般的芯片里是很难见到的。而Google很巧妙的使用了脉动阵列的架构,简化了硬件实现的难度。Google的TPU网站上有很清楚的动态展示,对脉动阵列感兴趣的朋友可以看看。当然,在实际应用中要充分利用这么大的阵列也不容易,到后面几代TPU,就把阵列分成了两块,每块的规模减少了一半。另外,对于不适合矩阵乘阵列的操作,TPU里面设计了专门的加速器,以保证整个网络的效率。TPU的指令集也很简单,主要就是Load,Store和计算,基本就是保证矩阵乘阵列的工作。

Nvidia为加速GEMM在GPU中设计了新的Tensor Core和相应的矩阵运算指令。第一代Tensor core主要执行4X4矩阵的运算,最新发布的第三代tensor core规模大一点,但相对TPU的MAC阵列,粒度细很多,同时Tensor Core和GPU架构紧密融合。他的优势是使用比较灵活,比较容易兼容CUDA编程模型。对于非GEMM类型的操作,则可以在GPU传统的计算单元中处理。但如果单纯看GEMM加速的效率,在有些情况下比规模更大的GEMM引擎要差一些。

1.3 GEMM加速的不同形式

Habana则是在DSP的基础上增加了GEMM引擎,这也是一种比较常见的AI芯片架构方式,它也是考虑到了灵活性和效率的平衡。

当然,对GEMM的加速效果是受很多因素影响的。首先要有大量的运算单元,这个相对比较容易,但即使有了大量的运算单元,如果数据不能有效的供给到GEMM引擎,则它理论上计算能力再强也发挥不出来。这也是为什么我们经常看到AI芯片宣传的峰值运算能力很强,但跑实际网络的有效算力就差了很多。此外,还有很多需要做架构优化和权衡的问题。比如可编程性。值得一提的是,Habana一直强调自己是从做硬件之前就开始做软件工具的。从实际展示的结果来看,Habana的芯片利用率还是比较高的,这个应该是硬件架构比较平衡,软件工具比较完善才可能做到的。

1.4 更多特殊的架构

下面我们看一下华为在去年的Hot chips会议上展示的达芬奇AI处理器架构,它吸取了过去几年AI硬件加速的经验,融合向量,标量和矩阵的的运算。3D Cube:161616三维弹性立方体,可在一个时钟周期内完成4096个FP16 MAC运算。而这个核通过不同的配置,可以作为 几十毫瓦的IP到支持几百瓦的芯片,的不同场景,比如高能效的Ascend 310到算力最强的Ascend 910。应该说达芬奇架构代表了对现阶段AI硬件加速的比较一致的认识,大家有兴趣也可以去看一下《昇腾AI处理器架构与编程》这本书,有很多详细的介绍。

当然,这几年AI芯片的热潮也给我们带来一些很有意思的,比较特殊的架构。比如,Grophcore的IPU是一个大规模并行,同构众核架构。最基本的硬件处理单元是IPU-Core,它是一个SMT多线程处理器,可以同时跑6个线程,更接近多线程CPU。芯片上有一千多个小的这种通用处理器核。同时,芯片没有外部存储,而是实现了300M左右的片上存储,这个也是很少见的。Graphcore还设计了一个相当简洁的多核通信和同步机制,大大简化的硬件设计和多芯片扩展的难度。而另外一个更激进的架构是Cerenbras的wafer级芯片,也就是整个wafer产出一颗芯片,可以说是工程上的奇迹。不过,目前看来这个芯片还是主要用在非常专用的场景。我们当然也很希望未来看到更多有意思的架构出现。

如果总结一下这几年AI计算加速在产业的发展,简单来说就是无芯片不AI。从云到边到端的各种场景都需要AI运算能力,因此也都需要AI加速。但是在不同的场景下,对AI加速的需求又有很大差别。比如云端的训练场景,需要高精度,高吞吐率,需要处理很大的数据集,因此还需要很大的存储。同时,软硬件必须有很强的扩展能力,支持大规模集群的训练模式。而云端推理场景的需求又有一些差异,高吞吐和低时延的要求并存。如果看端设备,从可穿戴设备,到手机,到自动驾驶,需求和应用场景的限制差异很大,不同场景可能需要不同的芯片来支持。端设备中,很少会有独立的AI芯片,AI加速主要是SoC中的一个IP。另外一个很有前景的应用场景是边缘服务器,这个场景可能是AI和5G最好的一个结合点。除了传统的各种各样处理器,包括CPU,会强化AI处理能力之外,在网络芯片,存储芯片,或者传感器芯片里也有增加AI处理的尝试,这样做的好处是让AI处理尽量离数据更近,可以缓解大量数据搬运的需求。

2 软件栈

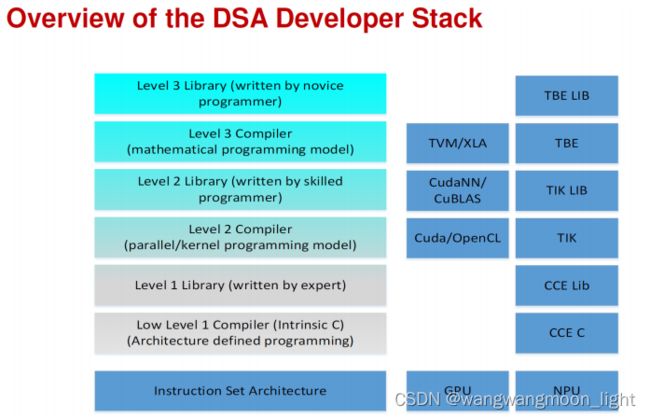

下面我们来看看软件栈方面的情况。我们前面已经强调了专用处理器的软件工具链方面的挑战和重要性,这里还是看看华为在hotchips上介绍的例子。对于领域专用处理器来说,其用户往往也是开发者。这里将用户分成了不同的情况。对于专家级的用户,你需要开发更低层次的编程接口,用户自己会做更多的优化工作。而对于普通用户,只会在抽象层次比较高的编程接口和模型上工作,大部分的优化工作需要工具链中的编译器来完成,或者通过优化后的库来支持,不过这两类工作的挑战都不小。

这个例子里面中间一列,我们看到目前业界应用最多的软件栈。硬件基于Nvidia GPU,软件是基于CUDA。正好Nvidia刚刚发布了新的AI软硬件产品,我们不妨展开来看一下。

首先是Nvidia新推出的A100,给AI硬件加速又设定了新的标杆。A100是7nm工艺,使用HBM2存储器接口,3D封装,整体性能有大幅提升。具体来说,Tensor Core支持更多的数据类型,特别是AI中常用的数据类型,支持固定结构的2:4稀疏化处理。FP16/BF16的峰值处理能力是312TFLOPS,INT8的峰值处理能力是624TOPS,如果是稀疏处理的情况,则最高性能翻倍。近几年很多AI芯片初创公司都说自己的芯片硬件性能比Nvidia GPU高几倍,不过现在看来,即使单看硬件,A100的指标也是最强的。

在A100的基础上,Nvidia的整个硬件产品线也做了升级,从显卡到云服务器到边缘服务器到自动驾驶和智能机器平台,非常完整。

我们如果来看软件工具和生态,Nvidia更是绝对的标杆,这方面其它厂商都有比较大的差距。本次黄教主展示的数据是有180万的开发者使用Nvidia的软件生态。首先是积累十多年的CUDA,在这之上又包装了一层CUDA-X,还整合了包括AI在内的各种领域功能,甚至包括对5G虚拟接入网的支持。对于不同类型的应用,不同类型的用户,都可以提供比较完善的支持,而且这套生态还是基于一套非常成熟和一致的底层架构,确实是非常厉害。我之前也整理了一个CUDA生态比较详细的信息图,有兴趣的朋友可以到我的公众号看看。

在这次的厨房展示中,黄教主说的最多的一个词可能是end-to-end,也就是端到端的支持,还给出了很多实例,比如对于推荐系统和交互是语音结合自然语言处理这类的系统都给出了专门的解决方案。而Nvidia AI就是一个端到端的软硬件加速方案,从大数据处理,到AI的training,再到inference,可以说把Nvidia的生态优势发挥到了极致。其中对于推荐系统,Nvidia专门推出了一个Merlin框架,解决用GPU加速推荐系统的问题。对这个问题感兴趣的朋友,可以看看“如何加速推荐系统?这是个高价值问题”。

2.1 编译器

下面我们讨论一下在软件栈里面非常重要的编译器。这张图来自Facebook开发的GLOW编译器,这里主要用来展示一下一般来说AI领域的编译器是做什么的。首先,和传统的编译器类似,AI编译器也是在不同的中间表示,也就是IR之间,进行转换和优化的工具。但它的输入一般不是编程语言而是神经网络模型,比如是这里的计算图的形式,这个计算图可能是来自上层的机器学习框架。AI编译器也可以在图的层次进行一些优化,然后转换为层次更低的IR,IR可能有多个层次,编译器就是逐渐的降低IR的层次,最终生成硬件能够运行的代码。我们可以看到,AI编译器的IR会有AI运算的特点,比如AI中常用的算子,conv,relu,pooling等等。此外AI编译器还需要使用一些新的优化技术和算法来优化计算图或者算子的实现。

目前的开源AI编译器项目也非常活跃,这其中最有代表性的两个是TVM和Google的MLIR。这两个编译器也都融入了很多先进的思想,从一般的编译器功能扩展到软硬件协同设计的概念。比如TVM就包括了一个开源的硬件加速器VTA,展示了从编译器到硬件加速器联合优化的初步尝试。而AutoTVM也是一个自动的编译优化工具。

而MLIR也明确说明了它是一个开源的程序优化框架。MLIR的第一个重要卖点就是多层次IR。原因也很简单,由于优化目标和方法的不同,单层或者很少的IR层次无法满足要求。当然,支持多层IR也不是说说这么简单,MLIR里支持IR的自由扩展使用了Dialect的设计,并提供了定义和操作Dialect的方法和基本的工具。这正好也是MLIR的第二个主要卖点,也就是提供了比较丰富的基础设施支持。MLIR充分利用了LLVM的经验和优化算法,也希望兼容各种现有的优化手段。对需要打造自己的编译器的开发者来说,可以简化很多工作。MLIR项目的理念非常好,有可能解决很多困扰我们的问题,非常值得大家关注。另外,值得一提的是,现在的AI编译器和AI框架并没有一个非常清晰的边界,未来也会是一个相互融合的趋势,当然总的目标都是更高效的执行AI运算。

3 发展趋势

到这里,我们基本看到了近几年AI芯片在硬件和软件两条线上的最新的进展。下面我们来聊聊AIi芯片的未来。

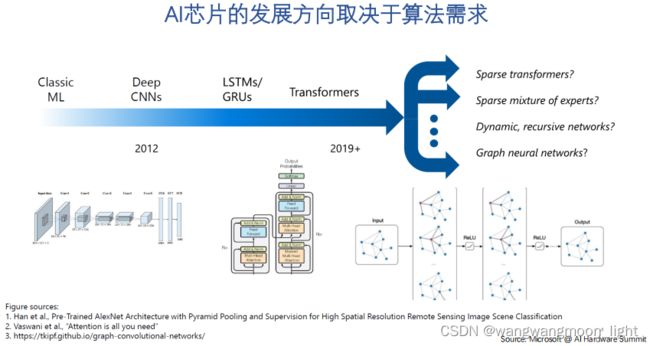

AI芯片的本质是一个领域专用架构,那么它发展的方向是完全取决于AI领域算法和应用发展的方向。2012年的Alexnet到2018年的Transformer,其核心计算还是稠密矩阵运算,这也是目前AI芯片支持的最好的计算模式。但在现在这个时间点,AI算法的走向还不是很清晰,未来每个分支的计算需求可能相差很远。在出现一个统一的模型之前,也很难形成一个统一的AI芯片架构。

除了AI硬件越来越强,神经网络模型也在进化。OpenAI正好在最近又发布了一个报告,是说从2012年到现在,大家设计的神经网络模型的效率越来越高,训练一个具有同等精度的模型的计算代价减少了大约44倍,也就是说现在设计的很好的小模型完全可以达到之前大模型的精度。当然,这并不是说我们就不需要硬件加速,这里毕竟只是有限的场景。这个报告还有一些其它的有趣信息,比如从17年开始,训练一个resnet50,按美元计算的成本下降了184x,这个数据应该是Google TPU实现的。这也说明,这几年专用硬件加速技术的发展,对提高AI计算的效率做出了很大的贡献。

当然,在一些成熟AI算法不断优化执行效率的同时,新的突破还是往往需要更多的数据和更大的模型,比如最近的GPT-3。同时,AI应用场景也越来越广,这两个例子是最近比较热的话题,把AI用于芯片设计和把AI用于5G的信号处理。因此,AI发展对算力和算力效率的需求在可预见的未来不会减弱。

要说技术趋势,学术研究应该是最好的风向标。最近我们做了一件事情,整理了一些近几年体系结构顶会中的论文(ISCA,ASPLOS,MICRO,HPCA),对和AI相关的研究加了些标签,形成了一个AI芯片相关论文的列表,方便大家查询。同时我们也分析了一下相关研究的趋势,AI芯片架构方面的研究从14年开始,到17年都非常活跃,有很多创新的工作。近两年,相关研究还是很多,但在架构层面已经很难看到大的创新了,这也是AI硬件加速技术走向成熟的正常表现。未来可能更多的创新会来自和电路和器件级技术的结合,比如存内计算,类脑计算;或者是针对特殊的计算模式或者新模型,比如稀疏化计算和近似计算,对图网络的加速;或者是针对数据而不是模型的特征来优化架构,等等。另外,软件和编译器层面的技术优化还是很大空间,而跨边界的优化技术和方法学也是值得关注的方向。

3.1 架构研究的趋势

另外一个有趣的问题是,如果算法不发生大的变化,按照现在AI加速的主要方法和半导体技术发展的趋势,我们有可能在不远的将来会碰到数字电路的极限。比如IBM就提出,1到10TFlops/W基本就是数字电路实现目前的深度学习计算的效率极限,在往后则要靠近似计算,模拟计算,甚至是材料上的创新了。所以我们也看到很多初创公司在做这个方向的尝试。

除了领域专用计算方法之外,另一个可能延续摩尔定律的技术是Chiplet,现在一种比较有意思的中文翻译是“芯粒”,芯片的芯,颗粒的粒。简单来说,就是基于先进的封装技术,可以把多个芯片的裸片封装在一起,通过这种模式而不是单纯靠芯片工艺的升级,来提升整体的性能。这些裸片可以是相同功能的算力扩展,也可以是不同功能,不同架构,甚至不同工艺的裸片的组合。这里给出的是Nvidia在Hotchips上展示的研究,通过chiplet技术实现一个可伸缩的deep learning加速器。这个话题很大,想象空间也很大,给我们带来的可能不止是技术上的进步,还可能是芯片设计模式和方法上的改变,甚至商业模式上的创新。时间关系就不展开了,有兴趣的朋友也可以看看我之前分析的文章。