第三节 神经网络起源-感知机

或许我们对“神经网络”这个词早已经不陌生,但是有没有考虑过它的起源呢?本文将介绍感知机(perceptron)这一算法。感知机是由美国学者FrankRosenblatt在1957年提出来的。那为何我们要回过头来看年代久远的感知机呢?原因很简单,感知机作为神经网络(深度学习)的起源算法,了解其构造,是学习通向神经网络和深度学习的一种重要思想。

1感知机是什么

感知机可以接收多个输入信号,然后输出一个信号,这里可以先来看一张图,其中 ![]() 和

和 ![]() 代表输入信号,图中的圆圈O代表神经元或者节点。当输入信号被送往神经元时,会分别被乘以固定的权重值

代表输入信号,图中的圆圈O代表神经元或者节点。当输入信号被送往神经元时,会分别被乘以固定的权重值 ![]() 和

和 ![]() ,只有当这个总和超过了某个界限值时,才会输出1。这也称为“神经元被激活” 。这里将这个界限值称为阈值,用符号θ表示。

,只有当这个总和超过了某个界限值时,才会输出1。这也称为“神经元被激活” 。这里将这个界限值称为阈值,用符号θ表示。

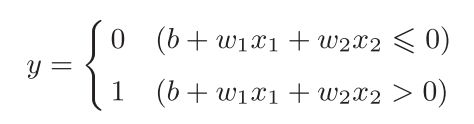

上述感知机的数学表达式如下:

而感知机对应的每个输入型号都有各自的权重,这些权重控制着各个信号,权重越大,对应该权重的信号的重要性就越高。

2 简单的逻辑电路

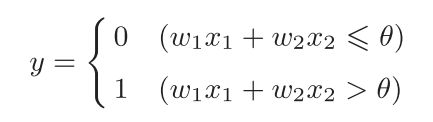

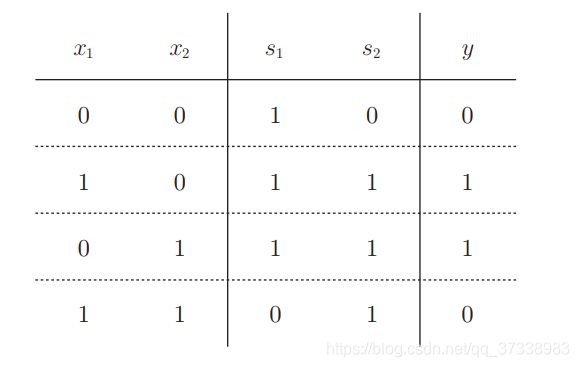

感知机可以用于解决简单的逻辑电路问题,与门是有两个输入和一个输出的门电路,其真值表入下图所示:

由上表,我们可以得出与门的四种情况,只有两个输入都为1时,输出才为1,其余的情况都为0。当我们用感知机来尝试解决这个问题时,就需要确定可以满足真值表中的![]() 、

、![]() 和 θ 的值。但实际上满足真值表的条件的参数可以有无数多个,例如当我们选取(0.5, 0.6, 0.8)时,代入感知机公式中,可以得到上面真值表的结果。即设定好参数后,只有当

和 θ 的值。但实际上满足真值表的条件的参数可以有无数多个,例如当我们选取(0.5, 0.6, 0.8)时,代入感知机公式中,可以得到上面真值表的结果。即设定好参数后,只有当![]() 和

和 ![]() 的值同事为1时,信号的加权总和才会超过给定的阈值θ

的值同事为1时,信号的加权总和才会超过给定的阈值θ

同样,在逻辑电路中,存在着另外两种简单的逻辑电路,与非门和或门:

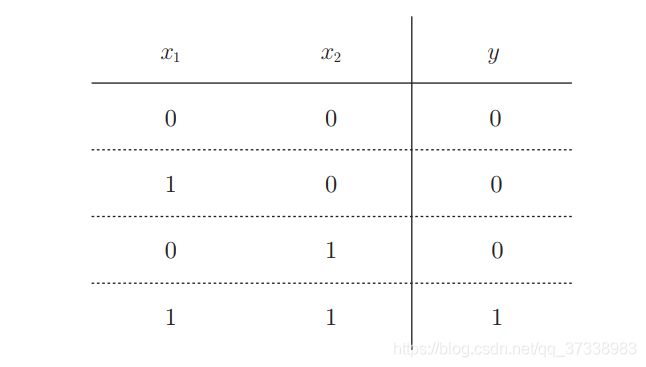

先来谈一谈与非门,顾名思义,与非门和与门一定有着某种关系,其真值表如下:

从表中,我们可以看出与非门和与门的输出结果正好相反,例如与门输出为A,则与非门输出就为 !A

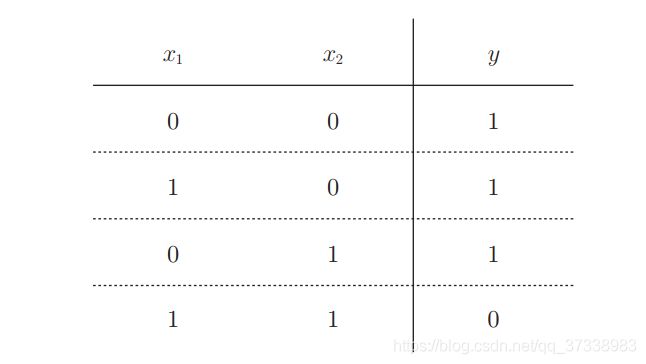

再来看一下或门,或门是只需要有一个输入信号为1时,输出就为1,其真值表如下:

从上面的三种逻辑电路的介绍,可以得知与门、与非门、或门的感知机构造是一样的。实际上, 3个门电路只有参数的值(权重和阈值)不同。也就是说,相同构造的感知机,只需通过适当地调整参数的值,就可以用于计算与门、与非门和或门。

3.感知机的实现

在实现之前,先将文章开头的感知机数学表达式换成另一种形式,这里将θ换成-b, 然后将其移动到不等式左边,得到:

虽然改变后的表达式形式上不一样,但是它们所表达的内容是完全相同的。这里的b(bias)称之为偏置。我们对改进后的感知机进行程序编写如下:

# 与门, 导入权重和偏置

def biasAND(x1, x2):

x = np.array([x1, x2])

w = np.array([0.5, 0.5])

bias = -0.7

tmp = np.sum(w*x) + bias

if tmp <= 0:

return 0

else:

return 1

print('与门:',biasAND(0, 0), biasAND(0, 1), biasAND(1, 0), biasAND(1, 1)) # 0, 0, 0, 1

与非门:

#与非门

def biasNAND(x1, x2):

x = np.array([x1, x2])

w = np.array([-0.5, -0.5])

bias = 0.7

tmp = np.sum(w*x) + bias

if tmp <= 0:

return 0

else:

return 1

print('与非门:',biasNAND(0, 0), biasNAND(0, 1), biasNAND(1, 0), biasNAND(1, 1))# 1,1,1,0或门:

def biasOR(x1, x2):

x = np.array([x1, x2])

w = np.array([0.5, 0.5])

bias = -0.2

tmp = np.sum(w*x) + bias

if tmp <= 0:

return 0

else:

return 1

print('或门:',biasOR(0, 0), biasOR(0, 1), biasOR(1, 0), biasOR(1, 1)) # 0, 1, 1,14.感知机的局限性

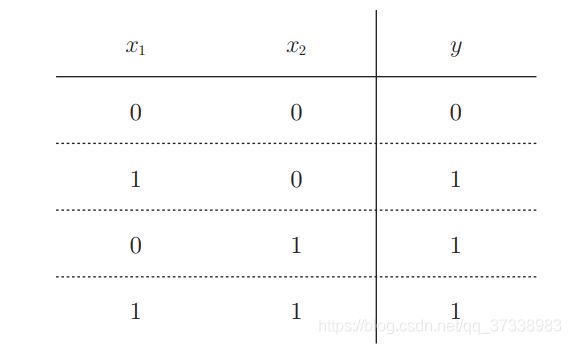

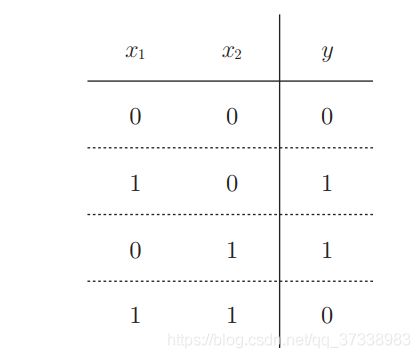

由上面可以知道,使用感知机可以实现与门、与非门、或门三种逻辑电路。在逻辑电路中还有另外一种简单的逻辑电路,异或门,其真值表如下所示:

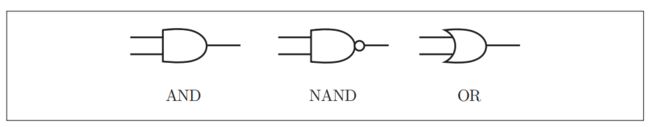

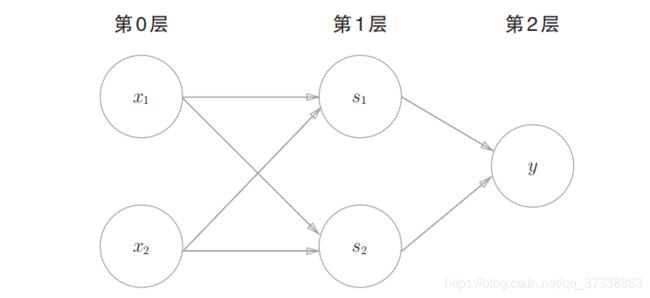

观察上面的表格,我们不难发现,无论我们的权重和偏置值如何取值,都无法利用感知机直观的实现异或门的结果。所以这里便引出了一个多层感知机的概念,虽然感知机不能直接解决异或门计算问题, 但实际上,感知机的绝妙之处在于它可以“叠加层”,通过不同的组合来解决这个问题,下面将与门、与非门和或门表达如下:

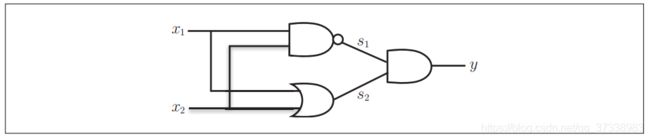

通过这三种电路的组合叠加就可以实现对异或门的实现:

异或门是一种多层结构的神经网络。这里,将最左边的一列称为第0层,中间的一列称为第1层,最右边的一列称为第2层。现在再来观察一下真值表:

其结果完全满足异或门的输出要求。对异或门编码如下:

# 异或门

def XOR(x1, x2):

s1 = biasNAND(x1, x2)

s2 = biasOR(x1, x2)

y = AND(s1, s2)

return y

print('异或门:',XOR(0, 0), XOR(0, 1), XOR(1, 0), XOR(1, 1)) # 0, 1, 1, 0叠加了多层的感知机也称为多层感知机(multi-layered perceptron),其结构图如下:

5 总结

本文主要简述了神经网络的起源,感知机(perceptron),对几种逻辑门电路进行介绍,使用感知机解决了与门、与非门和或门三种逻辑电路的计算,并对感知机的局限性进行分析,最终利用感知机多层叠加实现异或门的计算问题。