ARM处理器中断处理机制

一、异常

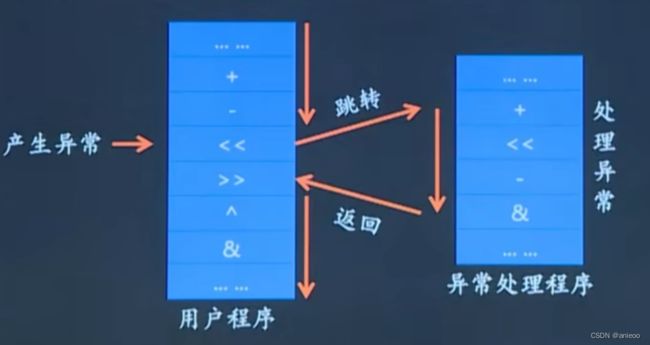

概念:处理器在正常执行程序的过程中可能会遇到一些不正常的事件发生,这时处理器就要将当前的程序暂停下来去处理这个异常的事件,当异常事件处理完成之后再返回被异常打断的点继续执行程序。

不同的处理器对异常的处理机制在宏观上是相同的,但是在具体的实现机制上有所不同:比如处理器在遇到异常后会产生的动作、如何能跳转到异常处理程序、处理完异常后又是如何返回原程序等等,这些细节的实现称为异常处理机制。

二、异常源

概念:导致异常产生的事件称为异常源。

其中会导致ARM处理器异常事件的异常源如下:

| FIQ | 快速中断请求引脚有效 |

| IRQ | 外部中断请求引脚有效 |

| Reset | 复位电平有效 |

| Software Interrupt | 执行swi指令 |

| Data Abort | 数据终止 |

| Prefetch Abort | 指令预存终止 |

| Undefined Instruction | 遇到不能处理的指令 |

FIQ、IRQ:ARM中断处理器可以配置与中断控制器(stm32:NVIC、I.MX6ULL:GIC)相连的某个中断输入引脚是FIQ还是IRQ,FIQ比IRQ有更高优先级,响应的速度更快,IRQ模式可以被FIQ模式中断,但IRQ不能中断FIQ模式;其次对于FIQ模式需要尽快处理,尽快结束。

Reset:当处理器的复位引脚有效时,系统产生复位异常中断,程序跳转到复位异常中断处理程序处执行。

Software Interrupt:与硬件中断相对应,由用户定义的软件触发的中断请求。比如linux系统中系统调用read()函数就是利用软中断陷入内核。

Data Abort:如果数据访问指令的目标地址不存在,或者该地址不允许当前指令访问,处理器产生数据访问中止异常中断。比如说当地址是一个野指针的时候就会触发。

Prefetch Abort :如果处理器预取的指令的地址不存在,或者该地址不允许当前指令访问,当该被预取的指令执行时,处理器产生指令预取中止异常中断。

Undefined Instruction:当ARM处理器或者是系统中的协处理器认为当前指令未定义时,产生未定义的指令异常中断。

三、ARM异常模式

ARM处理器通常有7种基本工作模式,(cotex-A系列新增了Monitor和Hyp模式所以有9种),其中5个属于异常模式,即ARM处理器遇到异常后会切换成对应的一场模式。

| 异常源 | FIQ | IRQ | Reset SWI |

Data Abort Prefetch Abort |

Undefined Instruction |

| 异常模式 | FIQ | IRQ | SVC | Abort | Undef |

四、ARM异常响应

ARM处理器产生异常后的动作(自动完成)

① 备份CPSR(程序状态寄存器)中的内容到SPSR

② 修改CPSR的值

2.1.禁止相应的中断

2.2.进入相应的异常模式

2.3 进入ARM状态

③ 保存返回地址到LR

④ 跳转到异常向量表对应的位置

五、ARM异常向量表

异常向量表是内存中的一段代码(一共32个字节,平分成8份)。

表中的每个异常源分配了四个字节的存储空间。

遇到异常后处理器自动跳转到表中对应的地址(对于Armv7架构,即异常向量表存储的是一个跳转指令)。

因为异常向量表空间有限,所以一般不会在这写异常处理程序,而是在对应的位置写一条异常跳转指令使其跳转到异常处理程序的入口。

六、 异常返回

ARM异常返回动作(自己编写)

① 将SPSR寄存器的值恢复到CPSR,回复程序原来的状态

② 将LR的值存到PC,使程序跳转回被打断的地方继续运行。