FPGA设计显示电压值

随着电子技术的飞速发展,数字电压表在电压测量领域的作用显得更加重要,本次实训课程旨在掌握基于FPGA的数字电压表设计。本次设计在Quartus

II 环境下进行,以Verilog HDL语言实现分频、模数转换、数码管显示、led灯蜂鸣器声光报警等系统所需模块。利用层次化、模块化的开发的方法完成设计,并进行波形仿真。利用SignalTap II完成系统的在线调试与验证。

设计内容:

(1)可以动态采集开发板上数字电位器调节产生的电压,电压采集精度为1%;

(2)具有复位按键,系统具有整体复位功能;;

(3)数码管显示采集到的电压值,显示内容为Ux.xxx 共计5个字符,其中U为数码管0最上面那行不亮,整数位1位,小数位3位,后面有小数点;

(4)系统具有上下阈值报警功能,阈值可以自己设定,便于修改。测量电压值超过阈值上限,则蜂鸣器响,4个led闪烁,闪烁频率4Hz;测量电压值超过阈值下限,则蜂鸣器响,4个led闪烁,闪烁频率2Hz;

超过阈值上限与超过阈值下限蜂鸣器驱动频率要有明显区分(超过阈值上限蜂鸣器声音比超过阈值下限急促);

(5)可以自行发挥,增加自己认为有必要增加的功能,比如自动调节量程、带时钟现实的数字电压表等。

设计要求:

(1)系统功能分析,分模块层次化设计,实现系统功能的方案设计;

(2)根据任务要求确定状态关系,如有需要画出状态转换图;

(3)编写各功能模块 Verilog HDL语言程序;

(4)对各功能模块进行编译、综合、仿真和验证;

(5)整个系统进行编译、

综合、仿真和验证;

(6)利用SignalTap II完成系统的在线调试与验证

(7)在FPGA实验开发系统试验板上进行硬件验证;

(8)完成实训报告。

实训题目具体设计过程记录(图、表或程序等)

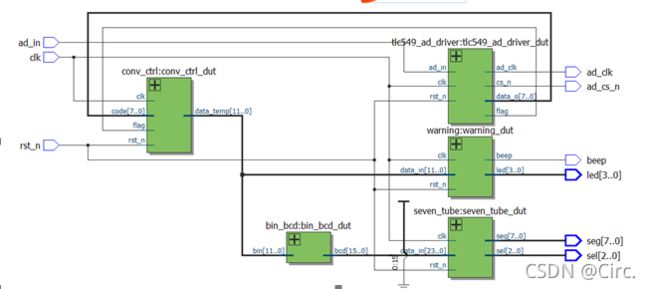

顶层功能设计与描述

将模块连接在一起,tcl_549采集8位信号通过AD转换将数据传给conv_crtl,根据公式转换成电压值,将8位数据转换成12位数据 ,然后同时传给后边的报警模块和bin_bcd模块,warning模块根据判断传过来的数据是否在规定的范围之内,如果在范围只能,灯和蜂鸣器都不工作,如果超出范围就发出警报。bin_bcd模块进行二进制转bcd码变成数码管可以识别的形式,将数值显示在seven_tube数码管上。

2、分功能模块设计与描述(涉及到状态转移表、分段式状态转移列表、流程图的也需要进行描述,分功能模块需要有波形仿真图,波形仿真图需要进行简单说明)

2.1.tlc_549_ad_driver模块

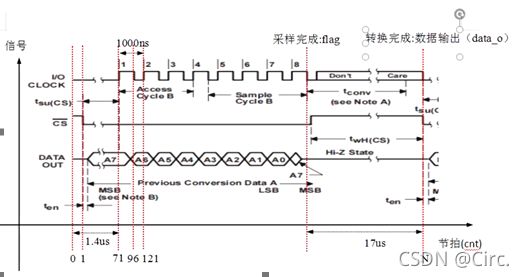

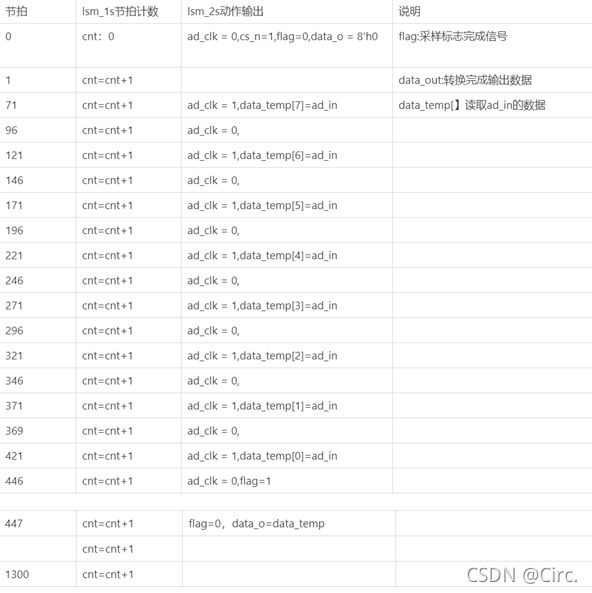

根据数据手册上cs_n拉低1.4微秒(1/50mhz=20ns,2070节拍)开始计数,所以节拍从71开始+25(1.1MHZ≈1MHZ 1/1_000hz=1000ns)(2025*2=1000ns是一个小周期)),cnt+1,上升沿采集信号,下降沿输出信号。同时在446节拍时采样结束,在447节拍时输出采样数据。477-1300节拍对应传输数据时间17微秒。

2.2 conv_ctrl模块

输入的8位数据code通过公式Vref(基准电压) * code / 256= data_temp 得到12位数据data_temp。

bin_bcd模块进行二进制转bcd码变成数码管可以识别的形式。

2.4

seven_tube模块

根据bin_bcd模块进行转换后得到的对应的BCD码在数码管上显示出来。Sel为位选,seg为段选,通过3-8译码器选择位数,根据手册控制seg使显示字符。

2.5 warning模块

12位数据传入警告模块中,将12位的数据进行判断是否在控制的范围之内,如果在范围之内,则flag1和flag2都为0,如果大于最大值,输出信号flag1=1,小于最小值输出信号flag2=1,由这两个信,控制后边的蜂鸣器模块中和灯模块,当其大于1000时,flag1=1,led闪烁频率为4Hz,并且蜂鸣器beep开始工作,频率为5kHz;当其小于900时,flag2=1,led闪烁频率为2Hz,并且蜂鸣器beep开始工作,频率为10kHz;

运行测试结果分析(SignalTap II完成系统的在线调试与验证并截图说明)

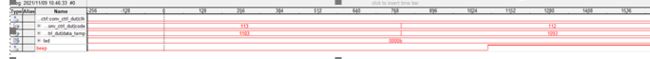

当code为十进制113时,data_temp为113 * 2500 / 256 =1104,高于上限阈值1000,故warning模块反应,led开始闪烁,同时蜂鸣器开始工作。

总结及分析

本次实训,我们熟悉了quartusII软件编程环境,学会了如何使用verilog hdl语言编写程序,这几天我们学学习了如何建立文件夹能让我们提高效率,还有如何编写测试程序,同时我们学习了模块代码的编写,包括计数器的编写,分频模块的编写,电压转换模块代码的书写,状态机的编写和数码管的设计,以及利用线性序列机的思想对tcl549芯片进行ad转换,还有bcd转化模块代码的书写,然后把我们前几天学习的模块连接起来,tcl_549采集8位信号通过AD转换将数据传给conv_crtl,根据公式转换成电压值,将8位数据转换成12位数据 ,然后同时传给后边的报警模块和bin_bcd模块,warning模块根据判断传过来的数据是否在规定的范围之内,如果在范围只能,灯和蜂鸣器都不工作,如果超出范围就发出警报。bin_bcd模块进行二进制转bcd码变成数码管可以识别的形式,将数值显示在seven_tube数码管上。

通过控制灯闪烁次数的范围,控制flag信号的输出状态,从而达到控制灯亮灭的状态。

本次实训,我们对FPGA有了一个大概的了解,FPGA设计的主要难点是熟悉硬件系统以及内部资源,保证设计的语言能够实现元器件之间的有效配合,提高程序的可读性以及利用率。我们的动手能力大大提高,不仅仅是停留在理论知识层面上,这对我们以后找工作打下了基础。