- 【iOS】MVC设计模式

Magnetic_h

iosmvc设计模式objective-c学习ui

MVC前言如何设计一个程序的结构,这是一门专门的学问,叫做"架构模式"(architecturalpattern),属于编程的方法论。MVC模式就是架构模式的一种。它是Apple官方推荐的App开发架构,也是一般开发者最先遇到、最经典的架构。MVC各层controller层Controller/ViewController/VC(控制器)负责协调Model和View,处理大部分逻辑它将数据从Mod

- 微服务下功能权限与数据权限的设计与实现

nbsaas-boot

微服务java架构

在微服务架构下,系统的功能权限和数据权限控制显得尤为重要。随着系统规模的扩大和微服务数量的增加,如何保证不同用户和服务之间的访问权限准确、细粒度地控制,成为设计安全策略的关键。本文将讨论如何在微服务体系中设计和实现功能权限与数据权限控制。1.功能权限与数据权限的定义功能权限:指用户或系统角色对特定功能的访问权限。通常是某个用户角色能否执行某个操作,比如查看订单、创建订单、修改用户资料等。数据权限:

- 腾讯云技术深度探索:构建高效云原生微服务架构

我的运维人生

云原生架构腾讯云运维开发技术共享

腾讯云技术深度探索:构建高效云原生微服务架构在当今快速发展的技术环境中,云原生技术已成为企业数字化转型的关键驱动力。腾讯云作为行业领先的云服务提供商,不断推出创新的产品和技术,助力企业构建高效、可扩展的云原生微服务架构。本文将深入探讨腾讯云在微服务领域的最新进展,并通过一个实际案例展示如何在腾讯云平台上构建云原生应用。腾讯云微服务架构概览腾讯云微服务架构基于云原生理念,旨在帮助企业快速实现应用的容

- 关于提高复杂业务逻辑代码可读性的思考

编程经验分享

开发经验java数据库开发语言

目录前言需求场景常规写法拆分方法领域对象总结前言实际工作中大部分时间都是在写业务逻辑,一般都是三层架构,表示层(Controller)接收客户端请求,并对入参做检验,业务逻辑层(Service)负责处理业务逻辑,一般开发都是在这一层中写具体的业务逻辑。数据访问层(Dao)是直接和数据库交互的,用于查数据给业务逻辑层,或者是将业务逻辑层处理后的数据写入数据库。简单的增删改查接口不用多说,基本上写好一

- 18、架构-可观测性之聚合度量

大树~~

架构javapython后端架构

聚合度量聚合度量是指对系统运行时产生的各种指标数据进行收集、聚合和分析,以了解系统的健康状况和性能表现。聚合度量是可观测性的关键组成部分,通过对度量数据的分析,可以及时发现系统中的异常和瓶颈。以下是对聚合度量各个方面的详细解析,并结合具体的数据案例和技术支撑。指标收集收集系统运行时产生的各种指标数据是聚合度量的基础。常见的指标包括CPU使用率、内存使用率、请求处理时间、请求数、错误率等。以下是指标

- BART&BERT

Ambition_LAO

深度学习

BART和BERT都是基于Transformer架构的预训练语言模型。模型架构:BERT(BidirectionalEncoderRepresentationsfromTransformers)主要是一个编码器(Encoder)模型,它使用了Transformer的编码器部分来处理输入的文本,并生成文本的表示。BERT特别擅长理解语言的上下文,因为它在预训练阶段使用了掩码语言模型(MLM)任务,即

- 系统架构设计师 需求分析篇二

AmHardy

软件架构设计师系统架构需求分析面向对象分析分析模型UML和SysML

面向对象分析方法1.用例模型构建用例模型一般需要经历4个阶段:识别参与者:识别与系统交互的所有事物。合并需求获得用例:将需求分配给予其相关的参与者。细化用例描述:详细描述每个用例的功能。调整用例模型:优化用例之间的关系和结构,前三个阶段是必需的。2.用例图的三元素参与者:使用系统的用户或其他外部系统和设备。用例:系统所提供的服务。通信关联:参与者和用例之间的关系,或用例与用例之间的关系。3.识别参

- Java爬虫框架(一)--架构设计

狼图腾-狼之传说

java框架java任务html解析器存储电子商务

一、架构图那里搜网络爬虫框架主要针对电子商务网站进行数据爬取,分析,存储,索引。爬虫:爬虫负责爬取,解析,处理电子商务网站的网页的内容数据库:存储商品信息索引:商品的全文搜索索引Task队列:需要爬取的网页列表Visited表:已经爬取过的网页列表爬虫监控平台:web平台可以启动,停止爬虫,管理爬虫,task队列,visited表。二、爬虫1.流程1)Scheduler启动爬虫器,TaskMast

- Armv8.3 体系结构扩展--原文版

代码改变世界ctw

ARM-TEE-Androidarmv8嵌入式arm架构安全架构芯片TrustzoneSecureboot

快速链接:.ARMv8/ARMv9架构入门到精通-[目录]付费专栏-付费课程【购买须知】:个人博客笔记导读目录(全部)TheArmv8.3architectureextensionTheArmv8.3architectureextensionisanextensiontoArmv8.2.Itaddsmandatoryandoptionalarchitecturalfeatures.Somefeat

- 【ARM Cortex-M 系列 2.3 -- Cortex-M7 Debug event 详细介绍】

主公讲 ARM

#ARM系列arm开发debugevent

请阅读【嵌入式开发学习必备专栏】文章目录Cortex-M7DebugeventDebugeventsCortex-M7Debugevent在ARMCortex-M7架构中,调试事件(DebugEvent)是由于调试原因而触发的事件。一个调试事件会导致以下几种情况之一发生:进入调试状态:如果启用了停滞调试(HaltingDebug),一个调试事件会使处理器在调试状态下停滞。通过将DHCSR.C_DE

- 基于STM32与Qt的自动平衡机器人:从控制到人机交互的的详细设计流程

极客小张

stm32qt机器人物联网人机交互毕业设计c语言

一、项目概述目标和用途本项目旨在开发一款基于STM32控制的自动平衡机器人,结合步进电机和陀螺仪传感器,实现对平衡机器人的精确控制。该机器人可以用于教育、科研、娱乐等多个领域,帮助用户了解自动控制、机器人运动学等相关知识。技术栈关键词STM32单片机步进电机陀螺仪传感器AD采集电路Qt人机界面实时数据监控二、系统架构系统架构设计本项目的系统架构设计包括以下主要组件:控制单元:STM32单片机传感器

- JAVA·一个简单的登录窗口

MortalTom

java开发语言学习

文章目录概要整体架构流程技术名词解释技术细节资源概要JavaSwing是Java基础类库的一部分,主要用于开发图形用户界面(GUI)程序整体架构流程新建项目,导入sql.jar包(链接放在了文末),编译项目并运行技术名词解释一、特点丰富的组件提供了多种可视化组件,如按钮(JButton)、文本框(JTextField)、标签(JLabel)、下拉列表(JComboBox)等,可以满足不同的界面设计

- ARMV8体系结构简介:概述

简单同学

ARMV8体系结构ARMV8

1.前言本文主要概括的介绍ARMV8体系结构定义了哪些内容,概括的说:ARM体系结构定义了PE的行为,不会定义具体的实现ARM体系结构也定义了debug体系结构和trace体系结构ARM体系结构采用RISC指令集(1)长度一致的寄存器;(2)load/store架构,数据处理操作只能对寄存器内容进行处理,不会直接对内存的内容进行处理;(3)简单寻址方式,load/store地址来源于寄存器或指令域

- Table列表复现框实现【勾选-搜索-再勾选】

~四时春~

java开发语言elementuivue

Table列表复现框实现【勾选-搜索-再勾选】概要整体架构流程代码实现技术细节注意参考文献概要最近在开发时遇到一个问题,在进行表单渲染时,正常选中没有问题,单如果需要搜索选中时,一个是已选中的不会回填,二是在搜索的结果中进行选中,没有实现,经过排查,查找资料后实现。例如:整体架构流程具体的实现效果如下:代码实现{{scope.row.userName}}已选区{{userItem.userName

- 深入浅出 -- 系统架构之负载均衡Nginx的性能优化

xiaoli8748_软件开发

系统架构系统架构负载均衡nginx

一、Nginx性能优化到这里文章的篇幅较长了,最后再来聊一下关于Nginx的性能优化,主要就简单说说收益最高的几个优化项,在这块就不再展开叙述了,毕竟影响性能都有多方面原因导致的,比如网络、服务器硬件、操作系统、后端服务、程序自身、数据库服务等,对于性能调优比较感兴趣的可以参考之前《JVM性能调优》中的调优思想。优化一:打开长连接配置通常Nginx作为代理服务,负责分发客户端的请求,那么建议开启H

- AI大模型的架构演进与最新发展

季风泯灭的季节

AI大模型应用技术二人工智能架构

随着深度学习的发展,AI大模型(LargeLanguageModels,LLMs)在自然语言处理、计算机视觉等领域取得了革命性的进展。本文将详细探讨AI大模型的架构演进,包括从Transformer的提出到GPT、BERT、T5等模型的历史演变,并探讨这些模型的技术细节及其在现代人工智能中的核心作用。一、基础模型介绍:Transformer的核心原理Transformer架构的背景在Transfo

- 6.0 践行打卡 D47

星月格格

去努力改变1.运动步行13000+8分钟腿部拉伸2.阅读《墨菲定律》第三章第三节:霍桑效应~适度发泄,才能轻装上阵“霍桑效应”这一概念,源自于1924年一个1933年间以哈佛大学心理专家乔治·埃尔顿·梅奥教授为首进行的一系列工厂工人的谈话实验研究。“霍桑效应”告诉我们,在工作,生活中总会产生数不清的情绪反应,其中很大一部分是负面的负面情绪的积累会影响人的精神和心情,不仅仅会影响个人健康,还会破坏人

- 信息系统安全相关概念(上)

YuanDaima2048

课程笔记基础概念安全信息安全笔记

文章总览:YuanDaiMa2048博客文章总览下篇:信息系统安全相关概念(下)信息系统安全相关概念[上]信息系统概述信息系统信息系统架构信息系统发展趋势:信息系统日趋大型化、复杂化信息系统面临的安全威胁信息系统安全架构设计--以云计算为例信息系统安全需求及安全策略自主访问控制策略DAC强制访问控制策略MAC信息系统概述信息系统用于收集、存储和处理数据以及传递信息、知识和数字产品的一组集成组件。几

- C++常见知识掌握

nfgo

c++开发语言

1.Linux软件开发、调试与维护内核与系统结构Linux内核是操作系统的核心,负责管理硬件资源,提供系统服务,它是系统软件与硬件之间的桥梁。主要组成部分包括:进程管理:内核通过调度器分配CPU时间给各个进程,实现进程的创建、调度、终止等操作。使用进程描述符(task_struct)来存储进程信息,包括状态(就绪、运行、阻塞等)、优先级、内存映射等。内存管理:包括物理内存和虚拟内存管理。通过页表映

- 程序员架构师主要是做什么_程序员架构师:职责、技能与挑战

绿色小猪

免费备考资料(2024年11月软考):历年试题+视频课合集+电子讲义点击领取>>>免费刷题:2024年11月软考备考刷题点此进入>>>程序员架构师的角色定位在软件开发领域,程序员架构师是一个至关重要的角色。他们不仅需要深入理解业务需求,还要将其转化为技术上的解决方案。程序员架构师是项目中的技术领航者,负责制定和维护软件系统的整体架构,确保系统的可扩展性、可维护性和性能。他们的工作涉及从概念化到实现

- metaRTC8.0,一个全新架构的webRTC SDK库

metaRTC

webrtc音视频

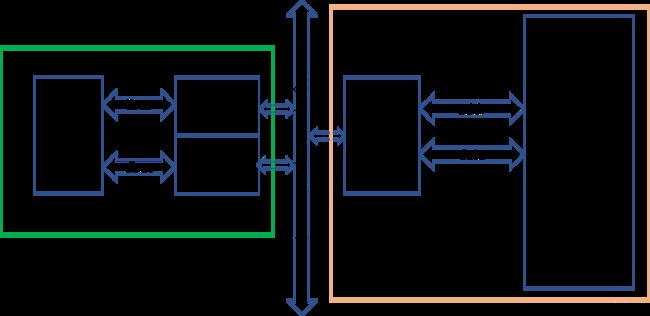

概述metaRTC8.0是metaRTC开源以来架构变化最大的一个版本,是metaIPC3.0等高性能的基础。metaRTC8.0是一个全新架构版本,并非在metaRTC7.0版本上简单升级,在QOS/语音对讲/内存占用/视频文件录制读取等方面新增多个模块,在弱网对抗/语音对讲/内存优化等效果上有显著提升。metaRTC8.0在一年多的开发中进行了近200次迭代,metaRTC8.0社区版计划在2

- 鲲鹏 ARM 架构 麒麟 Lylin v10 安装 Nginx (离线)

焚木灵

arm开发架构nginx服务器

最近做一个银行的项目,银行的服务器是鲲鹏ARM架构的服务器,并且是麒麟v10的系统,这里记录一下在无法访问外网安装Nginx的方法。其他文章:鲲鹏ARM架构麒麟Lylinv10安装Mysql8.3(离线)-CSDN博客鲲鹏ARM架构麒麟Lylinv10安装Node和NVM(离线)-CSDN博客鲲鹏ARM架构麒麟Lylinv10安装Pm2(离线)-CSDN博客鲲鹏ARM架构麒麟Lylinv10安装P

- Nginx的使用场景:构建高效、可扩展的Web架构

张某布响丸辣

nginx前端架构

Nginx,作为当今最流行的Web服务器和反向代理软件之一,凭借其高性能、稳定性和灵活性,在众多Web项目中扮演着核心角色。无论是个人博客、中小型网站,还是大型企业级应用,Nginx都能提供强大的支持。本文将探讨Nginx的几个主要使用场景,帮助读者理解如何在实际项目中充分利用Nginx的优势。1.静态文件服务对于包含大量静态文件(如HTML、CSS、JavaScript、图片等)的网站,Ngin

- Hadoop架构

henan程序媛

hadoop大数据分布式

一、案列分析1.1案例概述现在已经进入了大数据(BigData)时代,数以万计用户的互联网服务时时刻刻都在产生大量的交互,要处理的数据量实在是太大了,以传统的数据库技术等其他手段根本无法应对数据处理的实时性、有效性的需求。HDFS顺应时代出现,在解决大数据存储和计算方面有很多的优势。1.2案列前置知识点1.什么是大数据大数据是指无法在一定时间范围内用常规软件工具进行捕捉、管理和处理的大量数据集合,

- 稍微落后的人更容易被激励成长

有杕之杜

今日纯分享。图片发自App沃顿商学院市场营销学教授乔纳·伯杰在接受《哈佛商业评论》采访时,介绍了他的一项研究。伯杰教授告诉参加实验的人,他们在跟隔壁房间的另一个人比赛打字速度,获胜的人有金钱奖励。一轮比赛之后,伯杰给了这些人不同的反馈,有的人被告知远远落后竞争对手,有的人被告知稍稍落后,还有的人被告知不相上下或者略微领先。结果只有那些被告知“稍微落后”的人,在第二轮中速度明显提高,而且总体来说,这

- Web安全:Web体系架构存在的安全问题和解决方室

程序员-张师傅

前端安全web安全前端

Web体系架构在提供丰富功能和高效服务的同时,也面临着诸多安全问题。这些问题可能涉及数据泄露、服务中断、系统被控制等多个方面,对企业和个人造成不可估量的损失。以下是对Web体系架构中存在的安全问题及解决方案的详细分析:Web体系架构存在的安全问题注入攻击SQL注入:攻击者通过在输入字段中插入恶意SQL代码,操控后台数据库,窃取、篡改或删除数据。OS命令注入:攻击者通过输入字段插入恶意代码,执行系统

- Gobelieve 架构

weixin_34099526

数据库golangjson

Gobelievegithub地址声明:转简书JackieF的文章,为了自己方便copy了一份,加一些自己的东西.链接:https://www.jianshu.com/p/8121d6e85282IMCore主要分三大块:im客户连接服务器(可分布式部署,暂无负载均衡模块)imr路由查询服务器(主要解决im分布式部署的问题)ims存储服务器(主从部署)基础模块1.数据包协议包:header(12)

- Go 面向包的设计和架构分层

云满笔记

golang架构directorylayoutsrcproject

标题Go面向包的设计和架构分层序前项目架构分层工具包项目应用项目cmd/internal/internal/pkg/pkg/vendor/面向包的设计和验证包的位置依赖包导入应用级别的策略数据的发送和接收错误处理测试捕获错误不建议的目录结论Go面向包的设计和架构分层序本篇内容主要讲解golang项目的面向包设计准则和基础的架构分层。信息来自原文ArdanLabs:Package-Oriented-

- 操作系统基础

怡晗★

Linuxlinux

目录操作系统基础冯诺依曼体系结构介绍操作系统基本认知本篇文章是后面学习操作系统知识的基础操作系统基础冯诺依曼体系结构介绍冯诺依曼体系结构如下:在上图中「输入设备」和「输出设备」一般被称为计算机的外设,而「存储器」在冯诺依曼体系结构中表示「内存」输入设备一般包括:网卡、磁盘、键盘、触摸屏等输出设备一般包括:网卡、磁盘、鼠标、触摸屏、显示器(非触摸屏)等内存的作用「内存」是中央处理器与计算机其他设备的

- Go 语言基本架构

Fe_cow丿

Go

Go基本架构一、Go基本架构:packagemainimport"fmt"funcmain(){fmt.Println("hello,world")}go文件的后缀是.go;packagemain:表示文件所在的包是main;每个Go应用程序都包含一个为main的包;所有包名都应该使用小写字母;import“fmt”:表示引入一个包,包名为fmt,引入该包后,就可以使用fmt包的函数;比如:fmt

- 统一思想认识

永夜-极光

思想

1.统一思想认识的基础,才能有的放矢

原因:

总有一种描述事物的方式最贴近本质,最容易让人理解.

如何让教育更轻松,在于找到最适合学生的方式.

难点在于,如何模拟对方的思维基础选择合适的方式. &

- Joda Time使用笔记

bylijinnan

javajoda time

Joda Time的介绍可以参考这篇文章:

http://www.ibm.com/developerworks/cn/java/j-jodatime.html

工作中也常常用到Joda Time,为了避免每次使用都查API,记录一下常用的用法:

/**

* DateTime变化(增减)

*/

@Tes

- FileUtils API

eksliang

FileUtilsFileUtils API

转载请出自出处:http://eksliang.iteye.com/blog/2217374 一、概述

这是一个Java操作文件的常用库,是Apache对java的IO包的封装,这里面有两个非常核心的类FilenameUtils跟FileUtils,其中FilenameUtils是对文件名操作的封装;FileUtils是文件封装,开发中对文件的操作,几乎都可以在这个框架里面找到。 非常的好用。

- 各种新兴技术

不懂事的小屁孩

技术

1:gradle Gradle 是以 Groovy 语言为基础,面向Java应用为主。基于DSL(领域特定语言)语法的自动化构建工具。

现在构建系统常用到maven工具,现在有更容易上手的gradle,

搭建java环境:

http://www.ibm.com/developerworks/cn/opensource/os-cn-gradle/

搭建android环境:

http://m

- tomcat6的https双向认证

酷的飞上天空

tomcat6

1.生成服务器端证书

keytool -genkey -keyalg RSA -dname "cn=localhost,ou=sango,o=none,l=china,st=beijing,c=cn" -alias server -keypass password -keystore server.jks -storepass password -validity 36

- 托管虚拟桌面市场势不可挡

蓝儿唯美

用户还需要冗余的数据中心,dinCloud的高级副总裁兼首席营销官Ali Din指出。该公司转售一个MSP可以让用户登录并管理和提供服务的用于DaaS的云自动化控制台,提供服务或者MSP也可以自己来控制。

在某些情况下,MSP会在dinCloud的云服务上进行服务分层,如监控和补丁管理。

MSP的利润空间将根据其参与的程度而有所不同,Din说。

“我们有一些合作伙伴负责将我们推荐给客户作为个

- spring学习——xml文件的配置

a-john

spring

在Spring的学习中,对于其xml文件的配置是必不可少的。在Spring的多种装配Bean的方式中,采用XML配置也是最常见的。以下是一个简单的XML配置文件:

<?xml version="1.0" encoding="UTF-8"?>

<beans xmlns="http://www.springframework.or

- HDU 4342 History repeat itself 模拟

aijuans

模拟

来源:http://acm.hdu.edu.cn/showproblem.php?pid=4342

题意:首先让求第几个非平方数,然后求从1到该数之间的每个sqrt(i)的下取整的和。

思路:一个简单的模拟题目,但是由于数据范围大,需要用__int64。我们可以首先把平方数筛选出来,假如让求第n个非平方数的话,看n前面有多少个平方数,假设有x个,则第n个非平方数就是n+x。注意两种特殊情况,即

- java中最常用jar包的用途

asia007

java

java中最常用jar包的用途

jar包用途axis.jarSOAP引擎包commons-discovery-0.2.jar用来发现、查找和实现可插入式接口,提供一些一般类实例化、单件的生命周期管理的常用方法.jaxrpc.jarAxis运行所需要的组件包saaj.jar创建到端点的点到点连接的方法、创建并处理SOAP消息和附件的方法,以及接收和处理SOAP错误的方法. w

- ajax获取Struts框架中的json编码异常和Struts中的主控制器异常的解决办法

百合不是茶

jsjson编码返回异常

一:ajax获取自定义Struts框架中的json编码 出现以下 问题:

1,强制flush输出 json编码打印在首页

2, 不强制flush js会解析json 打印出来的是错误的jsp页面 却没有跳转到错误页面

3, ajax中的dataType的json 改为text 会

- JUnit使用的设计模式

bijian1013

java设计模式JUnit

JUnit源代码涉及使用了大量设计模式

1、模板方法模式(Template Method)

定义一个操作中的算法骨架,而将一些步骤延伸到子类中去,使得子类可以不改变一个算法的结构,即可重新定义该算法的某些特定步骤。这里需要复用的是算法的结构,也就是步骤,而步骤的实现可以在子类中完成。

- Linux常用命令(摘录)

sunjing

crondchkconfig

chkconfig --list 查看linux所有服务

chkconfig --add servicename 添加linux服务

netstat -apn | grep 8080 查看端口占用

env 查看所有环境变量

echo $JAVA_HOME 查看JAVA_HOME环境变量

安装编译器

yum install -y gcc

- 【Hadoop一】Hadoop伪集群环境搭建

bit1129

hadoop

结合网上多份文档,不断反复的修正hadoop启动和运行过程中出现的问题,终于把Hadoop2.5.2伪分布式安装起来,跑通了wordcount例子。Hadoop的安装复杂性的体现之一是,Hadoop的安装文档非常多,但是能一个文档走下来的少之又少,尤其是Hadoop不同版本的配置差异非常的大。Hadoop2.5.2于前两天发布,但是它的配置跟2.5.0,2.5.1没有分别。 &nb

- Anychart图表系列五之事件监听

白糖_

chart

创建图表事件监听非常简单:首先是通过addEventListener('监听类型',js监听方法)添加事件监听,然后在js监听方法中定义具体监听逻辑。

以钻取操作为例,当用户点击图表某一个point的时候弹出point的name和value,代码如下:

<script>

//创建AnyChart

var chart = new AnyChart();

//添加钻取操作&quo

- Web前端相关段子

braveCS

web前端

Web标准:结构、样式和行为分离

使用语义化标签

0)标签的语义:使用有良好语义的标签,能够很好地实现自我解释,方便搜索引擎理解网页结构,抓取重要内容。去样式后也会根据浏览器的默认样式很好的组织网页内容,具有很好的可读性,从而实现对特殊终端的兼容。

1)div和span是没有语义的:只是分别用作块级元素和行内元素的区域分隔符。当页面内标签无法满足设计需求时,才会适当添加div

- 编程之美-24点游戏

bylijinnan

编程之美

import java.util.ArrayList;

import java.util.Arrays;

import java.util.HashSet;

import java.util.List;

import java.util.Random;

import java.util.Set;

public class PointGame {

/**编程之美

- 主页面子页面传值总结

chengxuyuancsdn

总结

1、showModalDialog

returnValue是javascript中html的window对象的属性,目的是返回窗口值,当用window.showModalDialog函数打开一个IE的模式窗口时,用于返回窗口的值

主界面

var sonValue=window.showModalDialog("son.jsp");

子界面

window.retu

- [网络与经济]互联网+的含义

comsci

互联网+

互联网+后面是一个人的名字 = 网络控制系统

互联网+你的名字 = 网络个人数据库

每日提示:如果人觉得不舒服,千万不要外出到处走动,就呆在床上,玩玩手游,更不能够去开车,现在交通状况不

- oracle 创建视图 with check option

daizj

视图vieworalce

我们来看下面的例子:

create or replace view testview

as

select empno,ename from emp where ename like ‘M%’

with check option;

这里我们创建了一个视图,并使用了with check option来限制了视图。 然后我们来看一下视图包含的结果:

select * from testv

- ToastPlugin插件在cordova3.3下使用

dibov

Cordova

自己开发的Todos应用,想实现“

再按一次返回键退出程序 ”的功能,采用网上的ToastPlugins插件,发现代码或文章基本都是老版本,运行问题比较多。折腾了好久才弄好。下面吧基于cordova3.3下的ToastPlugins相关代码共享。

ToastPlugin.java

package&nbs

- C语言22个系统函数

dcj3sjt126com

cfunction

C语言系统函数一、数学函数下列函数存放在math.h头文件中Double floor(double num) 求出不大于num的最大数。Double fmod(x, y) 求整数x/y的余数。Double frexp(num, exp); double num; int *exp; 将num分为数字部分(尾数)x和 以2位的指数部分n,即num=x*2n,指数n存放在exp指向的变量中,返回x。D

- 开发一个类的流程

dcj3sjt126com

开发

本人近日根据自己的开发经验总结了一个类的开发流程。这个流程适用于单独开发的构件,并不适用于对一个项目中的系统对象开发。开发出的类可以存入私人类库,供以后复用。

以下是开发流程:

1. 明确类的功能,抽象出类的大概结构

2. 初步设想类的接口

3. 类名设计(驼峰式命名)

4. 属性设置(权限设置)

判断某些变量是否有必要作为成员属

- java 并发

shuizhaosi888

java 并发

能够写出高伸缩性的并发是一门艺术

在JAVA SE5中新增了3个包

java.util.concurrent

java.util.concurrent.atomic

java.util.concurrent.locks

在java的内存模型中,类的实例字段、静态字段和构成数组的对象元素都会被多个线程所共享,局部变量与方法参数都是线程私有的,不会被共享。

- Spring Security(11)——匿名认证

234390216

Spring SecurityROLE_ANNOYMOUS匿名

匿名认证

目录

1.1 配置

1.2 AuthenticationTrustResolver

对于匿名访问的用户,Spring Security支持为其建立一个匿名的AnonymousAuthenticat

- NODEJS项目实践0.2[ express,ajax通信...]

逐行分析JS源代码

Ajaxnodejsexpress

一、前言

通过上节学习,我们已经 ubuntu系统搭建了一个可以访问的nodejs系统,并做了nginx转发。本节原要做web端服务 及 mongodb的存取,但写着写着,web端就

- 在Struts2 的Action中怎样获取表单提交上来的多个checkbox的值

lhbthanks

javahtmlstrutscheckbox

第一种方法:获取结果String类型

在 Action 中获得的是一个 String 型数据,每一个被选中的 checkbox 的 value 被拼接在一起,每个值之间以逗号隔开(,)。

所以在 Action 中定义一个跟 checkbox 的 name 同名的属性来接收这些被选中的 checkbox 的 value 即可。

以下是实现的代码:

前台 HTML 代码:

- 003.Kafka基本概念

nweiren

hadoopkafka

Kafka基本概念:Topic、Partition、Message、Producer、Broker、Consumer。 Topic: 消息源(Message)的分类。 Partition: Topic物理上的分组,一

- Linux环境下安装JDK

roadrunners

jdklinux

1、准备工作

创建JDK的安装目录:

mkdir -p /usr/java/

下载JDK,找到适合自己系统的JDK版本进行下载:

http://www.oracle.com/technetwork/java/javase/downloads/index.html

把JDK安装包下载到/usr/java/目录,然后进行解压:

tar -zxvf jre-7

- Linux忘记root密码的解决思路

tomcat_oracle

linux

1:使用同版本的linux启动系统,chroot到忘记密码的根分区passwd改密码 2:grub启动菜单中加入init=/bin/bash进入系统,不过这时挂载的是只读分区。根据系统的分区情况进一步判断. 3: grub启动菜单中加入 single以单用户进入系统. 4:用以上方法mount到根分区把/etc/passwd中的root密码去除 例如: ro

- 跨浏览器 HTML5 postMessage 方法以及 message 事件模拟实现

xueyou

jsonpjquery框架UIhtml5

postMessage 是 HTML5 新方法,它可以实现跨域窗口之间通讯。到目前为止,只有 IE8+, Firefox 3, Opera 9, Chrome 3和 Safari 4 支持,而本篇文章主要讲述 postMessage 方法与 message 事件跨浏览器实现。postMessage 方法 JSONP 技术不一样,前者是前端擅长跨域文档数据即时通讯,后者擅长针对跨域服务端数据通讯,p