PCIe设备识别——LTSSM实验

一、LTSSM相关理论:

1.链路训练目标

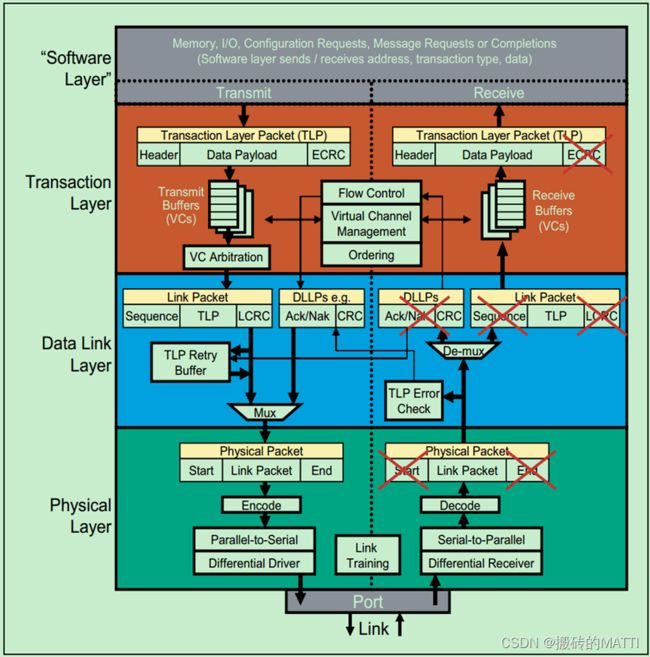

PCIe总线中的链路初始化与训练(Link Initialization & Training)是一种完全由硬件实现的功能,处于PCIe体系结构中的物理层。整个过程由链路训练状态机LTSSM(Link Training and Status State Machine)完成。

在系统复位后,会自动进行链路训练,以达成以下目标:位锁定(Bit Lock)、字符锁定(Symbol Lock,Gen1 & Gen2 Only)、块对齐(Block Alignment,Gen3 Only)、确定链路宽度(Link Width)、通道位置翻转(Lane Reversal)、信号极性翻转(Polarity Inversion)、确定链路的数据率(Data Rate)和通道对齐(Lane-to-Lane De-skew)等功能。

下面依次的,简要地介绍一下这些目标。

1.位锁定(Bit Lock)

位锁定是能够准确地识别出数据流中的0和1。接收端通过CDR(Clock and Data Recovery)逻辑将时钟从数据流中恢复出来,然后再用恢复出来的时钟对数据信号进行采样。一旦CDR完成了时钟的恢复,我们就说PCIe总线完成了位锁定。

2. 字符锁定(Symbol Lock)

对于Gen1&Gen2来说,采用的8b/10b编码,即传输的数据是以10bit为一个字符。LTSSM可以引导物理层相关逻辑通过识别COM(K28.5)等控制字符来确定每个字符的开始与结束为止,即字符锁定。

3. 块对齐(Block Alignment)

对于Gen3之后的来说,采用的是128b/130b编码。只用2bit作为sync header,标志一个block的开始。在Link training期间,接收端利用130bits的EIEOS来获取sync header的位置。即块对齐。

4. 链路宽度(Link Width):

链路训练与初始化过程中,相邻的两个PCIe设备需要相互通信来确定其支持的最大链路宽度。实际上PCIe Spec还允许采用动态带宽的机制,即允许链路宽度和数据率动态调整,以实现降低功耗等功能。

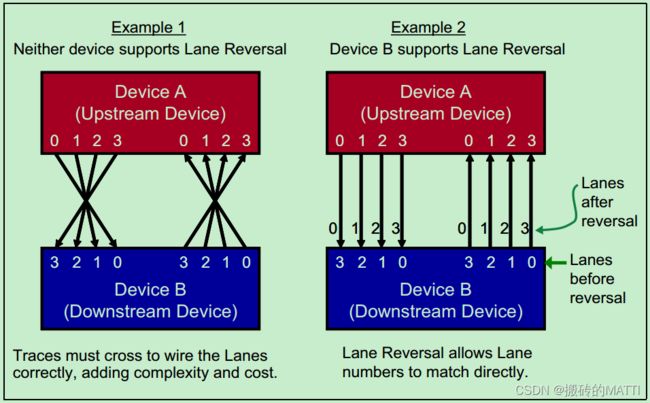

5. 通道位置翻转(Lane Reversal):

两个PCIe设备的通道排列位置可能不太一致,PCIe Spec允许对默认的通道排列位置重新排列,如下图所示。但是,从大部分的PCIe设备(PCIe卡和插槽等)都是按照统一的标准实现的,一般不会出现这种情况,因此这一功能是可选的。

6. 信号极性翻转(Polarity Inversion):

PCIe收发的都是差分信号,有的时候Link两端的设备的对应信号的极性可能是相反的。因此,PCIe Spec允许在链路训练与初始化的时候,对其进行调整。

7. 链路的数据率(Data Rate):

系统刚复位的时候,链路训练和初始化都是基于2.5G T/s的速率的。如果Link两端的设备都支持更高的速率,则会自动进入Re-training状态,以重新切换速率。

8. 通道对齐(Lane-to-Lane De-skew):

PCIe链路完成字符锁定或块对齐后,还需要进行通道对齐。因为有的通道的信号可能先到达,有的可能后到达。PCIe Spec规定PCIe链路应有能力对一定范围了的Lane-to-Lane Skew进行移除,使得各个Lane上的信号是同步的。

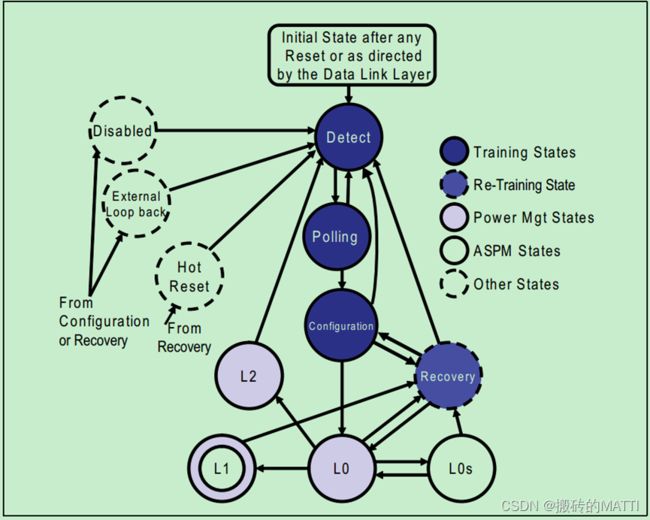

2、LTSSM

LTSSM有11个状态(其中又有多个子状态),分别是Detect、Polling、Configuration、Recovery,L0、L0s、L1、L2(L3是可选的)、Hot Reset、Loopback和Disable状态。系统进行复位操作(Cold, Hot or Warm Reset)后,会自动进入Detect状态。

这11个状态又可以被分为以下五个类别:

1、链路训练状态(Link Training State);

2、重训练状态(Re-Training(Recovery)State);

3、软件驱动功耗管理状态(Software Driven Power Management State);

4、活动状态功耗管理状态(Active-State Power Management State,ASPM State);

5、其他状态(Other State);

二、Xilinx PCIe设备识别实验

1.Pcie设备端

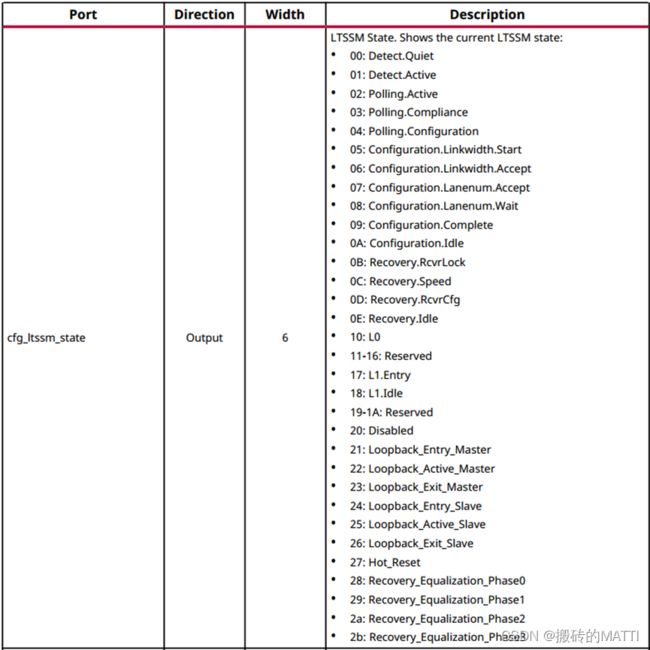

Pcie设备选用的是Xilinx的XDMA,XDMA内部封了xilinx PCIe的ip core,里面可以拉出LTSSM状态信号cfg_ltssm_state

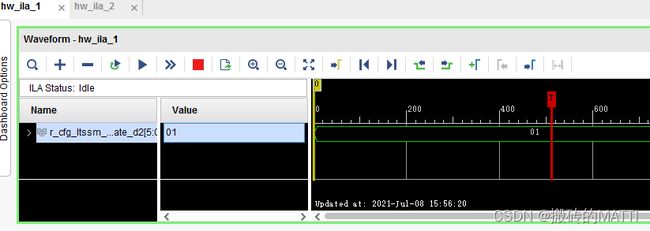

1.正常开机下到L0状态:

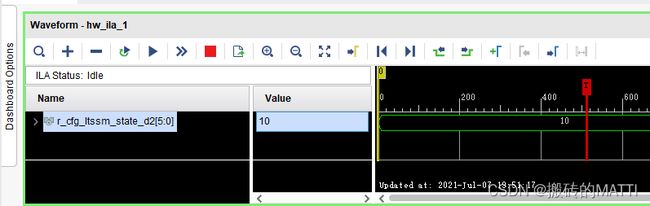

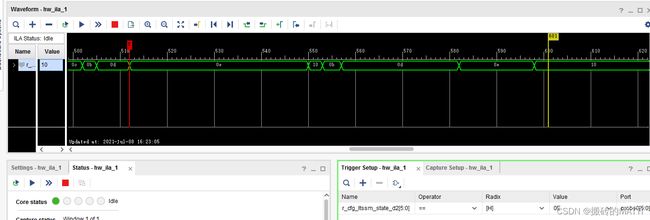

2.测试异常之后的LTSSM状态流转,设置触发信号,触发recover状态,进行异常测试:

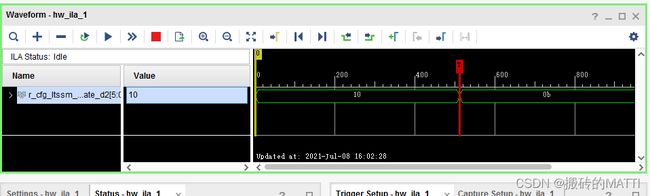

异常:

再次恢复,能正常跳转到LTSSM中L0状态

2.主机端

主机使用linux环境,系统为Fedora,设备上电之后在Terminal键入:

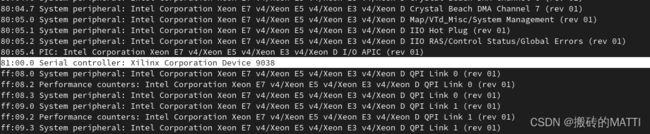

sudo lspci在list中查找到设备81:00:0 xilinx corporation device 9038

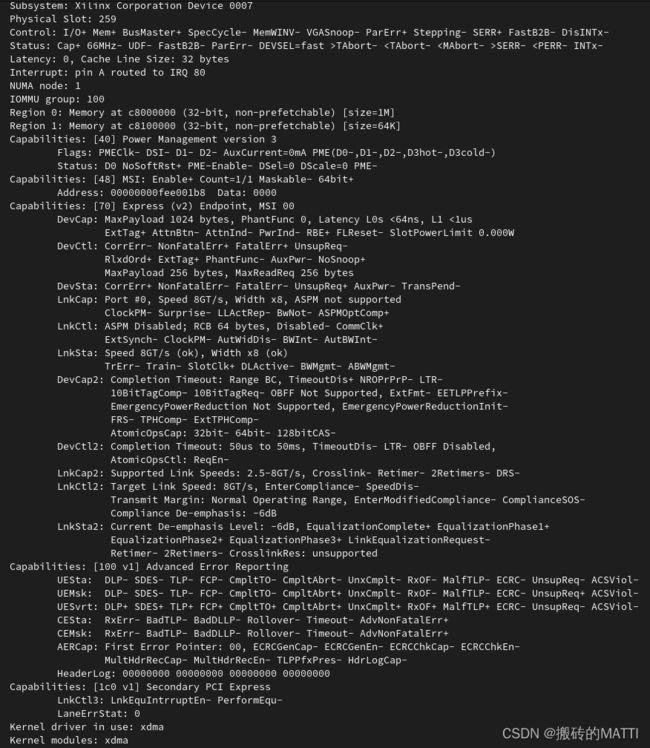

继续查看其详细信息

sudo lspci -vv -s 81:00:01. Region 0,这个是上面PCIe to AXI Lite Master Interface选择的空间。Region 1,这个是XDMA IP自身内部寄存器空间,不用关心。

2.DevCap里是设备能提供的MaxPayload size是1024字节;DevCtl里是系统最终协商的结果为MaxPayload size是256字节,MaxReadReq最大请求字节,协商后是256字节。

3. LnkCap字段,是设备能提供的PCIe链路状态,上面写的速度是8G,位宽是x8。LnkSta是最终协商的链路状态:PCIe IP上选择的是8G,位宽选择x8,这个目前协商到了。

参考:

1.PCIe PHY layer:Link training过程的LTSSM状态机跳转_maxwell2ic的博客-CSDN博客_pcie协商过程![]() https://blog.csdn.net/maxwell2ic/article/details/90759280

https://blog.csdn.net/maxwell2ic/article/details/90759280

2.

PCIe扫盲——链路初始化与训练基础(一)-Felix-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台![]() http://blog.chinaaet.com/justlxy/p/5100053531

http://blog.chinaaet.com/justlxy/p/5100053531

3.Xilinx PCIe IPcore手册 PG213

4.https://community.mellanox.com/s/article/understanding-pcie-configuration-for-maximum-performance![]() https://community.mellanox.com/s/article/understanding-pcie-configuration-for-maximum-performance

https://community.mellanox.com/s/article/understanding-pcie-configuration-for-maximum-performance

5.Xilinx PCIe XDMA使用指南1. 为什么使用PCIe传输 在FPGA需要和处理器打交道时,无论是X86,还是PowerPC,以![]() https://mp.weixin.qq.com/s/OODlnR49ycyguoqPj0WzZQ?st=1B2268519578E348054E218007CF2CADFE716368CDD5D8973C773B6A67AD968DBBBDB5754788CBC8D826ACC1C04DC08CC714BBAF4B9A5256BCCECFC3C009ADC14FBE89656819227E0F10ABC38BD1C74DF1532337672F45A3E632225DBAF692AD3A6E7F3DBE9D38A04AEEEF0C7A535A651284AAEFD6D64D861F7CC59AAB964C05F96C0417844F9F217B2523DF45D22825AA11451641E64F0C7D9B53C448DE8CC0E4E115FA664FE58DEBC01A0725B08B7E47942BE60B973724A8D7F4A09589B5A27FCBBDE9816A74764B75FAAF9F768F91&vid=1688852780257427&cst=9FD455B1329D217CA045EF768B669F3EFCB148833657951B5135B9CDBFF8E73F755ED90B46A12DBCD50667DE5C2D6E44&deviceid=83e48417-c232-40a2-8014-8974137e35ca&version=4.0.3.6007&platform=win

https://mp.weixin.qq.com/s/OODlnR49ycyguoqPj0WzZQ?st=1B2268519578E348054E218007CF2CADFE716368CDD5D8973C773B6A67AD968DBBBDB5754788CBC8D826ACC1C04DC08CC714BBAF4B9A5256BCCECFC3C009ADC14FBE89656819227E0F10ABC38BD1C74DF1532337672F45A3E632225DBAF692AD3A6E7F3DBE9D38A04AEEEF0C7A535A651284AAEFD6D64D861F7CC59AAB964C05F96C0417844F9F217B2523DF45D22825AA11451641E64F0C7D9B53C448DE8CC0E4E115FA664FE58DEBC01A0725B08B7E47942BE60B973724A8D7F4A09589B5A27FCBBDE9816A74764B75FAAF9F768F91&vid=1688852780257427&cst=9FD455B1329D217CA045EF768B669F3EFCB148833657951B5135B9CDBFF8E73F755ED90B46A12DBCD50667DE5C2D6E44&deviceid=83e48417-c232-40a2-8014-8974137e35ca&version=4.0.3.6007&platform=win