实验二 多路复用器的实现-数字电路与逻辑设计-湖南大学课程实验

因为CSDN传文档内的大量图片排版太麻烦了,所以直接上整个文档导出图,随便吧,反正只是备份存个档,也没什么人看。

下面是没有图片的文字部分,只是方便索引,没有排版

实验二 多路复用器的实现

班级 姓名 学号

一、实验目的

1.熟悉多路复用器、加法器的工作原理。

2.学会使用VHDL 语言设计多路复用器、加法器。

3.掌握generic 的使用,设计n-1 多路复用器。

4.兼顾速度与成本,设计行波加法器和先行进位加法器。

二、实验内容

1、利用VHDL语言设计一个8重3-1多路复用器,实现3个八位向量输入,选择一个输出的功能。

2、利用VHDL语言,使用generic设计n-1多路复用器并调用它定制为8-1多路复用器.

3、了解4位行波加法器、4位先行进位加法器的原理并设计VHDL程序。查看并分析其原理图,最后进行仿真验证。

三、实验方法

1、 实验方法

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是Quartus II。

2、 实验步骤

1、 新建,编写源代码。

(1).选择保存项和芯片类型:【File】-【new project wizard】-【next】(设置文件路径,在本次实验中,我将四个实验项目分别设置三个project name为MUX3_1、N_1MUX、ADDER和PREADD)-【next】(add添加文件,三个实验项目分别设置文件名MUX3_1.vhd、N_1MUX.vhd、ADDER.vhd和PREADD.vhd)-【properties】(检查文件类型type=VHDL)-【next】(三个项目都统一选择芯片类型family=Cyclone;name= EP1C3T100A8)-【next】-【finish】

(2).新建:【file】-【new】(选择VHDL File)-【OK】

2、写好源代码,保存文件(分别为MUX3_1.vhd、N_1MUX.vhd、ADDER.vhd和PREADD.vhd)。

3、编译与调试。确定源代码文件为当前工程文件,点击【processing】-【start compilation】进行文件编译,编译成功。

4、波形仿真及验证(包括功能仿真和时序仿真)。

新建一个vector waveform file。通过操作:右击 -【insert】-【insert node or bus】-【node finder】(pins=all;【list】)-【>>】-【ok】-【ok】。接着设置输入波形,然后点击【start simulation】开始仿真,查看时序仿真输出波形图。

在【assignments】-【setting】-【simulator settings】-【simulation mode】中,将timing修改为functional,然后再点击【processing】- 【Generate Functional Simulation Netlist】成功后点击【start simulation】开始仿真,查看输出功能仿真波形图。

5、时序分析:选择【start classic timing analyzer】-在compilation report中选择【timing analysis】-【tpd】(查看引脚到引脚的延时)

6、查看RTL Viewer:【Tools】-【netlist viewer】-【RTL viewer】。

四、实验过程

(一)8重3-1多路复用器

1、 编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

编译报告,资源消耗如下:

警告信息共一条:

c) RTL视图

d)结果分析及结论

程序正常通过编译,出现一则警告,提示“定义的管脚没有和外部的管脚连接”。因为本次实验并没有在实体芯片上运行,所以暂时可以不做处理,往下几个实验的警告相同,所以不再赘述。

2、 波形仿真

a) 波形仿真过程:插入S、I0、I1、I2和Y五个节点(S、I0、I1、I2为输入节点,Y为输出节点),设置输入波形,点击为S设置计时器信号,从00开始;设置I0为固定输入01010101,I1为固定输入11001101,I2为固定输入00110110,保存并对应仿真。

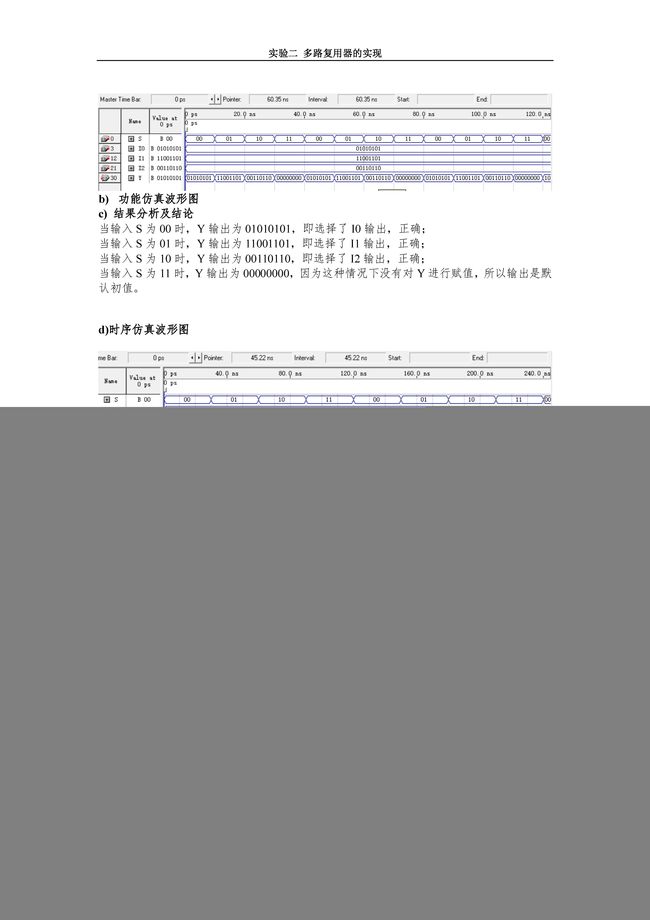

b) 功能仿真波形图

c) 结果分析及结论

当输入S为00时,Y输出为01010101,即选择了I0输出,正确;

当输入S为01时,Y输出为11001101,即选择了I1输出,正确;

当输入S为10时,Y输出为00110110,即选择了I2输出,正确;

当输入S为11时,Y输出为00000000,因为这种情况下没有对Y进行赋值,所以输出是默认初值。

d)时序仿真波形图

e)结果分析及结论

可以看出每次输入信号S变换后,输出有约15ns的延迟,且输出信号作出反应时产生了在短时间内的信号波动,其余表现同功能仿真.

3.时序分析

a)时序分析图

b)结果分析及结论

S[0]引脚到Y[0]引脚的实际p2p时间最长,为15.902ns,I0[7]引脚到Y[7]引脚的实际p2p时间最短,为9.617ns。

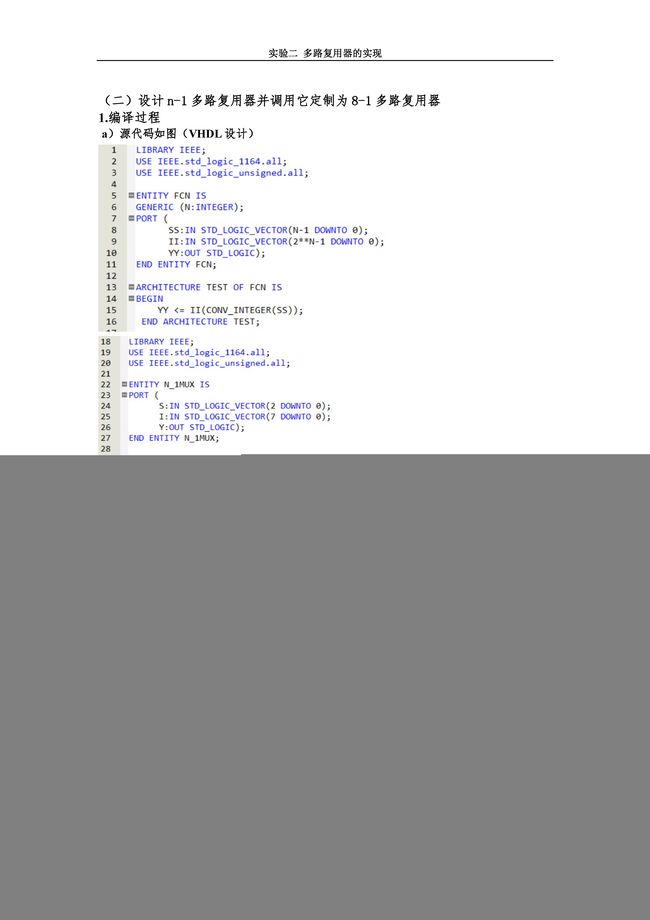

(二)设计n-1多路复用器并调用它定制为8-1多路复用器

1.编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

编译报告,资源消耗如下:

c) RTL视图

d)结果分析及结论

程序正常通过编译,我通过调用函数以行为描述的方式的设计,从RTL电路原理图看出实际实现的电路模块为选择器。

3、 波形仿真

a) 波形仿真过程:插入S,I,Y三个信号(S、I为输入节点,Y为输出节点),设置输入波形,点击为S设置三位计时器信号从000开始,设置I[7~0]为固定输入01011001,保存并对应仿真。

b) 功能仿真波形图

c) 结果分析及结论

自输入S从000到111,应当分别选择I的第0到7位输出看到输出波形随着S输入信号的变换依次为10011010,正确。

d)时序仿真波形图

e)结果分析及结论

可以看出,时序仿真每次输入时变化,输出在延迟13秒左右作出反应,且在部分输入变化时存在冒险;将输入改成按照格雷码进行变换时,输出的冒险很好地消除了(见下图)。

3.时序分析

a)时序分析图

b)结果分析及结论

S[1]引脚到Y引脚的实际p2p时间为14.796ns ,是所有引脚间tpd最长的,S[2]引脚到Y引脚的实际p2p时间为12.205ns,时延最短。

(三)行波进位加法器

1.编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

编译报告,资源消耗如下:

c) RTL视图

d)结果分析及结论

程序正常通过编译,我采用分层设计方式进行结构描述,利用半加器、全加器,组合成四位行波加法器。

4、 波形仿真

a) 波形仿真过程:插入A、B、C0、S、C4五个节点(A、B、C0为输入节点,其余为输出节点),设置输入波形,点击为A设置四位计时器信号,从0000开始,点击为B设置四位计时器信号,从0010开始,C0设置为时钟信号,周期160ns,相位差0,保存并进行对应仿真。

b)功能仿真波形图与分析

观察到080ns,在进位输入为0时,输出的是A+B的结果,如4050ns,A输入0100,B输入0110,输出S为1010且输出进位为0,正确;

但结果存在溢出时,进位输入为1,如70~80ns,A输入0111,B输入1001,计算结果溢出,输出S为0000且输出进位为1表示溢出,正确;

b) 时序仿真波形图及分析

可以观察到每次输入变化都会有将近12ns的延迟以及几ns的输出跳动,在部分时候,如60ns处的输入变化所对应的输出甚至发生了溢出位的跳动。

3.时序分析

a)时序分析图

(如右图所示)

b)结果分析及结论

可以看到最长的延迟为引脚C[0]到S[3]的,为15.467ns。

(四)四位先行进位加法器

1.编译过程

a)源代码如图(VHDL设计)

b)编译、调试过程

编译报告,资源消耗如下:

c) RTL视图

d)结果分析及结论

程序正常通过编译,我采用数据流描述进行设计,利用逻辑门直接计算得出各位的进位输入,得到四位先行进位加法器。

5、 波形仿真

c) 波形仿真过程:插入A、B、C0、S、C4五个节点(A、B、C0为输入节点,其余为输出节点),设置输入波形,点击为A设置四位计时器信号,从0000开始,点击为B设置四位计时器信号,从0010开始,C0设置为时钟信号,周期160ns,相位差0,保存并进行对应仿真。

b)仿真波形图与分析

波形仿真效果与先行进位加法器类似,这里不再过多说明

3.时序分析

a)时序分析图

b)结果分析及结论

可以看到最长的延迟为引脚A[0]到C4的,为16.977ns。

对比行波进位加法器,延迟反而更大,可能是与芯片性能并不理想,电路并没有更好地优化有关。

五、实验结论

通过此次试验,我对多路复用器、加法器的工作原理的了解更加深刻。同时也了解generic 的使用。在实验过程中也与老师探讨了n-1多路复用器的其他实现方法,给了我很多启发。