- 【vivado】debug相关时钟及其约束关系

liuchj04

XilinxSoCFPGAfpga开发

一、前言在xilinxfpga的degug过程中,经常出现由于时钟不对而导致的观测波形失败,要想能够解决这些问题需要了解其debug的组成环境以及之间的数据流。本文主要介绍debug过程中需要的时钟及各时钟之间的关系。二、debug相关时钟Vivado硬件管理器使用JTAG接口与VivadoDebug内核进行通信,DebugHub在FPGA器件的JTAG边界扫描(BSCAN)接口和VivadoDe

- 听说Zynq-手把手教你自定义ip核并调用

不只会拍照的程序猿

听说ZYNQ嵌入式eclipseubuntufpgaverilog

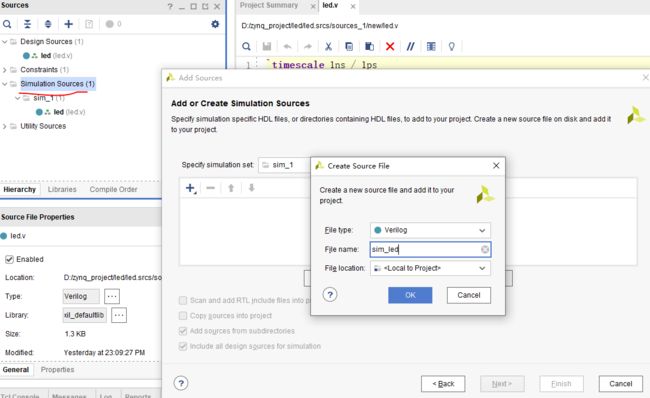

概述小编最近在研究Zynq,因为对其相对陌生,在探索过程中也遇到了不少坑,这里将如何创建IP核并调用的方法步骤总结记录,以免日后忘记。注意★环境:Vivado2018.2。开发板:digilent(迪芝伦)公司的ZYBO创建IP核创建工程1.打开vivado软件,选择CreateProject创建项目。2.输入工程名和路径,勾选createprojectsubdirectory,为你自动在目录下创

- Vivado 约束文件XDC使用经验总结

宁静致远dream

FPGA不积跬步

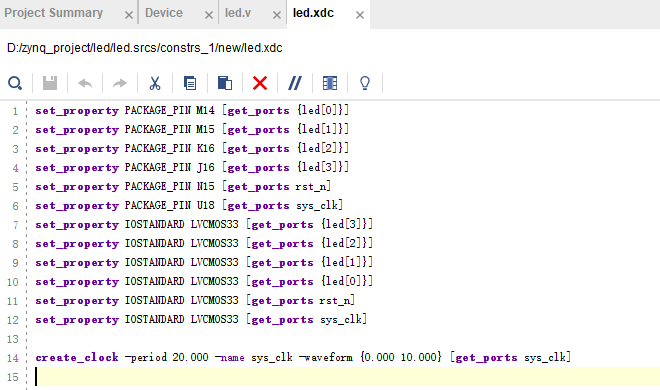

1.1Vivado约束文件XDC使用经验总结1.1.1本节目录1)本节目录;2)本节引言;3)FPGA简介;4)Vivado约束文件XDC使用经验总结;5)结束语。1.1.2本节引言“不积跬步,无以至千里;不积小流,无以成江海。就是说:不积累一步半步的行程,就没有办法达到千里之远;不积累细小的流水,就没有办法汇成江河大海。1.1.3FPGA简介FPGA(FieldProgrammableGateA

- Linux下VCS与Verdi联合仿真(Verilog与VHDL混仿)

超能力MAX

fpga开发

1.介绍本篇简单介绍一下如何通过VCS与Verdi实现混合仿真,在学习过程中也遇到了很多头疼的问题,因此通过一些例子简要总结一下,当然,也希望对各位小伙伴有所帮助。很多公司ASIC设计所使用的还是更加专业的EDA软件,即Synopsys下的VCS、Verdi这种(Vivado大多针对于自家FPGA),VCS编译速度极快,仿真效率高,Verdi支持信号追溯、无缝增加信号波形等功能。2.使用环境:Li

- 实时系统vxWorks - zynq7020移植vxWorks

不只会拍照的程序猿

实时vxWorks听说ZYNQ嵌入式vxWorksZynq实时系统操作系统

概述关于zynq的启动方式,网上百度有一大堆,这里就不详细阐述了,小编整理了一下主要流程大致为:上电->bootRom->FSBL->操作系统。BootRom:硬件固化,用户无需更改,类似bios。FSBL(BOOT.bin):由fsbl.elf、bitstream和SSBL三部分组成。fsbl.elf用于完成PS初始化工作,加载PLbitstream文件,运行SSBL(bootrom)。操作系统

- vivado实现FFT和IFFT信号处理

寒听雪落

信号处理_通信原理FPGA专栏_verilog信号处理算法

一,FFT的物理意义FFT是离散傅立叶变换的快速算法,可以将一个信号变换到频域。有些信号在时域上是很难看出什么特征的,但是如果变换到频域之后,就很容易看出特征了。这就是很多信号分析采用FFT变换的原因。另外在频谱分析方面,FFT可以将一个信号的频谱提取出来。一个模拟信号,经过ADC采样(采样频率要大于信号频率的两倍)之后,就变成了数字信号。采样得到的数字信号,就可以做FFT变换了。N个采样点,经过

- petalinux-build ERROR

Ret0

嵌入式硬件

最近编译Xilinx的固件的时候报了一个错,看的我云里雾里,一度认为ubuntu的版本跟petalinux的版本不匹配,想要重新安装操作系统和编译环境,想想都头大。petalinux-create-tproject--templatezynqMP-npetalinux-config--get-hw-description=./petalinux-build第二条命令导入的zu11eg的hdf然后就

- Tria Technologies RFSoC 平台 - 入门指南

东枫科技

USRPfpga开发5G

TriaTechnologiesRFSoC平台-入门指南适用于RFSoCGen-3的宽带毫米波无线电开发平台该平台将Otava和Avnet联合开发的OtavaDTRX2双收发器毫米波无线电卡与AMDXilinxZynq®UltraScale+™RFSoCZCU208评估套件相结合。5G毫米波相控阵天线模块开发平台该平台使开发人员能够使用AMDZynq®UltraScale+™RFSoCGen3

- 基于zynq的千兆网udp项目_一种基于ZYNQ的四路万兆以太网安全交换机的制作方法...

weixin_39534149

基于zynq的千兆网udp项目

本实用新型涉及网络安全、网络通信技术领域,尤其是一种基于ZYNQ的四路万兆以太网安全交换机,适用于大中型企业的交换网络。背景技术:随着互联网的高速发展,传统的以太网交换机在功能和性能上已不能满足要求,而大容量、高性能、高安全等以太网交换机的需求日益增长,以太网交换机朝着高速化方向发展。作为衡量网络性能的重要标准之一,速率是以太网交换机等设备发展的重要方向。为满足用户快速增长的需求,以太网速率从最初

- 时钟结构设计

cckkppll

fpga开发

时钟结构设计现在已经清楚地说明时钟决策的主要考虑因素,下面将介绍如何为设计提供需要的时钟。推断无需用户干预,Vivado综合工具就可以自动为所有时钟结构设定全局缓存(BUFG),直到架构允许的最大数量(除非用综合工具另行设定或加以控制)。如前文所述,BUFG能够提供满足大多数时钟需求的、受控良好的低偏差网络。除非器件上的BUFG数量或功能无法满足设计的时钟要求,无需另行干预。但是如果对时钟结构施加

- zynq 编译过程

法号:行颠

Linuxlinux

zynq编译过程zynq编译过程配置硬件生成BOOT.BIN生成boot.scr设备树文件编译内核设备树配置内核编译编译根文件系统配置编译在`SD`卡上生成根文件系统制作SD启动卡参考文档zynq编译过程最近在做zynq的驱动开发,学习了一下zynq的编译过程。在petalinux工程中进行配置硬件sptl//设置petalinux工作环境petalinux-create-tproject--te

- Zynq UltraScale+ MPSoC 在linux系统运行R5 裸机程序 remoteproc - R5

愧莫佳话

linuxarm

参考文章:ultrascale学习笔记之remoteproc启动R5ZYNQUltraScale+MPSoCLinux+ThreadXAMP玩法ZynqUltraScale+MPSoC包含Cortex™-A53处理器和Cortex™-R5实时处理单元。移植完Linux系统,在系统上同时运行A53和R5应用程序,重点是修改R5程序的起始地址。vitis创建A53应用程序可以参考之前的文章R5程序可以

- 常用软件安装包

sinat_39901027

edaic

Vivadovivado2022.2链接:https://pan.baidu.com/s/1ddVXKjxPZ5OL4gPSKMzwLg提取码:wmwkvivado2021.2链接:链接:https://pan.baidu.com/s/1EcrkcZzTe6v9LRnc5Fp0bg提取码:9tf8vivado2020.3链接:https://pan.baidu.com/s/1gFcHPX1cOnj

- vivado CLOCK_DELAY_GROUP、CLOCK_LOW_FANOUT

cckkppll

fpga开发

CLOCK_DELAY_GROUPLAY_GROUP属性标识具有相同MMCM的相关时钟,PLL、GT源或公共驱动器,应在放置和布线过程中进行平衡减少时钟之间的定时路径上的时钟偏斜。提示:时钟匹配(通过Clock_DELAY_GROUP属性)用于相同的MMCM、PLL或GT源。体系结构支持UltraScale、UltraScale+和VersalACAP体系结构。适用对象•直接连接到全局时钟输出的时

- FPGA实现光纤通信(3)——光纤8b/10b编码数据回环

得之坦然,失之淡然。

FPGA学习笔记fpga开发开源

前言光纤通信属于高速串行通信,具有较高的数据传输速率,通常用于服务器以及通信设备之间用于高速数据交换,对于xilinx7系列的FPGA,内部具有集成的高速接口用于实现光纤通信。本次就来实现8b/10b编码数据回环。测试环境:vivado版本:2020.02FPGA芯片:XC7K70T测试说明:进行光纤8B/10B编码数据回环测试8B/10B编码简介8b/10b编码是由IBM公司的Widmer和Fr

- FPGA入门学习之Vivado-数码管驱动设计实验

ZdqDeveloper

fpga开发学习FPGA

在本篇文章中,我们将介绍如何使用Vivado软件进行FPGA的数码管驱动设计实验。数码管是一种常见的输出设备,用于显示数字或字符等信息。通过本实验,您将学习如何使用FPGA来控制数码管的显示,并编写相应的Verilog代码。实验准备:Vivado软件的安装和配置。FPGA开发板(如Xilinx的Basys3)。实验步骤:步骤1:创建新工程打开Vivado软件,并选择"CreateProject"来

- 《基于FPGA的Cortex-M3软核基本SOC设计及外设开发详解》

HWxuYnO

fpga开发程序人生

基于FPGA的Cortex-M3软核基本SOC设计实现基于FPGA的Cortex-M3软核基本SOC,系统外设包括GPIO和UART串口。开发基于vivado2019.2和vitis,理论上可适用于任何版本的vivado,并且附带本人编写的详细开发文档,能够快速完成工程的移植。在该工程基础上可进一步开发更多的功能。ID:42100675319624107小小读者ok基于FPGA的Cortex-M3

- ZYNQ + Linux

jerwey

linuxzynq

ZYNQLinux操作系统移植说明文档http://xilinx.eetrend.com/content/2019/100018437.html1,组成ZYNQ上面移植Linux操作系统包括四个部分,uboot,devicetree,kernel,ramdisk.其中uboot类似于bios,负责对设备进行简单的初始化,devicetree以树的形式对zynq相连的硬件设备进行描述,kernel是

- ZYNQ&FPGA 时钟IP核(MMCM PLL)实验

Nadukab

fpgaverilog嵌入式

时钟资源简介:7系列的FPGA使用了专用的全局(Global)和区域(Regional)时钟资源来管理和设计不同的时钟需求。ClockManagementTiles(CMT)提供了时钟合成(Clockfrequencysynthesis),倾斜矫正(deskew),过滤抖动(jitterfiltering)功能。一个CMT包括一个MMCM和一个PLL。7系列FPGA高层次时钟结构视图:ClockR

- FPGA 时钟树缓存布局布线

cckkppll

fpga开发

时钟树缓存布局布线在以下阶段,Vivado布局器确定MMCM/PLL,全局时钟缓存和时钟根的位置,同时遵守物理XDC约束:1.I/O和时钟布局布局器根据连接规则和用户约束布局I/O缓存和MMCM/PLL。布局器将时钟缓存分配给时钟区域,但不分配给单个site位置,除非使用LOC属性进行约束。只有仅驱动非时钟负载的时钟缓存可以基于它们的驱动器和负载的布局移动到该流程中稍后的不同时钟区域。在此阶段的任

- vivado生成ltx文件命令_实验室自研工具Vivado Batch Mode Tool介绍!

电动星球蟹老板

vivado生成ltx文件命令

这里从两个方面分别进行说明,为什么要使用Vivado的Batchmode。1、流程操作效率我所谓的流程操作效率,是指在使用Vivado时,通过键盘输入、鼠标点击以及进行等待等实际外部操作的效率。例如我需要打开一个Vivado工程,并进行Synthesis,那么在GUI下是这样的流程操作:点击打开VivadoGUI并等待----用Vivado点击打开对应的.xpr文件并等待----点击runSynt

- Verilog中阻塞赋值和非阻塞赋值的区别?

张小侃

数字IC知识fpga硬件

阻塞赋值“=”对应组合逻辑电路赋值(无存储功能,立即赋值),并且会阻塞后面的赋值操作,非阻塞赋值“<=”对应时序逻辑电路赋值(有存储功能),所有非阻塞赋值操作在同一时刻进行赋值。下面分别通过vivado综合不同情况赋值的代码。第一种:在时序逻辑电路中使用阻塞赋值,通过综合后的电路可以看出非阻塞赋值综合出来的电路时立即执行赋值操作,和组合逻辑电路特性一致,无缓存功能,out_o直接被优化掉了。alw

- 搭建 RUST 交叉编译环境

法号:行颠

Linuxrustrust开发语言后端

在嵌入式`Linux`上运行`RUST`在嵌入式`Linux`上运行`RUST`构造交叉编译的`RUST`环境编译代码其他参考文档在嵌入式Linux上运行RUST最近在开发zynq相关的产品,想使用rust来开发应用程序;所以研究了一下如何在pc上进行rust的交叉编译。本人用的是zynq的7035芯片,里面包含两个cortex-A7的处理器。$cat/proc/cpuinfoprocessor:

- xilinx vivado PULLMODE 设置思路

坚持每天写程序

fpga开发

1.xilinx引脚分类XilinxIO的分类:以XC7A100TFGG484为例,其引脚分类如下:1.UserIO(用户IO):用户使用的普通IO1.1专用(Dedicated)IO:命名为IO_LXXY_#、IO_XX_#的引脚,有固定的特定用途,多为底层特定功能的直接实现,如差分对信号、关键控制信号等,不能随意变更。1.2多功能(Multi-Function)IO:命名为IO_LXXY_ZZ

- FPGA随记——赛灵思OOC功能

一口一口吃成大V

FPGA随记fpga开发

在这里,我们简要介绍一下Vivado的OOC(Out-of-Context)综合的概念。对于顶层设计,Vivado使用自顶向下的全局(Global)综合方式,将顶层之下的所有逻辑模块都进行综合,但是设置为OOC方式的模块除外,它们独立于顶层设计而单独综合。通常,在整个设计周期中,顶层设计会被多次修改并综合。但有些子模块在创建完毕之后不会因为顶层设计的修改而被修改,如IP,它们被设置为OOC综合方式

- 零配置初始化流程就一直过不去_ZYNQ UltraScale+ MPSoc FPGA自学笔记-启动加载配置...

weixin_40009026

零配置初始化流程就一直过不去

前言听说最近秋天的第一杯奶茶挺火的,我得赶紧奋发图强写点东西,好赚点赏钱给妹子买奶茶,各位大佬出手大方点,我怕秋天过去了妹子还没喝上奶茶!言归正传,ZYNQUltraScale+MPSoc的配置过程还是挺复杂的,决定写一篇文章来讲一讲,当然我也是初学,如有错讹请轻轻打左脸。一、配置过程Zynq®UltraScale+™MPSoC同时有PS端和PL端,PS又有两种不同的多核处理器可以运行底层代码或者

- zynq usb dwc3中断事件异常

charschu

linux-usb驱动开发

最近在调试zynq的usb,发现一个问题,给pcbulk传输吐log,传输速率1MB左右速率发包,发现会传输终止,调用epsend接口会失败原因在于没有收到传输完成事件,收到连续2次notready事件,这种情况usbbusy标志没有清除,结果send会进入updatethansfer分支指令,但是此时usbhardware已经释放了sourceindex,会挂死掉这里,这样说明硬件已经发送了完成

- PetaLinux开发流程

非鱼知乐

1.Createanewprojectpetalinux-create-tproject--templatezynq-n$(project_name)orpetalinux-create-tproject-s$(bsp_file)2.Importhardwareinformationpetalinux-config--get-hw-description=$(path_to_hdf)The.hdf

- ZYNQ MPSOC FPGA 仿真 教程

行者..................

fpga开发FPGA

1.**FPGA与MPSOC**:FPGA(FieldProgrammableGateArray)是一种可以通过编程配置的集成电路,适用于各种应用和功能。MPSOC(Multi-ProcessorSystemonChip)是集成了多个处理器(通常是微处理器)的系统芯片,用于处理复杂的应用,如图像处理、网络通信等。2.**仿真与分析**:-**仿真波形图**:在进行硬件设计时,仿真波形图是用来验证电

- zybo上运行linux,Zybo开发板linux作业系统移植

周行文

zybo上运行linux

文章主要介紹zyboboard上linux作业系统移植过程。分别介绍了开发环境搭建、U-boot编译、linux内核编译、busybox制作等流程及注意事项。文章使用的开发板是zynq7000系列的zyboboard。Vivado版本是2015.1.主机系统是Debian9.1.开发环境搭建工欲善其事必先利其器,做开发前搭建好编译环境是重要的一步,这些步骤大体上都相同,然而对于不同的系统平台、硬件

- 深入浅出Java Annotation(元注解和自定义注解)

Josh_Persistence

Java Annotation元注解自定义注解

一、基本概述

Annontation是Java5开始引入的新特征。中文名称一般叫注解。它提供了一种安全的类似注释的机制,用来将任何的信息或元数据(metadata)与程序元素(类、方法、成员变量等)进行关联。

更通俗的意思是为程序的元素(类、方法、成员变量)加上更直观更明了的说明,这些说明信息是与程序的业务逻辑无关,并且是供指定的工具或

- mysql优化特定类型的查询

annan211

java工作mysql

本节所介绍的查询优化的技巧都是和特定版本相关的,所以对于未来mysql的版本未必适用。

1 优化count查询

对于count这个函数的网上的大部分资料都是错误的或者是理解的都是一知半解的。在做优化之前我们先来看看

真正的count()函数的作用到底是什么。

count()是一个特殊的函数,有两种非常不同的作用,他可以统计某个列值的数量,也可以统计行数。

在统

- MAC下安装多版本JDK和切换几种方式

棋子chessman

jdk

环境:

MAC AIR,OS X 10.10,64位

历史:

过去 Mac 上的 Java 都是由 Apple 自己提供,只支持到 Java 6,并且OS X 10.7 开始系统并不自带(而是可选安装)(原自带的是1.6)。

后来 Apple 加入 OpenJDK 继续支持 Java 6,而 Java 7 将由 Oracle 负责提供。

在终端中输入jav

- javaScript (1)

Array_06

JavaScriptjava浏览器

JavaScript

1、运算符

运算符就是完成操作的一系列符号,它有七类: 赋值运算符(=,+=,-=,*=,/=,%=,<<=,>>=,|=,&=)、算术运算符(+,-,*,/,++,--,%)、比较运算符(>,<,<=,>=,==,===,!=,!==)、逻辑运算符(||,&&,!)、条件运算(?:)、位

- 国内顶级代码分享网站

袁潇含

javajdkoracle.netPHP

现在国内很多开源网站感觉都是为了利益而做的

当然利益是肯定的,否则谁也不会免费的去做网站

&

- Elasticsearch、MongoDB和Hadoop比较

随意而生

mongodbhadoop搜索引擎

IT界在过去几年中出现了一个有趣的现象。很多新的技术出现并立即拥抱了“大数据”。稍微老一点的技术也会将大数据添进自己的特性,避免落大部队太远,我们看到了不同技术之间的边际的模糊化。假如你有诸如Elasticsearch或者Solr这样的搜索引擎,它们存储着JSON文档,MongoDB存着JSON文档,或者一堆JSON文档存放在一个Hadoop集群的HDFS中。你可以使用这三种配

- mac os 系统科研软件总结

张亚雄

mac os

1.1 Microsoft Office for Mac 2011

大客户版,自行搜索。

1.2 Latex (MacTex):

系统环境:https://tug.org/mactex/

&nb

- Maven实战(四)生命周期

AdyZhang

maven

1. 三套生命周期 Maven拥有三套相互独立的生命周期,它们分别为clean,default和site。 每个生命周期包含一些阶段,这些阶段是有顺序的,并且后面的阶段依赖于前面的阶段,用户和Maven最直接的交互方式就是调用这些生命周期阶段。 以clean生命周期为例,它包含的阶段有pre-clean, clean 和 post

- Linux下Jenkins迁移

aijuans

Jenkins

1. 将Jenkins程序目录copy过去 源程序在/export/data/tomcatRoot/ofctest-jenkins.jd.com下面 tar -cvzf jenkins.tar.gz ofctest-jenkins.jd.com &

- request.getInputStream()只能获取一次的问题

ayaoxinchao

requestInputstream

问题:在使用HTTP协议实现应用间接口通信时,服务端读取客户端请求过来的数据,会用到request.getInputStream(),第一次读取的时候可以读取到数据,但是接下来的读取操作都读取不到数据

原因: 1. 一个InputStream对象在被读取完成后,将无法被再次读取,始终返回-1; 2. InputStream并没有实现reset方法(可以重

- 数据库SQL优化大总结之 百万级数据库优化方案

BigBird2012

SQL优化

网上关于SQL优化的教程很多,但是比较杂乱。近日有空整理了一下,写出来跟大家分享一下,其中有错误和不足的地方,还请大家纠正补充。

这篇文章我花费了大量的时间查找资料、修改、排版,希望大家阅读之后,感觉好的话推荐给更多的人,让更多的人看到、纠正以及补充。

1.对查询进行优化,要尽量避免全表扫描,首先应考虑在 where 及 order by 涉及的列上建立索引。

2.应尽量避免在 where

- jsonObject的使用

bijian1013

javajson

在项目中难免会用java处理json格式的数据,因此封装了一个JSONUtil工具类。

JSONUtil.java

package com.bijian.json.study;

import java.util.ArrayList;

import java.util.Date;

import java.util.HashMap;

- [Zookeeper学习笔记之六]Zookeeper源代码分析之Zookeeper.WatchRegistration

bit1129

zookeeper

Zookeeper类是Zookeeper提供给用户访问Zookeeper service的主要API,它包含了如下几个内部类

首先分析它的内部类,从WatchRegistration开始,为指定的znode path注册一个Watcher,

/**

* Register a watcher for a particular p

- 【Scala十三】Scala核心七:部分应用函数

bit1129

scala

何为部分应用函数?

Partially applied function: A function that’s used in an expression and that misses some of its arguments.For instance, if function f has type Int => Int => Int, then f and f(1) are p

- Tomcat Error listenerStart 终极大法

ronin47

tomcat

Tomcat报的错太含糊了,什么错都没报出来,只提示了Error listenerStart。为了调试,我们要获得更详细的日志。可以在WEB-INF/classes目录下新建一个文件叫logging.properties,内容如下

Java代码

handlers = org.apache.juli.FileHandler, java.util.logging.ConsoleHa

- 不用加减符号实现加减法

BrokenDreams

实现

今天有群友发了一个问题,要求不用加减符号(包括负号)来实现加减法。

分析一下,先看最简单的情况,假设1+1,按二进制算的话结果是10,可以看到从右往左的第一位变为0,第二位由于进位变为1。

- 读《研磨设计模式》-代码笔记-状态模式-State

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

/*

当一个对象的内在状态改变时允许改变其行为,这个对象看起来像是改变了其类

状态模式主要解决的是当控制一个对象状态的条件表达式过于复杂时的情况

把状态的判断逻辑转移到表示不同状态的一系列类中,可以把复杂的判断逻辑简化

如果在

- CUDA程序block和thread超出硬件允许值时的异常

cherishLC

CUDA

调用CUDA的核函数时指定block 和 thread大小,该大小可以是dim3类型的(三维数组),只用一维时可以是usigned int型的。

以下程序验证了当block或thread大小超出硬件允许值时会产生异常!!!GPU根本不会执行运算!!!

所以验证结果的正确性很重要!!!

在VS中创建CUDA项目会有一个模板,里面有更详细的状态验证。

以下程序在K5000GPU上跑的。

- 诡异的超长时间GC问题定位

chenchao051

jvmcmsGChbaseswap

HBase的GC策略采用PawNew+CMS, 这是大众化的配置,ParNew经常会出现停顿时间特别长的情况,有时候甚至长到令人发指的地步,例如请看如下日志:

2012-10-17T05:54:54.293+0800: 739594.224: [GC 739606.508: [ParNew: 996800K->110720K(996800K), 178.8826900 secs] 3700

- maven环境快速搭建

daizj

安装mavne环境配置

一 下载maven

安装maven之前,要先安装jdk及配置JAVA_HOME环境变量。这个安装和配置java环境不用多说。

maven下载地址:http://maven.apache.org/download.html,目前最新的是这个apache-maven-3.2.5-bin.zip,然后解压在任意位置,最好地址中不要带中文字符,这个做java 的都知道,地址中出现中文会出现很多

- PHP网站安全,避免PHP网站受到攻击的方法

dcj3sjt126com

PHP

对于PHP网站安全主要存在这样几种攻击方式:1、命令注入(Command Injection)2、eval注入(Eval Injection)3、客户端脚本攻击(Script Insertion)4、跨网站脚本攻击(Cross Site Scripting, XSS)5、SQL注入攻击(SQL injection)6、跨网站请求伪造攻击(Cross Site Request Forgerie

- yii中给CGridView设置默认的排序根据时间倒序的方法

dcj3sjt126com

GridView

public function searchWithRelated() {

$criteria = new CDbCriteria;

$criteria->together = true; //without th

- Java集合对象和数组对象的转换

dyy_gusi

java集合

在开发中,我们经常需要将集合对象(List,Set)转换为数组对象,或者将数组对象转换为集合对象。Java提供了相互转换的工具,但是我们使用的时候需要注意,不能乱用滥用。

1、数组对象转换为集合对象

最暴力的方式是new一个集合对象,然后遍历数组,依次将数组中的元素放入到新的集合中,但是这样做显然过

- nginx同一主机部署多个应用

geeksun

nginx

近日有一需求,需要在一台主机上用nginx部署2个php应用,分别是wordpress和wiki,探索了半天,终于部署好了,下面把过程记录下来。

1. 在nginx下创建vhosts目录,用以放置vhost文件。

mkdir vhosts

2. 修改nginx.conf的配置, 在http节点增加下面内容设置,用来包含vhosts里的配置文件

#

- ubuntu添加admin权限的用户账号

hongtoushizi

ubuntuuseradd

ubuntu创建账号的方式通常用到两种:useradd 和adduser . 本人尝试了useradd方法,步骤如下:

1:useradd

使用useradd时,如果后面不加任何参数的话,如:sudo useradd sysadm 创建出来的用户将是默认的三无用户:无home directory ,无密码,无系统shell。

顾应该如下操作:

- 第五章 常用Lua开发库2-JSON库、编码转换、字符串处理

jinnianshilongnian

nginxlua

JSON库

在进行数据传输时JSON格式目前应用广泛,因此从Lua对象与JSON字符串之间相互转换是一个非常常见的功能;目前Lua也有几个JSON库,本人用过cjson、dkjson。其中cjson的语法严格(比如unicode \u0020\u7eaf),要求符合规范否则会解析失败(如\u002),而dkjson相对宽松,当然也可以通过修改cjson的源码来完成

- Spring定时器配置的两种实现方式OpenSymphony Quartz和java Timer详解

yaerfeng1989

timerquartz定时器

原创整理不易,转载请注明出处:Spring定时器配置的两种实现方式OpenSymphony Quartz和java Timer详解

代码下载地址:http://www.zuidaima.com/share/1772648445103104.htm

有两种流行Spring定时器配置:Java的Timer类和OpenSymphony的Quartz。

1.Java Timer定时

首先继承jav

- Linux下df与du两个命令的差别?

pda158

linux

一、df显示文件系统的使用情况,与du比較,就是更全盘化。 最经常使用的就是 df -T,显示文件系统的使用情况并显示文件系统的类型。 举比例如以下: [root@localhost ~]# df -T Filesystem Type &n

- [转]SQLite的工具类 ---- 通过反射把Cursor封装到VO对象

ctfzh

VOandroidsqlite反射Cursor

在写DAO层时,觉得从Cursor里一个一个的取出字段值再装到VO(值对象)里太麻烦了,就写了一个工具类,用到了反射,可以把查询记录的值装到对应的VO里,也可以生成该VO的List。

使用时需要注意:

考虑到Android的性能问题,VO没有使用Setter和Getter,而是直接用public的属性。

表中的字段名需要和VO的属性名一样,要是不一样就得在查询的SQL中

- 该学习笔记用到的Employee表

vipbooks

oraclesql工作

这是我在学习Oracle是用到的Employee表,在该笔记中用到的就是这张表,大家可以用它来学习和练习。

drop table Employee;

-- 员工信息表

create table Employee(

-- 员工编号

EmpNo number(3) primary key,

-- 姓