什么是IO Pad?

1.什么是IO pad?

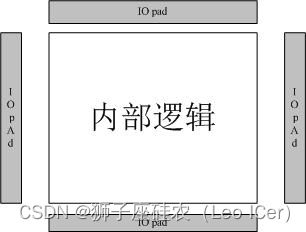

IO pad是一个芯片管脚处理模块,即可以将芯片管脚的信号经过处理送给芯片内部,又可以将芯片内部输出的信号经过处理送到芯片管脚。输入信号处理包含时钟信号,复位信号等,输出信号包含观察时钟、中断等。IO pad模块可以控制输入输出信号的电平、驱动电流等,同时还包含了检测功能。

IO pad 具有不同的类型,对应不同的信号需要不同的IO pad模块,常见的信号类型有:

输入差分时钟信号,复位信号,正常数据信号、

输出观察时钟信号、JTAG接口信号、正常输出信号

IO pad模块一般具有两种模式:有些类型的IO pad支持两种模式,有些只支持一个模式。

接收模式,也可以成为输入模式:

芯片管脚信号作为输入进入IO PAD模块,驱动输出信号送给芯片内部逻辑。

驱动模式,可以称为输出模式:

芯片内部逻辑的输出信号作为IO的输入,驱动输出信号送给芯片管脚。

2.IO Pad类型有哪些?

2.1.输入差分时钟 AC-Coupled

芯片管脚差分时钟输入,分别为clk_n和clk_p, 经过pad后输出为单根芯片内部使用的时钟。

2.2.芯片复位信号RST

芯片管脚输入复位信号,通过IO pad模块后作为输入送给芯片内部模块。一般只有一个方向,从芯片管脚输入复位信号,输出信号给芯片内部逻辑。

2.3.JTAG接口

用于DFT(Design fortest )的JTAG接口,这些信号包含了TRST_L, TMS,TCK, TDI, TDO, ATPG_MODE_L, and PAD_TRI_L。此类IO pad模块两种模式:输入模式和输出模式。根据配置信号可以设置成接收模式和驱动模式。

2.4.正常数据输出:TRAN类型

此类IO引脚最为常见,包含:中断输出信号、状态观察输出信号(PCIE link信号、led状态、部分时钟)、调试debug信号。

此类IO可以配置成接收模式和驱动模式。

并且在接收模式时:需要考虑是否使用弱上拉和弱下拉功能。

驱动模式时:不使用弱上拉和弱下拉功能

2.5.Clkobs

观察芯片内部的各类时钟,各类时钟通过mux输出一个clk,通过clkobs pad输出

2.6.温度监控

用于测裸片温度

3.IO pad功能

3.1.tran类型输入输出

TRAN是最常用的IO PAD类型,常用于各类数据(不包含其他类型)的输入输出。

输入模式(三种):不用上拉下拉、带上拉、带下拉

输出模式: 就一种,不带上下拉

X的连接:输入接0,输出悬空

输入上拉:输入信号signal_in连接pad,RCV_DATA为输出信号

当输入信号低电平有效时,采用上拉电阻,此时默认状态为高,若signal_in由1跳变为0,则驱动接收信号RCV_DATA为0;若采用下拉电阻,则当signal_in没有连接pad时,RCV_DATA为0,电路功能出错。