FPGA系列:ZCU102开发板上的第一个工程(MIG控制器)

该工程是XILINX官网上提供的一个例程。刚拿到ZCU102时没有拿到资源,自行在官网上查找有关资料进行学习,发现官网有提供例程便从这里开始熟悉我的新板子。

XILINX官网:Xilinx -灵活应变. 万物智能.

FPGA上电后IO的默认状态 | 电子创新网赛灵思社区

Vivado之时序约束XDC-kevinc-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台

一、软硬件准备

ZCU102开发板,需要连接电源和右上角的JTAG。

进入官网搜索XCU102,可以检索到XCU102有关的原理图、数据手册和例程等。我们找到XTP432-ZCU102 MIG Tutorial(v11.0),下载官网提供的教程和源代码。MIG控制器可以实现对DDR地址空间的读写。

二、创建工程

1、工程名:zcu102_mig

2、Project Type:RTL Project,勾选Do not specify sources at this time

3、Default Part:Board——ZCU102 Evaluation Board

4、Finish成功创建空白工程

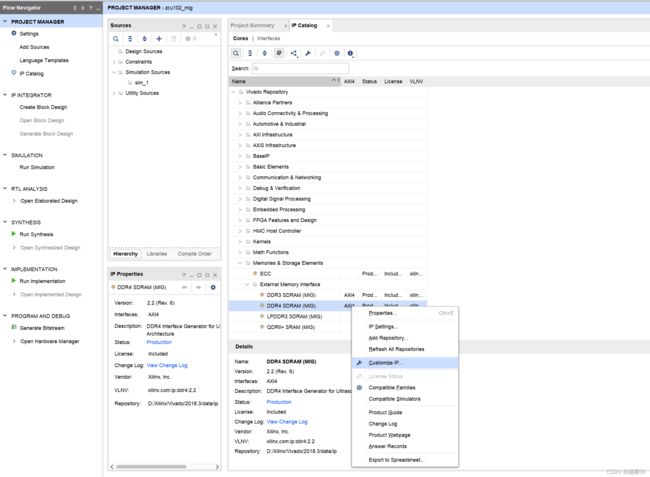

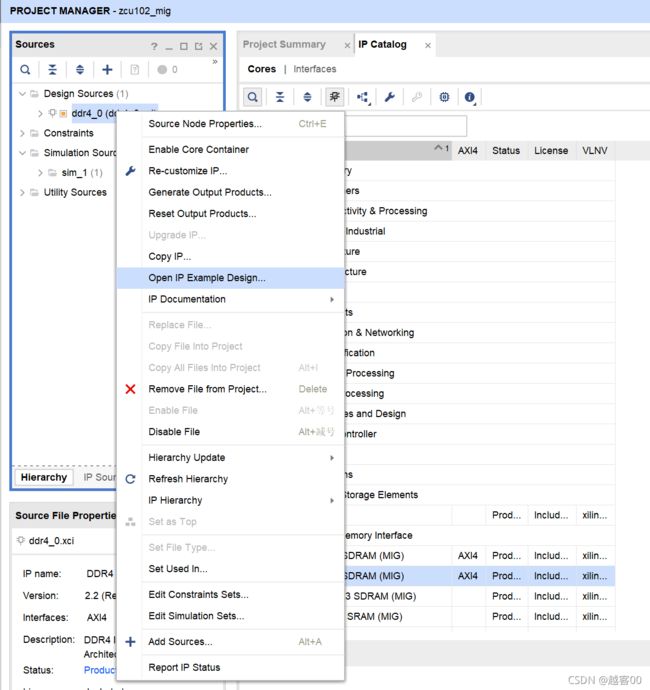

5、创建完工程后我们按照教程指引创建并配置MIG控制器。点击IP Catalog——Memories & Storage Elements——External Memery Interface——DDR4 SRAM(MIG),右键选择Customize IP进入IP编辑页面。

Board:

Set C0_SYS_CLK to user si570 sysclk

Set C0_DDR4 to ddr4 sdram

Set SYSTEM_RESET to Custom

Basic:

The Memory Device Interface Speed is preset to 833 ps

The Reference Input Clock Speed is preset to 3332 ps

The Memory Part is preset to MT40A256M16GE-075E

The Data Width is preset to 16

Advanced Options:

Set the Debug Signals to Enable

Example Design TestBench 选择Advanced TG

点击OK,Generate自动生成IP。等待IP自检完成。

回头找到我们从官网下载的源码,解压rdf0381-zcu102-mig-c-2019-1.zip,打开ddr4_0_ex文件夹会发现里面只有一个imports文件夹,复制里面的约束文件example_design.xdc、顶层文件example_top.sv、LED驱动文件led_display_driver.v到创建的IP工程ddr4_0_ex里的imports文件夹,替换相同的文件。回到VIVADO的ddr4_0_ex工程,重载工程文件并添加复制的RTL文件、约束文件到工程。

回头找到我们从官网下载的源码,解压rdf0381-zcu102-mig-c-2019-1.zip,打开ddr4_0_ex文件夹会发现里面只有一个imports文件夹,复制里面的约束文件example_design.xdc、顶层文件example_top.sv、LED驱动文件led_display_driver.v到创建的IP工程ddr4_0_ex里的imports文件夹,替换相同的文件。回到VIVADO的ddr4_0_ex工程,重载工程文件并添加复制的RTL文件、约束文件到工程。

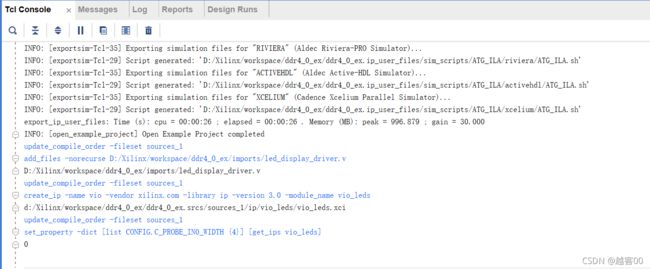

在TCL控制台输入代码添加LED驱动文件并创建VIO IP:

add_files -norecurse C:/zcu102_mig/ddr4_0_ex/imports/led_display_driver.v

create_ip -name vio -vendor xilinx.com -library ip -version 3.0 -module_name vio_leds

set_property -dict [list CONFIG.C_PROBE_IN0_WIDTH {4}] [get_ips vio_leds]

第一行代码中的路径需要替换成led_display_driver.v存放路径。

第一行代码中的路径需要替换成led_display_driver.v存放路径。

三、运行和调试

在VIVADO中生成比特流并加载到ZCU102开发板中,LED0和LED3常亮,LED1闪烁。实验成功。

四、结果分析

做实验还是要回到学习和分析方面来的,我们做这个实验的目的一是熟悉VIVADO软件,其次就是学习ZCU102的使用。

首先我们来学习原理图。打开约束文件,以led[3]为例,确定led[3]对应的引脚为 AJ14。打开ZCU102的原理图搜索,对应的BANK44包含一系列LED和开关SW,在约束文件中进行约束可以调用。

set_property PACKAGE_PIN AJ14 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property SLEW SLOW [get_ports {led[3]}]

最后一行代码是笔者感到陌生的,通过搜索相关资料我们可以知道在Xilinx的设计环境中,可以将输出信号的Slew rate设置成FAST或SLOW。当设置成FAST时,提高了信号变化的斜率,从而提高了信号的转换速率,但同时使脉冲信号的振铃增大。因此,除非万不得已,不要将输出信号的Slew rate设成FAST。